Логическая матрица на основе мемристорной коммутационной ячейки

Иллюстрации

Показать всеИзобретение относится к области микро- и наноэлектроники на основе перспективных материалов и устройств и направлено на создание устройства с высокой степенью интеграции элементов, выполняющего логические операции и содержащего матрицу высокоскоростных переключателей на основе электрически перепрограммируемых ячеек. Технический результат заключается в возможности перепрограммируемой коммутации, которая подходит для построения логики работы нейроморфного устройства и снижения энергопотребления. Это достигается путем использования в качестве переключающихся элементов мемристоров, обладающих небольшим размером и высокой скоростью переключения, и адресных низковольтных МОП транзисторов, включенных комплементарно. Разделение цепей записи и считывания позволяет осуществлять многократное программирование логического устройства. Наличие в ячейке адресных транзисторов позволяет минимизировать токи утечки и взаимовлияние ячеек при их объединении в матрицу, что уменьшает энергопотребление. 4 ил.

Реферат

Изобретение относится к области микро- и наноэлектроники на основе перспективных материалов и устройств и может быть использовано для построения надежных сверхбольших логических матриц с энергонезависимой памятью, высокой степенью интеграции элементов, малым энергопотреблением и высоким быстродействием.

Известно устройство логической матрицы, созданной на основе коммутационной ячейки, в которую включены полевой транзистор с плавающим затвором (размером 10 F2) и двумя высоковольтными транзисторами (более 10 F2) в качестве программирующих элементов (US №8120955 В2, Feb. 21, 2012). Устройство обладает рядом недостатков в случае применения сверхбольших логических матриц (например, в нейропроцессорах со сложной архитектурой). Это малая степень интеграции из-за больших размеров элементов и, как следствие, ограниченное число логических вентилей и типовых схем на их основе; высокое энергопотребление в процессе записи и при невысоком быстродействии из-за медленного накопления заряда в плавающем затворе; ограниченные возможности при программировании и обучении.

Известны коммутационные ячейки на мемристорных элементах в чипах памяти. В одном варианте ячейки (Negrov D. V., Kirtaev R. V., Kiseleva I. V. et. al. Integration of Functional Elements of Resistive Nonvolative Memory with 1T-1R Topology / Russian Microelectronics. 2016. Vol. 45, No. 6. Pp. 383-395) используется один адресный n-МОП транзистор. В двух других вариантах ячейки (Liu T., Yan Т.Н., Scheuerlein R. A 130.7-mm 2-Layer 32-Gb ReRAM Memory Device in 24-nm Technology / IEEE Journal of solid-state circuits. 2013. V. 49. No. 1. Pp. 140-149; Chevallier C.J., Siau C.H., Lim S.F., Namala S.R. et.al. A 0.13 μm 64Mb multi-layered conductive metal-oxide memory / IEEE International Solid-state circuits conference. 2010. Pp. 260-261) применяется диод в качестве селектора для исключения тока утечки через соседние элементы.

Общим недостатком таких схем является возможность пропускать ток через мемристор только в одном направлении, что не позволяет осуществить перепрограммирование.

Предложены программируемые логические устройства, в которых могут быть использованы мемристорные коммутационные ячейки (Yang J.J., Strukov D.B., Stewart D.R. Memristive devices for computing / Nature Nanotechnology. 2013. No. 8. Pp. 13-24). В этих устройствах мемристорный кроссбар расположен под углом над CMOS вентилями. Организация ячеек в кроссбар обеспечивает большую плотность элементов, но обладает существенным недостатком в виде взаимовлияния включенных ячеек. Из-за этого организация больших кроссбаров невозможна. Для исключения этого эффекта последовательно мемристору включен селективный элемент (диод или n-МОП транзистор), пропускающий ток только в одном направлении. В свою очередь, такое решение исключает возможность перепрограммирования мемристоров.

Кроме этого, проводники, соединяющие мемристор с логическими элементами, могут оказаться очень длинными из-за повернутого кроссбара, т.е. будут обладать большим сопротивлением, что может привести к неправильной работе устройства.

Задачей, которую решает изобретение, является обеспечение устойчивой работы сверхбольшой коммутационной матрицы на основе мемристорных переключателей в программируемом логическом устройстве.

Техническим результатом является высокая степень интеграции элементов, малое энергопотребление и высокое быстродействие устройства.

Это достигается путем использования в качестве переключающихся элементов мемристоров, обладающих небольшим размером (1 F2) и высокой скоростью переключения (менее 30 нс), и адресных низковольтных МОП транзисторов (4 F2), включенных комплементарно. Разделение цепей записи и считывания позволяет осуществлять многократное программирование логического устройства. Наличие в ячейке адресных транзисторов позволяет минимизировать токи утечки и взаимовлияние ячеек при их объединении в матрицу, что уменьшает энергопотребление.

Сущность изобретения поясняется фиг. 1 - 4.

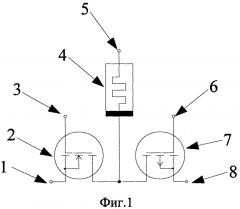

На фиг. 1 показана электрическая схема коммутационной ячейки, которая представляет собой соединение транзисторной КМОП структуры и одного мемристора, где 1 - шина питания Vss, 2 - n-МОП транзистор, 3 - затвор n-МОП транзистора (Xn1), 4 - мемристор, 5 - второй контакт мемристора (Y1), 6 - затвор р-МОП транзистора (Xp1), 7- р-МОП транзистор, 8 - шина питания Vdd.

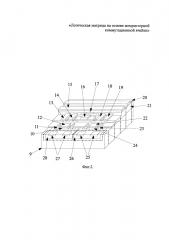

На фиг. 2 представлены топологические приемы построения фрагмента логической матрицы, состоящего, например, из 5 коммутационных ячеек, где 9 - подложка, 10 - изолятор, 11 - соединительный проводник, 12 - затвор n-МОП транзистора, 13 - шина питания Vss, 14 - шина управления затворами n-МОП транзисторов (Xn1), 15 - выход матрицы (шина Y1), 16 - соединительный проводник, 17 - область переключения, 18 - шина управления затворами р-МОП транзисторов (Xp1), 19 - шина питания Vdd, 20 - мемристивный слой (переключающийся материал), 21 - изолятор, 22 - затвор р-МОП транзистора, 23 - соединительный проводник, 24 - изолятор, 25 - полупроводник р-типа (исток и сток р-МОП транзистора), 26 - полупроводник n-типа (колодец для р-МОП транзистора), 27 - полупроводник n-типа (исток и сток n-МОП транзистора), 28 - полупроводник р-типа (колодец для n-МОП транзистора).

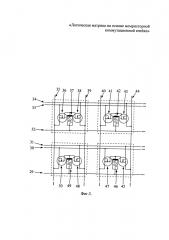

На фиг. 3 приведен способ организации коммутационных ячеек в логическую матрицу, реализующую конъюнкции, а с помощью инверторов и дизъюнкции, где 29 - выход логической матрицы (Q1)/ шина программирования первой строки, 30 - шина питания Vss, 31 - шина питания Vdd, 32 - выход логической матрицы (Q2)/ шина программирования второй строки, 33 - шина питания Vss, 34 - шина питания Vdd, 35 - вход логической матрицы X1, 36 - n-МОП транзистор, 37 - мемристор, 38 - р-МОП транзистор, 39 - вход логической матрицы не-Х1, 40 - вход логической матрицы Х2, 41 - n-МОП транзистор, 42 - мемристор, 43 - р-МОП транзистор, 44 - вход логической матрицы не-Х2, 45 - р-МОП транзистор, 46 - мемристор, 47 - n-МОП транзистор, 48 - р-МОП транзистор, 49 - мемристор, 50 - n-МОП транзистор.

На фиг. 4. представлены эпюры напряжений при записи 51 и считывании 52 на выходе матриц, состоящих из одной и четырех ячеек соответственно.

Рассмотрим работу устройства (фиг. 3).

В электрической схеме коммутационной ячейки, приведенной на фиг. 1, выполнены соединения следующим образом: мемристор 4 первым контактом подключен к соединению стоков n- и р-канальных транзисторов (2 и 7), которые переключают этот контакт между полюсами источника питания 1 и 8. Затворы транзисторов (3 и 6) являются входами, предназначенными для ввода переменных в логическую матрицу. Второй контакт мемристора 5 подключен к проводящей линии, которая гальванически объединяет контакты мемристорных ячеек на одной строке для реализации функций конъюнкций и дизъюнкций.

Мемристорные ячейки с КМОП транзисторами объединены в равномерную прямоугольную матрицу (фиг. 2). Топология матрицы представляет собой структуру из двух основных слоев: нижний КМОП слой транзисторов, на который через изолятор 21 нанесен верхний слой мемристоров 20. Сначала формируют слой КМОП транзисторов по стандартной технологии: на первом этапе в подложке 9 создаются карманы двух полевых n- и р-канальных транзисторов (28 и 26 соответственно); на следующем этапе формируются затворы транзисторов (12 и 22); затем транзисторы соединяют проводниками 16 в комплементарные пары. Далее на заготовке, например, методом магнетронного напыления и с помощью литографии формируют слой диэлектрика 21 с матрицей проводящих переходных колодцев 16, которые присоединяют стоки комплементарных пар транзисторов к нижнему контакту мемристора. Затем методом магнетронного напыления наносят мемристивный слой 20, который состоит из оксида переходного метала толщиной в несколько десятков нанометров, и кросс-проводники, соединяющие мемристорные ячейки в параллельную цепь (15).

Таким образом, в достаточно простом технологическом процессе формируется сетка мемристорных ячеек, которые через слой диэлектрика и сетки переходных колодцев подключаются к транзисторам, наносимым по стандартной технологии КМОП.

Схема логического коммутатора, состоящего из матрицы ячеек с мемристорами и реализующего дизъюнктивные нормальные формы, показана на фиг. 3. Дизъюнктивные нормальные формы позволяют каноническим образом реализовывать любые логические операции, которые требуются для нейроморфного процессора. Количество мемристорных ячеек и подключенных к ним линий растет в соответствии с размерностью матриц, на чертеже показаны только начальные узлы с мемристорными ячейками и линии входов и программирования. Логические переменные подаются на вертикальные линии 35, 39 и 40, 44, подключенные к затворам входных транзисторов 36, 38, 41, 43, 45, 47, 48, 50. Входные транзисторы образуют КМОП структуру и с каждым мемристором (37, 42, 46, 49) формируют элементарные ячейки, которые выполняют функции коммутации. Мемристоры ячеек, запрограммированные заранее в проводящее состояние, подключают соответствующие логические входы к горизонтальным цепям, а мемристоры в непроводящем состоянии отключают входы от этих цепей. При этом с входными переменными, подключаемыми на одну горизонтальную проводящую линию, выполняется функция конъюнкции. Полученные уровни напряжения на горизонтальных цепях далее подаются на матрицу дизъюнкции. Результатом работы схемы являются выходные логические уровни, полученные как функции последовательной конъюнкции и дизъюнкции от входных переменных по скоммутированным связям мемристорными ячейками.

Программирование мемристоров, составляющих ячейки конъюнктивной и дизъюнктивной матриц, осуществляется с помощью КМОП транзисторов 36, 38, 41, 43, 45, 47, 48, 50, подключенных к горизонтальным цепям. Предварительно матрица находится в режиме коммутации логических схем, и оба программирующих транзистора закрыты. Управляющее напряжение, подаваемое на затворы программирующих КМОП транзисторов, включает режим программирования мемристоров. При этом открывается только один программирующий транзистор верхнего или нижнего плеча в зависимости от того, как требуется перепрограммировать мемристор, ввести его в низкоомное или высокоомное состояние. Соответственно для программирования на другом контакте мемристора устанавливается противофазный уровень напряжения через входные КМОП транзисторы, а их затворами управляют входные логические линии.

На фиг. 4 показан результат моделирования матриц, состоящих из одной и из четырех коммутационных ячеек. Сравнение логических уровней при считывании в двух вариантах показывает, что при напряжении питания 3 В, напряжение на выходе матрицы отличается на 1,6%. Основной вклад в различие напряжений вносят переходные процессы в транзисторах, т.е. на более низких скоростях работы устройства зависимость выходного напряжения от размера матрицы можно будет уменьшить. При этом различия в итоговых сопротивлениях мемристоров в высокоомном (100 кОм) и низкоомном (10 кОм) состояниях равны 0,07% и 0,13% соответственно. Это позволяет говорить о достаточно низком влиянии ячеек друг на друга.

Таким образом, предлагаемая логическая матрица, являющаяся комбинацией конъюнктивной и дизъюнктивной матриц, реализует булеву функцию дизъюнктивной нормальной формы с возможностью перепрограммируемой коммутации, которая подходит для построения логики работы нейроморфного устройства.

Логическая матрица на основе мемристорной коммутационной ячейки, представляющая собой устройство для выполнения логических операций, содержащее матрицу переключателей на основе электрически перепрограммируемых ячеек, отличающаяся тем, что в качестве коммутирующего элемента используется ячейка с мемристором и двумя полевыми транзисторами, в которой мемристивный материал наносится сплошным слоем на слой, содержащий матрицу транзисторов.