Патент ссср 264451

Иллюстрации

Показать всеРеферат

26445 I

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советский

Социалистических

Республик

Зависимо" от авт. свидетельства «¹â€”

Кл, 21а1, 36/18

Заявлено 07.Ч!!!.1968 (№ 1263647/18-24) с присоединением заявки ¹â€”

Приоритет

Опубликовано 03.11!.1970. Бюллетень № 9

Дата опубликования описания 17Х!.1970

МПК Н ОЗК

УДК 681.327«53 (088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Авторы изобретения

А. Г. Кухарчук и Л. Я. Приступа

Институт кибернетики АН Украинско" ССР

Заявитель

ЗАПОМИНАЮЩИЙ ДЕШИФРАТОР

Изобретение относится к области электронных цифровых вычислительных машин и устройств автоматики.

Известны запоминающие дешифраторы, разделенные на две группы по признаку четности числа единиц и содержащие блок контроля и схему совпадения, выходы которых через инверторы соединены с шинами выхода.

Для них характерны низкое быстродействие и недостаточно полный контроль.

Описываемый дешифратор отличается тем, что, с целью повышения быстродействия и эффективности контроля, шины выхода каждой группы дешифратора и выход каждого из групповых инверторов блока контроля соединены с соответствующими входами дополнительных схем совпадения, выходы которых через схемы разделения подключены ко входам инверторов.

Это повышает быстродействие дешифратора и эффективность контроля.

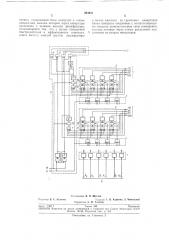

На чертеже изобра>кена схема описываемого дешифратора, где: 1 — развязывающие инверторы; 2 †схе совпадения; 8 — инверторы;

4 — блок контроля; 5 — шины выхода дешифратора; б —; 7, 8 — схемы совпадения; 9, 10 — групповые инверторы; 11 — 18 — схемы совпадения; 14 — схемы разделения; 15 — инвертор; 1б †вх установки «0», 17 †вх занесения; 18 †ши контроля; 19 †21 †схемы совпадения; 22 — 24 — схемы разделения, Описываемый дешифратор состоит из развязывающих ин верторов 1, схем совпадения 2, собственно дешифратора, выходных инверторов 8 и блока контроля 4, в состав которого входят триггер б, схемы совпадения 7 и 8, соединенные через двухвходовые схемы разделения 28 и 24 с групповыми инверторами 9 и 10 соответственно, а также узла сравнения, состоящего из схем совпадения 11 — 18, 19, 20 и инвертора 15.

Каждая из общего количества 2" выходная шина дешифратора пронумерована двоичным п-разрядным кодовым набором, при поступлении которого она выбирается (на чертежг и=3). При разделении выходных инверторо на две группы в одну группу отнесены инверторы, соединенные с выходными шинами, номера которых имеют нечетное количество единиц, в другую — четное. Со входом каждого выходного инвертора соединена введенная схема совпадения «И» через введенную двух« входовую схему разделения «ИЛИ», на второй вход которой поступает сигнал со схем совпадения 2 дешифратора. Количество введенных схем совпадения 21, а также схем разделения 22 равно числу выходных инверторов дешифратора, т. е. 2" .

В каждой из групп выходных инверторов 8

30 произведены соединения между инверторами через введенные схемы «ИЛИ» и «И» таким

264451

3 образом, что на входы схемы «И», соединенной со входом инвертора, поступают потенциалы с выходов всех остальных инверторов группы, в том числе и соответствующего группового инвертора.

Благодаря введенным элементам и соединениям схема дешифратора обладает свойством запоминать состояние, в котором она оказывается во время дешифрации кода.

Цикл дешифрации кода в запоминающем дешифраторе состоит из двух тактов.

1-й такт. На вход 16 схемы подается сигнал «Установка 0», поступающий через схемы

28 и 24 на входы гругповых инверторов 9 и

10 и приводящий к появлению потенциалов нулевого уровня на их выходах. Наличие этих потенциалов приводит к отсутствию совпадений в схемах 21 и появлению потенциалов единичного уровня на выходных шинах дешифратора, совпадение которых в схемах 7 и 8 приводит к тому, что после окончания сигнала «Установка 0» установившееся состояние схемы запоминается.

Это состояние, называемое исходным, характерно тем, что ни одна из выходных шин дешифратора не является выбранной.

2-й такт. В зависимости от значения и-разрядного двоичного кода, поступающего в дешифратор в своем прямом значении в виде сигналов хц, х,,..., х> i и инверсном значении в виде сигналов хо, х, ..., х i, в момент поступления, сигнала «Занесение» на вход 17 устройства срабатывает одна из схем

«И» диодного дешифратора, и на выходе инвертора, соединенного с ней, появляется потенциал нулевого уровня, являющийся сигналом выбранной выходной шины дешифратора.

Сигнал, появившийся на выбранной выходной шине, запоминается. Запоминание его происходит аналогично запоминанию исходного соединения. При этом на всех невыбранных выходных шинах и на выходе группового инвертора, относящемся к той группе, где имеется выбранная выходная шина, запоминаются потенциалы единичного уровня.

После прекращения сигнала «Занесение» установившиеся значения потенциалов сохраняются.

В данном дешифраторе совмещены во времени процессы дешифрации и запоминания результата дешифрации, что приводит к существенному уменьшению временных задержек,> схеме, увеличению скорости срабатыванич дешифратора.

В схеме дешифратора-прототипа с момента поступления сигнала «Занесение» до моменга появления сигнала на выбранной выходной шине (существующего также после прекращения сигнала занесения) наблюдается за держка сигнала в трех инверторах, тогда как в предлагаемом запоминающем дешифраторе †толь в одном инверторе.

Работа блока контроля 4 по обнаружению в запоминающем дешифраторе одиночных

4 ошибок и неисправностей, приводящих к одиночным ошибкам, происходит также в два рабочих такта дешифратора, 1-й такт. С поступлением сигнала «Установка О» происходит установка запоминающего дешифратора в исходное состояние и срабатывает триггер б блока контроля таким образом, что на его выходе, соединенном с схемами

11 и 12, устанавливается потенциал едини шого уровня.

Одиночные ошибки, возникшие из-за,неисправности нагрузок дешифратора, одного из выходных инверторов или одного из диодов схем совпадения 21, приводящие в данном случае к появлению потенциала нулевого уровня на одной из выходных шин дешифратора (ложной выборке шины), вызывают выход схем из исходного состояния, что обнаруживается с помощью схем 11 и 12 блока контроля по появлению потенциала единичного уровня на выходе одного из групповых инверторов 9 и 10 и приводит к появлению сигнала ошибки на выходе 18 схемы (шине контроля).

Таким образом, в этом такте цикла дешифрации контролем охвачены кроме выходных цепей также и выходные инверторы и шины дешифратора.

2-й такт. С поступлением сигнал «Занесение» происходит выборка одной из выходных шин дешифратора, а акже ее запоминание..

Кроме того, изменяет свое состояние триггер б блока контроля и на его выходе, соединенном со схемами 19 и 20, появляется потенциал единичного уровня.

Одиночные ошибки, вызванные неисправностью одного из развязывающих инверторов (1) или одного из диодов в схемах 2 диодного дешифратора, приводят к тому, что схема либо не выходит из исходного состояния, либо, кроме истин но выбранной шины, относящейся к одной из групп, имеет место ложно выбранная выходная шина в другой группе.

В первом из этих случаев на обоих групповых инверторах 9 и 10 появляются потенциалы нулевого уровня, а в другом — оба потенциала единичного уровня.

С помощью схем 18, 19, 20 и инвертора 15, реализующих логическую функцию равнозначности указанных потенциалов (П9 П 1)

4 11 к —

Развязывающие инверторы предназначены для устранения влияния на регистр, с которого поступает код в дешифратор, неисправностей дешифратора, приводящих к искажешпо одного из разрядов двоичного кода, подлежащего дешифрации.

Если засылка кода в названный дешифратор контролируется, то инвертор 1 следует исключить.

Предмет изобретения

Запоминающий дешифратор, разделенный на две группы по признаку четности числа

264451

1б

Составитель В. М. Щеглов

Тскрсды Т, П. Курилко, 3. Чижевский

Корректор А. М. Глазова

Рс.тактор Б. С. Нинкина

Зака". 1505 7 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4,5

Типография, пр. Сапунова, 2 единиц. содержащий блок контроля и схемы совпадения, выходы которых через инверторы соединены с шинами выхода дешифратора, отлича оций ся тем, что, с целью повышения быстродействия и эффективности контроля, ши - ы выхо.".а каждой группы дешифратора и выход каждого из групповых инверторов бло1:а контроля соединены с соответствующими гходами дополн:1тельных схем совпадения, выходы которых через схемы разделен1гя подключены ко входам IIHI:åðòîðîâ. т

1бб

О C

05 l I