Инструкция и логика для идентификации инструкций для удаления в многопоточном процессоре с изменением последовательности

Иллюстрации

Показать всеГруппа изобретений относится к области обработки информации и может быть использована для идентификации инструкций для удаления в многопоточном процессоре с изменением последовательности. Техническим результатом является повышение пропускной способности конвейерной обработки и улучшение производительности. Процессор содержит первую логику для выполнения потока инструкций с изменением последовательности, причем поток инструкций разделен на множество субпотоков, при этом поток инструкций и каждый субпоток упорядочен порядком программы (PO); вторую логику для определения старейшей неотправленной инструкции в потоке инструкций и хранения связанного PO значения старейшей неотправленной инструкции в качестве указателя выполненной инструкции, причем поток инструкций включает в себя отправленные и неотправленные инструкции; третью логику для определения последней удаленной инструкции в потоке инструкций и хранения связанного PO значения последней удаленной инструкции в качестве указателя удаления; четвертую логику для выбора диапазона инструкций между указателем удаления и указателем выполненной инструкции и пятую логику для идентификации инструкций в диапазоне в качестве подлежащих удалению. 3 н. и 17 з.п. ф-лы, 34 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к области логики обработки информации, микропроцессорам и ассоциированной с ними архитектуре набора команд, которые при выполнении процессором или другой логической схемой обработки информации, выполняют логические, математические или другие функциональные операции.

Уровень техники

Многопроцессорные системы становятся все более и более распространенным явлением. Способ применения многопроцессорных систем включает в себя динамический домен, структурируя вплоть до настольных компьютеров. Для того чтобы воспользоваться преимуществами многопроцессорных систем, код потока, подлежащий выполнению, может быть разделен посредством планировщиков на множество потоков для выполнения посредством различных устройств обработки. Каждый поток может быть обработан параллельно с другим потоком. Более того, чтобы увеличить функциональность устройства обработки может быть использован способ выполнения с изменением последовательности команд. Способ выполнения с изменением последовательности команд может выполнять инструкции, когда необходимо обеспечить доступность ввода таких инструкций. Таким образом, инструкция, которая появляется позже в кодовой последовательности, может быть выполнена перед инструкцией, появляющейся ранее в кодовой последовательности.

Краткое описание чертежей

Варианты осуществления проиллюстрированы в качестве примера, и не ограничены на прилагаемых чертежах:

Фиг. 1А показывает блок-схему иллюстративной компьютерной системы, сформированной процессором, который может включать в себя исполнительные блоки для выполнения инструкции, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 1B иллюстрирует систему обработки данных в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 1С иллюстрирует другие варианты осуществления системы обработки данных для выполнения операций сравнения текстовой строки;

Фиг. 2 показывает блок-схему микроархитектуры для процессора, который может включать в себя логические схемы для выполнения инструкции, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 3A иллюстрирует различные представления типа упакованных данных в мультимедийных регистрах, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 3B иллюстрирует возможные форматы хранения данных в регистре, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 3C показывает различные представления типов упакованных данных со знаком и беззнаковые в мультимедийных регистрах, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 3D показывает вариант осуществления формата кодирования операции;

Фиг. 3E показывает другой возможный формат кодирования операции, имеющий сорок или больше битов, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 3F иллюстрирует еще один возможный формат кодирования операции, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 4А представляет собой блок-схему, иллюстрирующую упорядоченный конвейер и этап переименования регистра, конвейер с изменением последовательности команд, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 4B показывает блок-схему, иллюстрирующую упорядоченную архитектуру ядра и логику переименования регистров, логику с изменением последовательности команд, включенную в состав процессора, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 5А показывает блок-схему процессора, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 5B показывает блок-схему примерной реализации ядра, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 6 показывает блок-схему системы, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 7 показывает блок-схему второй системы, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 8 показывает блок-схему третьей системы в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 9 показывает блок-схему системы-на-кристалле, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 10 показывает процессор, содержащий центральный блок обработки и блок обработки графики, который может выполнять, по меньшей мере, одну инструкцию, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 11 показывает блок-схему, иллюстрирующую разработку IP ядер, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 12 показывает, как инструкция первого типа может быть эмулирована процессором другого типа, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 13 показывает блок-схему, различающую использование конвертора команд программного обеспечения для преобразования двоичных инструкций в наборе источника команды в двоичные инструкции в целевом наборе команд, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 14 представляет собой блок-схему архитектуры набора команд процессора, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 15 представляет собой более подробную блок-схему архитектуры набора команд процессора, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 16 показана блок-схема конвейера для выполнения команд для процессора, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 17 показывает блок-схему электронного устройства для использования процессора, в соответствии с вариантами осуществления настоящего изобретения;

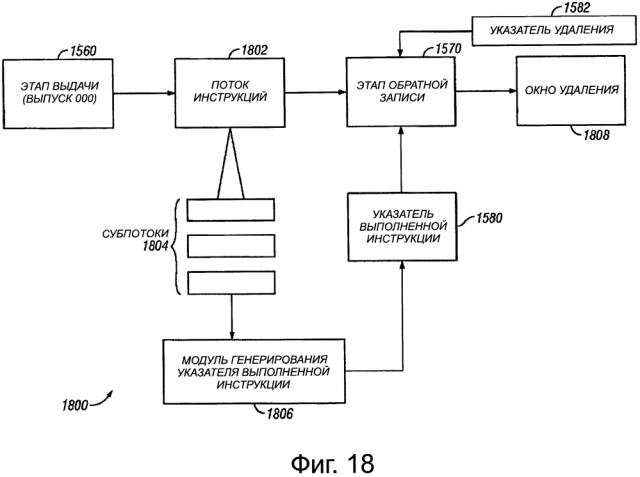

Фиг. 18 показывает функциональную блок-схему системы для выполнения инструкции и логику для идентификации инструкций, подходящих для удаления, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 19А-19Е показывают более детальный вид системы для выполнения инструкции и логики для идентификации инструкций, подходящих для удаления, в соответствии с вариантами осуществления настоящего изобретения;

Фиг. 20 является иллюстрацией примера аппаратной логики для определения минимального значения порядка программы среди множества потоков в соответствии с вариантами осуществления настоящего изобретения; и

Фиг. 21 является иллюстрацией примера способа для идентификации инструкций, подходящих для удаления, в соответствии с вариантами осуществления настоящего изобретения.

Подробное описание

Следующее описание описывает инструкцию и логику обработки для идентификации инструкций, подходящие для удаления, в пределах или совместно с процессором, виртуальным процессором, пакете, компьютерной системой или другими устройствами обработки. Такое устройство обработки может включать в себя процессор с изменением последовательности команд. Более того, такое устройство обработки может включать в себя многопоточный процессор с изменением последовательности команд. В последующем описании многочисленные конкретные детали, такие как логическая схема обработки, типы процессоров, микроархитектурные условия, события, механизмы решений и тому подобное изложены для обеспечения более полного понимание вариантов осуществления настоящего изобретения. Следует принять во внимание специалистам в данной области техники, что варианты осуществления могут быть реализованы без таких конкретных деталей. Кроме того, некоторые хорошо известные структуры, схемы и тому подобное не показаны подробно для упрощения описания вариантов осуществления настоящего изобретения.

Несмотря на то, что следующие варианты осуществления описаны со ссылкой на процессор, другие варианты осуществления применимы к другим типам интегральных схем и логических устройств. Подобные способы и идеи вариантов осуществления настоящего изобретения могут быть применены к другим типам схем или полупроводниковым устройствам, которые могут получить выгоду от более высокой пропускной способности конвейерной обработки и улучшенной производительности. Идеи вариантов осуществления настоящего раскрытия применимы к любому процессору или машине, которая выполняет обработку данных. Однако варианты осуществления не ограничены процессорами или машинами, которые выполняют 512-битные, 256-битные, 128-битные, 64-битные, 32-битные или 16-битные операции с данными и могут быть применены к любому процессору и машине, в которой может быть осуществлено манипуляция или управление данными. Кроме того, в последующем описании, приведенные примеры и прилагаемые чертежи показывают различные примеры для целей иллюстрации. Однако эти примеры не следует рассматривать в ограничительном смысле, так как они предназначены только для обеспечения примеров вариантов осуществления настоящего изобретения, а не с целью дать исчерпывающий перечень всех возможных вариантов реализации вариантов осуществления настоящего изобретения.

Хотя, приведенные ниже примеры описывают процесс обработки команд и распределение в контексте исполнительных блоков и логических схем, другие варианты осуществления настоящего изобретения, могут быть получены путем передачи данных или инструкций, хранящихся на машиночитаемом, материальном носителе, которые, когда выполняются машиной, предписывают машине выполнять функции, в соответствии, по меньшей мере, с одним из вариантов осуществления изобретения. В одном из вариантов осуществления функции, ассоциированные с вариантами осуществления настоящего изобретения, воплощены в машиноисполняемые инструкции. Инструкции могут быть использованы для вызова процессора общего назначения или процессора специального назначения, которые могут быть запрограммированы инструкциями для выполнения этапов настоящего изобретения. Варианты осуществления настоящего изобретения могут быть представлены в виде компьютерного программного продукта или программного обеспечения, которое может включать в себя машину или компьютерно-считываемый носитель, имеющий сохраненные на нем команды, которые могут быть использованы для программирования компьютера (или других электронных устройств) для выполнения одной или более операций в соответствии с вариантами осуществления настоящего изобретения. Кроме того, этапы осуществления настоящего изобретения могут быть выполнены с помощью специальных компонентов аппаратных средств, которые содержат фиксированные логические функции для выполнения этапов, или любой комбинацией программируемых компьютерных компонентов и аппаратных компонентов с фиксированными функциями.

Инструкции, используемые для программной логики, для выполнения вариантов осуществления настоящего изобретения могут быть сохранены в памяти в системе, такой как DRAM, кэш, флэш-память или другое запоминающее устройство. Кроме того, инструкции могут быть распределены по сети или посредством другого считываемого компьютером носителя информации. Таким образом, машиночитаемый носитель информации может включать в себя любой механизм для хранения или передачи информации в форме, считываемой машиной (например, компьютером), но не ограничиваясь этим, гибкие диски, оптические диски, компакт-диск, компакт-диск постоянной памяти (CD-ROMs) и магнитооптические диски, память только для чтения (ROMs), оперативное запоминающее устройство (RAM), стираемое программируемое постоянное запоминающее устройство (EPROM), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM), магнитные или оптические карты, флэш-память, или материальный машиночитаемый носитель информации, используемый при передаче информации через интернет с помощью электрических, оптических, акустических или других форм распространяющихся сигналов (например, несущие волны, инфракрасные сигналы, цифровые сигналы и т.д.). Соответственно, считываемый компьютером носитель информации может включать в себя любой тип материального машиночитаемого носителя информации, пригодный для хранения или передачи электронных инструкций или информации в форме, считываемой машиной (например, компьютером).

Разработка может осуществляться посредством реализации различных этапов, от создания до компьютерного моделирования и до изготовления. Данные, представляющие конструкцию, могут представлять конструкцию в цифровом виде. Во-первых, как это может быть полезно при моделировании, аппаратные средства могут быть представлены с использованием языка описания аппаратных средств или другого функционального языка описания. Кроме того, модель уровня схемы с логическим и/или транзисторным затвором могут быть изготовлены на некоторых этапах процесса проектирования. Кроме того, конструкции, на каком-то этапе, может достичь уровня данных, представляющие физическое размещение различных устройств в аппаратной модели. В тех случаях, в которых некоторые способы полупроводникового производства используются, данные, представляющие модель аппаратных средств, могут быть данными, указывающими на наличие или отсутствие различных признаков на различных уровнях маски для масок, используемых для производства интегральных схем. В любом представлении конструкции данные могут быть сохранены в любой форме машиночитаемого носителя. Память или магнитные или оптические запоминающие устройства, такие как диск, может быть машиночитаемым носителем информации для хранения информации, передаваемой с помощью модулированной оптической или электрической волны или иным образом генерироваться для передачи такой информации. При передаче электрической несущей волны с указанием или несущая код или информации о структуре, при этой осуществляется копирование, буферизация или повторная передача электрического сигнала, может быть сделана новая копия. Таким образом, провайдер связи или сетевой провайдер может хранить на материальном машиночитаемом носителе информации, по меньшей мере, временно, в статье, такой как, информация, закодированная на несущей волне, реализуя способы вариантов осуществления настоящего изобретения.

В современных процессорах могут быть использованы различные исполнительные блоки для обработки и выполнения различных кодов и инструкций. Некоторые инструкции могут быть обработаны быстрее, в то время как другие могут занять несколько тактовых циклов для завершения. Чем выше производительность команд, тем лучше общая производительность процессора. Таким образом, было бы выгодно иметь, на сколько это возможно, больше быстродействующих инструкций. Тем не менее, могут существовать определенные инструкции, которые имеют большую сложность и требуют больше с точки зрения времени выполнения и ресурсов процессора, такие как инструкции с плавающей запятой, операции загрузки/сохранения, перемещение данных и т.д.

Поскольку все больше компьютерных систем используются в интернете, в текстовых и мультимедийных приложениях, была использована дополнительная поддержка процессора в течение долгого времени. В одном варианте осуществления набор инструкций может быть связан с одной или более компьютерных архитектур, включающая в себя типы данных, инструкции, архитектуру регистра, режимы адресации, архитектуру памяти, обработку прерываний и исключений и внешний ввод/вывод (I/O).

В одном варианте осуществления архитектура системы команд (ISA) может быть реализована с помощью одной или нескольких микроархитектур, которые могут включать в себя логику и схемы процессора, используемые для реализации одного или нескольких наборов команд. Соответственно, процессоры с различными микроархитектурами могут совместно использовать, по меньшей мере, часть общего набора инструкций. Например, Intel® Pentium 4 процессоры, процессоры Intel® Core™ и процессоры, изготовленные Advanced Micro Devices, Inc. Саннивейл CA реализовывают почти идентичные версии набора инструкций x86 (с некоторыми расширениями, которые были добавлены в более новые версии), но имеют различные внутренние конструкции. Аналогично, процессоры, разработанные другими компаниями в области разработки процессоров, такие как ARM Holdings, Ltd., MIPS или их лицензиаты или соразработчики, могут совместно использовать, по меньшей мере, часть общего набора команд, но могут включать в себя различные конструкции процессора. Например, та же архитектура регистра ISA может быть реализована по-разному в разных микроархитектурах с использованием новых или хорошо известных технологий, включающие в себя специализированные физические регистры, один или более динамически выделенных физических регистров с использованием механизма переименования регистра (например, использование таблицы псевдонимов регистров (RAT), буфера переупорядочения (ROB) и файла удаления регистра). В одном из вариантов осуществления регистры могут включать в себя один или несколько регистров, архитектуры регистров, регистровые файлы или другие наборы регистров, которые могут или не могут быть переадресованы с помощью программного обеспечения.

Инструкция может включать в себя один или несколько форматов команд. В одном варианте осуществления формат команд может указывать на различные поля (число битов, расположение битов и т.д.), чтобы указать, среди прочего, какая операция должна быть выполнена, и операнды, на которых будут выполняться, что операция. В дополнительном варианте осуществления, некоторые форматы команд могут быть дополнительно определены с помощью шаблонов команд (или субформаты). Например, шаблоны команд заданного формата команд могут быть определены, чтобы иметь различные подмножества полей формата команды и/или определены, чтобы иметь заданное поле, которое интерпретируется иным образом. В одном варианте осуществления команда может быть выражена с помощью формат команд (и, если определено, в данном одном из шаблонов команд этого формата инструкции) и устанавливает или указывает на операцию и операнды, на которых операция будет работать.

Научные, финансовые, автовекторные общего назначения, RMS (распознавание, анализ и синтез) и визуальные и мультимедийные приложения (например, 2D/3D графика, обработка изображений, сжатие/распаковка видео, алгоритмы распознавания голоса и аудио манипуляции) могут быть обработаны посредством одной и той же операции на большом количестве элементов данных. В одном из вариантов осуществления архитектура с одним потоком команд и несколькими потоками данных (SIMD) относится к типу инструкции, которая вызывает процессор выполнить операции с множеством элементов данных. Технология SIMD может использоваться в процессорах, которые могут логически разделить биты в регистре на ряд с фиксированной величиной или переменной величиной элементов данных, каждое из которых представляет собой отдельное значение. Например, в одном варианте осуществления биты в 64-битовом регистре могут быть организованы как операнд-источника, содержащий четыре отдельных 16-битовых элементов данных, каждый из которых представляет собой отдельное 16-битное значение. Этот тип данных может упоминаться как "упакованный" тип данных, или "вектор" типа данных, и операнды этого типа данных могут упоминаться как операнды упакованных данных или векторные операнды. В одном варианте осуществления элемент упакованных данных или вектор может представлять собой последовательность из элементов упакованных данных, сохраненных в одном регистре, и операнд упакованных данных или вектор операнд может быть исходным или конечным операндом SIMD инструкции (или 'инструкции упакованных данных' или 'инструкции вектора'). В одном варианте осуществления SIMD инструкция определяет одну векторную операцию, выполняемую на двух исходных векторных операндах, чтобы сгенерировать операнд вектора назначения (также называемый как операнд результирующего вектора) одного и того же или разного размера, с тем же или другим числом элементов данных, и в таком же или другом порядке элементов данных.

SIMD технологии, такие как, применяемые процессорами Intel® Core™, имеющие набор команд, включающий в себя х86, MМХ™, потоковые SIMD-расширения (SSE), SSE2, SSE3, инструкции SSE4.1 и SSE4.2, ARM процессоры, такие как ARM Cortex® семейства процессоров, имеющие набор команд, включающий в себя вектор с плавающей точкой (VFP) и/или инструкций NEON, и процессоры MIPS, такие как семейство Loongson процессоров, разработанных Институтом вычислительной техники (ICT) в китайской академии наук, позволили значительное повысить производительность приложений (Core™ и MМХ™ являются зарегистрированными товарными знаками или товарными знаками корпорации Intel в Санта-Клара, штат Калифорния).

В одном из вариантов осуществления регистры/данные источника и назначения могут быть общими терминами для представления источника и назначения соответствующих данных или операции. В некоторых вариантах осуществления они могут быть реализованы с помощью регистров, памяти или других мест хранения, имеющих другие названия или функции, чем те, которые представлены. Например, в одном варианте осуществления, "DEST1" может быть регистром временного хранения или другой областью хранения данных, в то время, как "SRC1" и "SRC2" могут быть первым и вторым регистром исходного хранения или другой областью памяти и так далее. В других вариантах осуществления, два или более SRC и DEST областей хранения могут соответствовать разным элементам хранения данных в пределах одной области хранения (например, SIMD регистр). В одном из вариантов осуществления один из исходных регистров может также выступать в качестве регистра назначения, например, посредством обратной записи результата операции, выполняемой на первых и вторых исходных данных, на один из двух исходных регистров, служащих в качестве регистров назначения.

На фиг. 1А показана блок-схема иллюстративной компьютерной системы, сформированной процессором, который может включать в себя исполнительные блоки для выполнения инструкции, в соответствии с вариантами осуществления настоящего изобретения. Система 100 может включать в себя компонент, такой как процессор 102, применяя исполнительные блоки, включающие в себя логику для выполнения алгоритмов для обработки данных, в соответствии с настоящим изобретением, например, в варианте осуществления, описанном в данном документе. Система 100 может быть примером систем обработки, основанные на Pentium® III, Pentium® 4, Xeon™, Itanium®, XScale™ и/или микропроцессорам StrongARM™, которые обеспечиваются Intel Corporation Санта-Клара, штат Калифорния, хотя другие системы (включающие в себя персональные компьютеры, имеющие другие микропроцессоры, инженерные рабочие станции, телевизионные приставки и тому подобное) могут быть использованы. В одном варианте осуществления примерная система 100 может использовать версию операционной системы WINDOWS™, предоставляемую Microsoft Corporation в Редмонде, штат Вашингтон, хотя другие операционные системы (UNIX и Linux, например), встроенное программное обеспечение и/или графические пользовательские интерфейсы, также могут использоваться. Таким образом, варианты осуществления настоящего изобретения не ограничены какой-либо конкретной комбинацией схем аппаратного и программного обеспечения.

Варианты осуществления не ограничиваются компьютерными системами. Варианты осуществления настоящего изобретения могут быть использованы и в других устройствах, таких как портативные устройства и встроенные приложения. Некоторые примеры портативных устройств включают в себя сотовые телефоны, устройства интернет протокола, цифровые камеры, персональные цифровые помощники (PDA) и карманные ПК. Встроенные приложения могут включать в себя микроконтроллер, цифровой сигнальный процессор (DSP), систему на кристалле, сетевые компьютеры (NetPC), телеприставки, сетевые концентраторы, переключатели глобальной сети (WAN) или любую другую систему, которая может выполнять одну или несколько инструкций в соответствии, по меньшей мере, с одним вариантом осуществления.

Компьютерная система 100 может включать в себя процессор 102, который может включать в себя один или более исполнительных блоков 108 для выполнения алгоритма для выполнения, по меньшей мере, одной инструкции, в соответствии с одним из вариантов осуществления настоящего изобретения. Один вариант осуществления изобретения может быть описан в контексте одного настольного процессора или серверной системы, но другие варианты осуществления могут быть включены в состав многопроцессорной системы. Система 100 может быть примером архитектуры системы "хаба". Система 100 может включать в себя процессор 102 для обработки сигналов данных. Процессор 102 может включать в себя микропроцессор со сложным набором команд (CISC), микропроцессор с сокращенным набором команд (RISC), микропроцессор с командными словами очень большой длины (VLIW), процессор, реализующий комбинацию наборов инструкций или любой другой процессор, например, такой как процессор цифровых сигналов, например. В одном варианте осуществления, процессор 102 может быть соединен с шиной 110 процессора, которая может передавать сигналы данных между процессором 102 и другими компонентами в системе 100. Элементы системы 100 могут выполнять обычные функции, которые хорошо известны специалистам в данной области техники.

В одном варианте осуществления, процессор 102 может включать в себя LI внутренний кэш 104 первого уровня. В зависимости от архитектуры, процессор 102 может иметь один внутренний кэш или множество уровней внутреннего кэша. В другом варианте осуществления, кэш-память может находиться вне процессора 102. Другие варианты осуществления могут также включать в себя комбинацию внутренних и внешних кэшей в зависимости от конкретной реализации и потребностей. Регистровый файл 106 может хранить различные типы данных в различных регистрах, включающие в себя целочисленные регистры, регистры с плавающей запятой, регистры состояния и регистр указателя инструкций.

Исполнительный блок 108, включающий в себя логику для выполнения целочисленных операций и вычислений с плавающей запятой, также находится в процессоре 102. Процессор 102 также может включать в себя микрокод (UCODE) ROM, которое хранит микрокод для некоторых макрокоманд. В одном варианте осуществления исполнительный блок 108 может включать в себя логику для обработки набора 109 упакованных команд. Включением набора 109 упакованных команд в набор команд процессора 102 общего назначения, а также с соответствующей схемой для выполнения команд, операции, используемые многими мультимедийными приложениями, могут выполняться с использованием упакованных данных в процессоре 102 общего назначения. Таким образом, многие мультимедийные приложения могут быть ускорены и выполняться более эффективно при использовании полной ширины шины данных процессора для выполнения операций с упакованными данными. Это может устранить необходимость передачи более мелких блоков данных по шине передачи данных процессора для выполнения одной или более операций одного элемента данных за один раз.

Варианты осуществления исполнительного блока 108 также могут быть использованы в микроконтроллерах, встроенных процессорах, графических устройствах, DSPs и в других типах логических схем. Система 100 может включать в себя память 120. Память 120 может быть реализована в виде устройства динамической памяти с произвольным доступом (DRAM), устройства статической оперативной памяти (SRAM), устройства флэш-памяти или другого устройства памяти. Память 120 может хранить инструкции и/или данные, представленные сигналами данных, которые могут быть выполнены процессором 102.

Системная логическая микросхема 116 может быть соединена с шиной НО процессора и памятью 120. Системная логическая микросхема 116 может включать в себя концентратор контроллера памяти (МСН). Процессор 102 может осуществлять связь с МСН 116 через шину 110 процессора. МСН 116 может обеспечить тракт 118 памяти с высокой пропускной способностью к памяти 120 для передачи и хранения данных и для хранения графических команд, данных и текстур. МСН 116 может направлять сигналы данных между процессором 102, памятью 120 и другими компонентами в системе 100 и служит мостом для сигналов данных между шиной 110 процессора, памятью 120 и системой 122 ввода/вывода. В некоторых вариантах осуществления системная логическая микросхема 116 может обеспечивать графический порт для соединения с графическим контроллером 112. МСН 116 может быть соединен с памятью 120 через интерфейс 118 памяти. Графическая карта 112 может быть соединена с МСН 116 через межсоединение 114 быстродействующего графического порта (AGP).

Система 100 может использовать шину 122 интерфейса собственного концентратора для соединения МСН 116 с концентратором 130 I/O контроллера (ICH). В одном варианте осуществления МСН 130 может обеспечить прямое подключение с некоторыми устройствами ввода/вывода через локальную шину ввода/вывода. Локальная шина ввода/вывода может включать в себя высокоскоростную шину ввода/вывода для подключения периферийных устройств к памяти 120, набору микросхем и процессору 102. Примеры могут включать в себя аудио контроллер, концентратор 128 встроенного программного обеспечения (флэш-BIOS), беспроводной приемопередатчик 126, блок 124 хранения данных, унаследованный контроллер ввода/вывода, содержащий пользовательские интерфейсы ввода и клавиатуры, последовательный порт расширения, такой как универсальная последовательная шина (USB) и сетевой контроллер 134. Блок 124 хранения данных может содержать жесткий диск, флоппи-дисковод, CD-ROM, устройство флэш-памяти или другое запоминающее устройство.

В качестве другого варианта осуществления системы, инструкция в соответствии с одним вариантом осуществления, может быть использована с системой на кристалле. Один из вариантов осуществления системы на кристалле включает в себя процессор и память. Память для одной такой системы может включать в себя флэш-память. Флэш-память может быть расположена на том же кристалле, что и процессор, и другие компоненты системы. Кроме того, другие логические блоки, такие как контроллер памяти или графический контроллер также могут быть расположены в системе на кристалле.

Фиг. 1B изображает систему 140 обработки данных, которая реализует принципы вариантов осуществления настоящего изобретения. Как очевидно для специалистов в данной области техники, варианты осуществления, описанные здесь, могут работать с альтернативными системами обработки данных без отхода от сущности и объема вариантов осуществления изобретения.

Компьютерная система 140 содержит процессорное ядро 159 для выполнения, по меньшей мере, одной инструкции, в соответствии с одним вариантом осуществления. В одном из вариантов осуществления процессорное ядро 159 представляет собой блок обработки любого типа архитектуры, включающей в себя, но не ограничиваясь этим, CISC, RISC или VLIW тип архитектуры. Процессорное ядро 159 также может быть изготовлено посредством одного или нескольких технологических процессов, и посредством представления на машиночитаемом носителе информации достаточно подробно, может быть пригодно для облегчения упомянутого производства.

Процессорное ядро 159 содержит исполнительный блок 142, набор регистровых файлов 145 и декодер 114. Процессорное ядро 159 может также включать в себя дополнительные схемы (не показаны), которые могут быть ненужными для понимания вариантов осуществления настоящего изобретения. Исполнительный блок 142 может выполнять инструкции, полученные процессорным ядром 159. В дополнение к выполнению типовых инструкций процессора, исполнительный блок 142 может выполнять инструкции в наборе 143 упакованных команд для выполнения операций над форматами упакованных данных. Набор 143 упакованных команд может включать в себя инструкции для выполнения вариантов осуществления изобретения и других упакованных инструкций. Исполнительный блок 142 может быть соединен с регистровым файлом 145 с помощью внутренней шины. Регистровый файл 145 может представлять собой область хранения на процессорном ядре 159 для хранения информации, в том числе данных. Как упоминалось ранее, следует понимать, что область для хранения может хранить упакованные данные, но это не является критическим. Исполнительный блок 142 может быть соединен с декодером 144. Декодер 144 может декодировать инструкции, полученные процессорным ядром 159 в управляющие сигналы и/или точки входа микрокода. В ответ на эти сигналы управления и/или точек входа микрокода, исполнительный блок 142 выполняет соответствующие операции. В одном варианте осуществления декодер может интерпретировать опкод инструкции, который будет указывать на то, что операция должна выполняться на соответствующих данных, указанных в инструкции.

Процессорное ядро 159 может быть соединено с шиной 141 для связи с различными другими системными устройствами, которые могут включать в себя, но не ограничиваются ими, например, блок 146 управления синхронным динамическим оперативным запоминающим устройством (SDRAM), блок 147 управления статическим оперативным запоминающим устройством (SRAM), интерфейс 148 пакетной флэш-памяти, блок управления 149 картой памяти персонального компьютера международной ассоциации (РСМС1А)/карта памяти (CF), блок управления 150 жидкокристаллическим дисплеем (LCD), контроллер 151 прямого доступа к памяти (DMA) и главный интерфейс 152 альтернативной шины. В одном из вариантов осуществления, система 140 обработки данных также может включать в себя мост 154 ввода/вывода для связи с различными устройствами ввода/вывода через шину 153 ввода/вывода. Такие устройства ввода/вывода могут включать в себя, но не ограничиваются ими, например, универсальный асинхронный приемник/передатчик (UART) 155, универсальную последовательную шину (USB) 156, Bluetooth беспроводного UART 157 и интерфейс 158 расширения ввода/вывода.

Один из вариантов осуществления системы 140 обработки данных обеспечивает для мобильных устройств, сетевой и/или беспроводной связи и процессорного ядра 159, которые могут выполнять SIMD операции, включающую в себя операцию сравнения текстовой строки. Процессорное ядро 159 может быть запрограммировано с помощью различных аудио, видео, изображений и алгоритмов коммуникаций, включающие в себя дискретные преобразования, такие как преобразование Уолша-Адамара, быстрое преобразование Фурье (FFT), дискретное косинусное преобразование (DCT) и их соответствующие обратные преобразования; способы сжатия/распаковки, такие как преобразование цветового пространства, оценка движения кодирования видео или компенсация движения декодирования видео; и функции модуляции/демодуляции (МОДЕМ), такие как импульсно-кодовая модуляция (РСМ).

На фиг. 1С показаны другие варианты осуществления системы обработки данных, которая выполняет SIMD-операции сравнения текстовых строк. В одном из вариантов осуществления, система 160 обработки данных может включать в себя центральный процессор 166, а SIMD сопроцессор 161, кэш-память 167 и систему 168 ввода/вывода. Система 168 ввода/вывода может быть дополнительно соединена с беспроводным интерфейсом 169. SIMD-сопроцессор 161 может выполнять операции, включающие в себя инструкции согласно одному варианту осуществления изобретения. В одном из вариантов осуществления процессорное ядро 170 может быть пригодным для производства посредством одного или нескольких технологических процессов, а также представлено на машинно-читаемом носителе информации достаточно подробно, что может быть пригодным для облегчения изготовления всей или части системы 160 обработки данных, включающей в себя процессорное ядро 170.

В одном из вариантов осуществления, SIMD-сопроцессор 161 содержит исполнительный блок 162 и набор регистровых файлов 164. Один из вариантов основного процессора 165 содержит декодер 165, чтобы распознавать команды из набора 163 инструкций, включающие в себя инструкции, в соответствии с одним вариантом осуществления для исполнения исполнительным блоком 162. В других вариантах осуществления, SIMD-сопроцессор 161 также включает в себя, по меньшей мере, часть декодера 165 для декодирования инструкций набора 163 инструкций. Процессорное ядро 170 может также включать в себя дополнительные схемы (не показаны), которые могут быть излишними для понимания вариантов осуществления настоящего изобретения.

В процессе работы ос