Управление колебаниями инициатора ввода/вывода при передаче

Иллюстрации

Показать всеИзобретение относится к средствам обеспечения связи между электронными устройствами. Технический результат - обеспечение схемы ввода/вывода с полным колебанием выходного напряжения для возбуждения выходного сигнала. Схема интерфейса линии передачи включает в себя регулятор напряжения для управления колебанием напряжения схемы интерфейса линии передачи для передачи сигналов. Схема интерфейса линии передачи включает в себя элементы комплементарного инициатора, включающие в себя элемент инициатора р-типа, для подъема напряжения в линии передачи в ответ на высокий логический уровень и элемент инициатора n-типа для понижения напряжения в линии передачи в ответ на логически низкий уровень. Регулятор напряжения соединен между одним из элементов инициирования и соответствующим опорным напряжением для уменьшения колебания напряжения в схеме интерфейса линии передачи. 3 н. и 15 з.п. ф-лы, 14 ил.

Реферат

Область техники, к которой относится изобретение

Варианты осуществления изобретения в общем, относятся к связи между устройствами и более конкретно к управлению колебаниями инициатора связи между устройствами.

Уведомление об авторском праве/разрешении

Части раскрытия данного патентного документа могут содержать материал, который защищен авторским правом. Владелец авторского права не возражает против воспроизведения любого из патентного документа или патентного раскрытия в том виде, как они представлены в файле ведомства по патентам и товарным знакам или в записях, но в остальном сохраняет все авторские права. Уведомление о защите авторских прав относится ко всем данным, описанным ниже, и к приложенным к ним чертежам, а также к любому программному обеспечению, описанному ниже: Copyright © 2013, Intel Corporation, All Rights Reserved.

Уровень техники

Связь между компонентами на хост платформе необходима для работы электронного устройства. Однако связь включает в себя использование выходной линии или инициаторов линии передачи, потребляющих существенное количество общей энергии, используемой в электронных устройствах. Например, связь между процессором и памятью, между контроллером памяти и процессором, между контроллером памяти и запоминающим устройством, между периферийным контроллером и процессором или подсистемой памяти, или другая связь, потребляет существенное количество энергии. Обычно связь между разными компонентами может называться вводом-выводом (I/O) и часто управляется стандартами (например, между компонентами подсистемы памяти). Стандарты I/O могут относиться к рабочим характеристикам в отношении энергии питания I/O, задержки I/O и частоты I/O. Стандарты или номинальные значения рабочих установок I/O установлены на значения, которые могут быть достигнуты в разных системах для совместимости и обеспечения возможности взаимодействия.

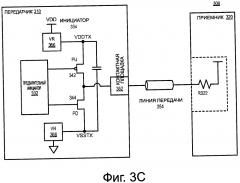

На фиг. 1А показана блок-схема известного выходного инициатора CMOS. Известный выходной инициатор 134 CMOS (комплементарный металлооксидный полупроводник) представляет собой обычную конструкцию для систем I/O. Система 102 включает в себя передатчик 110, осуществляющий связь с приемником 120. Следует понимать, что передатчик 10 представляет собой приемное устройство, когда приемник 120 запускает связь с передатчиком 110. Таким образом, роли устройства передачи и устройства приема могут стать обратными, и выходной инициатор 134 представлен как часть приемопередатчика 130. Однако с целью представленного здесь описания основное внимание направлено, скорее, на передачу сигнала, чем на прием сигнала. С целью передачи сигнала от передатчика 110 в приемник 120 приемник 120 может быть смоделирован как импеданс R122 нагрузки. Передатчик 110 инициирует линию 154 передачи для приемника 120 для приема путем подъема напряжения в линии 154 передачи до уровня VDD через элемент 140 подъема (PU) и опускания напряжения в линии 154 передачи вниз до VSS через элемент 142 опускания (PD). Выходной импеданс R146 обычно согласован с импедансом контактной площадки 152 и линии 154 передачи, как это выглядит для инициатора 134. Предварительный инициатор 132 обеспечивает передачу сигналов и управление для инициатора 134, для вывода сигнала по линии 154 передачи. Контактная площадка 152 формирует интерфейс между устройством 110 передатчика и линией 154 передачи.

Пример использования системы 102 представлен для инициатора в LPDDR3 (малой мощности с двойной скоростью передачи данных версия 3, исходная спецификация, опубликованная в мае 2012 компанией JEDEC). Система 102 обеспечивает полное колебание выходного напряжения для возбуждения выходного сигнала. Другие компоненты, кроме подсистем памяти, также могут использовать инициатор, который обеспечивает полное колебание выходного напряжения. Для полного колебания выходного напряжения используется существенная энергия для I/O (ввода/вывода) или взаимодействия между компонентами.

Краткое описание чертежей

Следующее описание включает в себя раскрытие чертежей, содержащих иллюстрации, приведенные в качестве примера воплощения вариантов осуществления изобретения. Чертежи следует понимать как пример, а не как ограничение. Используемые здесь ссылки на один или больше "вариантов осуществления" следует понимать, как описывающие конкретные свойства, структуры и/или характеристики, включенные, по меньшей мере, в одно воплощение изобретения. Таким образом, такие фразы как "в одном варианте осуществления" или "в альтернативном варианте осуществления", появляющиеся здесь, описывают различные варианты осуществления и воплощения изобретения и не обязательно все относятся к одному и тому же варианту осуществления. Однако они не обязательно являются взаимно исключающими.

На фиг. 1А показана блок-схема известного выходного инициатора CMOS.

На фиг. 1В показана блок-схема выходного инициатора с двойным NMOS.

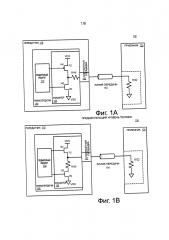

На фиг. 2 показана блок-схема варианта осуществления системы, имеющей регулятор напряжения, для уменьшения колебаний напряжения при передаче.

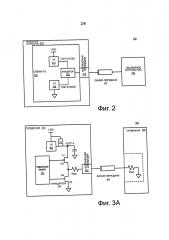

На фиг. 3А показана блок-схема варианта осуществления системы, имеющей регулятор напряжения, включенный для уменьшения колебаний напряжения относительно высокого опорного напряжения выходного сигнала.

На фиг. 3В показана блок-схема варианта осуществления системы, имеющей регулятор напряжения, включенный для уменьшения колебаний напряжения относительно низкого опорного напряжения выходного сигнала.

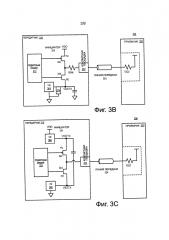

На фиг. 3С показана блок-схема варианта осуществления системы, имеющей регуляторы напряжения, включенные для уменьшения колебаний напряжения, как относительно низкого опорного напряжения, так и относительно высокого опорного напряжения выходного сигнала.

На фиг. 4 показана блок-схема варианта осуществления подсистемы памяти, имеющей систему тестирования, обеспечивающую тестирование в системе для управления колебаниями выходного напряжения.

На фиг. 5 показана блок-схема варианта осуществления контроллера памяти и подсистемы связи запоминающего устройства с регулировкой напряжения для управления колебаниями напряжения сигнала.

На фиг. 6А показана блок-схема варианта осуществления схемы импеданса с множеством выводов для подъема напряжения.

На фиг. 6В показана блок-схема варианта осуществления схемы импеданса с множеством выводов для опускания напряжения.

На фиг. 7 показана блок-схема последовательности операций варианта осуществления обработки для вывода сигнала с уменьшенными колебаниями напряжения.

На фиг. 8 показана блок-схема последовательности операций варианта осуществления обработки для эмпирического тестирования и определения установки передачи данных с использованием исчерпывающего поиска возможных значений.

На фиг. 9 показана блок-схема варианта осуществления вычислительной системы, в которой может быть выполнено управление колебаниями напряжения.

На фиг. 10 показана блок-схема варианта осуществления мобильного устройства, в котором может быть выполнено управление размахом напряжения.

Описания определенных деталей и воплощений представлены ниже, включая в себя описание чертежей, на которых могут быть представлены некоторые или все варианты осуществления, описанные ниже, а также описание других потенциальных вариантов осуществления или вариантов осуществления представленных здесь изобретательских концепций.

Осуществление изобретения

Как описано ниже, регулятор напряжения управляет колебаниями напряжения схемы интерфейса линии передачи для передачи сигналов. Схема интерфейса линии передачи представляет собой или составляет часть инициатора, который инициирует линию передачи. Схема интерфейса линии передачи включает в себя комплементарные элементы инициирования, включающие в себя элемент инициирования р-типа для подъема напряжения в линии передачи в ответ на высокий логический уровень и элемент инициирования n-типа для опускания напряжения в линии передачи в ответ на низкий логический уровень. Регулятор напряжения соединен между одним из элементов инициирования и соответствующим опорным напряжением для уменьшения колебаний напряжения в схеме интерфейса линии передачи. В одном варианте осуществления регуляторы напряжения используются как в ответвлении, поднимающем напряжение, так и в ответвлении, опускающем напряжение, в схеме интерфейса линии передачи. Таким образом, первый регулятор напряжения может быть размещен между источником высокого напряжения (VDD) и элементом подъема напряжения и второй регулятор напряжения может быть размещен между источником низкого напряжения или землей (VSS) и элементом опускания напряжения. Уменьшенный размах колебаний напряжения может быть выполнен так, чтобы он соответствовал стандартам интерфейса I/O (ввода/вывода) при уменьшении количества энергии, используемой в системах для передачи I/O.

В одном варианте осуществления операции схемой интерфейса линии передачи можно дополнительно управлять путем использования эмпирического тестирования. Система эмпирически может тестировать параметры рабочих характеристик I/O (ввода/вывода) устройства для конкретного устройства. На основе эмпирического тестирования через систему тестирования система может устанавливать рабочие параметры, специфичные для системы или устройства, в котором происходит обмен данными между устройствами. Для каждой из множества различных установок для множества разных параметров схемы I/O система тестирования устанавливает значение для каждого параметра схемы I/O, генерирует тестовый трафик для нагрузочных испытаний при передаче данных со значением (значениями) параметра и измеряет рабочий запас для рабочих характеристик I/O. Параметры цепи могут включать в себя Vref, Ron, максимальную скорость нарастания выходного напряжения, нагрузочный резистор на кристалле (ODT), выходное напряжение регулятора и/или другие параметры. Тестовая система дополнительно выполняет функцию поиска для определения значений для каждого параметра цепи I/O, при которых рабочий запас удовлетворяет минимальному пороговому значению, и рабочие характеристики, по меньшей мере, одного из параметров цепи I/O увеличиваются. В одном варианте осуществления система устанавливает значения во время работы для параметров цепи I/O на основе функции поиска. Настройки могут динамически изменяться для конкретных компонентов определенных систем на основе тестирования.

В одном варианте осуществления описанная тестовая система или тестовый механизм может использоваться для тестирования подсистем памяти, и более конкретно, для обмена данными между компонентами платформы (например, процессором, контроллером памяти) и запоминающим устройством. Любая подсистема памяти, в которой используется контроллер памяти с планировщиком или эквивалентной логикой, может воплощать, по меньшей мере, один вариант осуществления тестового механизма. Ссылка здесь может быть сделана на запоминающие устройства, которые могут включать в себя разные типы памяти. Например, в подсистемах памяти обычно используется DRAM, которое представляет собой один пример запоминающего устройства, как описано здесь. Таким образом, тестовый механизм, описанный здесь, совместимым с любой одной из многих технологий памяти, таких как DDR3 (двойная скорость передачи данных, версия 3, оригинальный выпуск JEDEC (Объединенный инженерный совет по электронным устройствам) 27 июня 2007 г., в настоящее время выпуск 21), DDR4 (DDR версии 4, исходная спецификация, опубликованная в сентябре 2012 г. JEDEC), LPDDR4 (двойная скорость передачи данных с низким потреблением энергии, версия 4, спецификация разрабатывается JEDEC на момент подачи данной заявки), WIDEIO (спецификация, развиваемая JEDEC на момент подачи данной заявки), и/или другие, и технологии на основе производных или расширений таких спецификаций.

На фиг. 1В показана блок-схема известного выходного инициатора двойного NMOS. Система 104 аналогична системе 102 на фиг. 1А, но с элементом 144 подъема напряжения n-типа и с элементом 142 опускания напряжения n-типа. Колебания выходных сигналов ниже в системе 104, чем в системе 102, поскольку элемент подъема напряжения n-типа или устройство имеет пороговое напряжение, необходимое для включения элемента 144, что уменьшает выходные колебания в результате использования комплементарной конструкции инициатора. Элементы 110, 120, R122, 130, 132, 134, 152 и 154 являются такими же, как и в системе 104, за исключением упомянутого. Выходной импеданс R148 обычно устанавливают так, чтобы он соответствовал импедансу контактной площадки 152 и линии 154 передачи, как это выглядит для инициатора 134.

Пример использования системы 104 предназначен для инициатора, для LPDDR4, в котором предложена система 104 аналогичной конструкции. Система 102 позволяет получить полное колебание выходного напряжения для возбуждения выходного сигнала, при этом используется больше энергии, чем в системе 104. Однако система 104 увеличивает padcap (емкость контактной площадки) и требует другого управления скоростью нарастания выходного напряжения, чем используется в системе 102. Таким образом, в системе интерфейса невозможно просто подключать инициатор LPDDR3 для поддержки наследуемых устройств на той же контактной площадке, соединенной с инициатором LPDDR4. Кроме того, конструкция системы 104 приводит к таким значениям подъема напряжения Ron (выходной импеданс), которое не очень хорошо управляется через PVT (обработка, напряжение и температура). Кроме того, поднятое напряжение и Ron трудно компенсировать в системе 104.

На фиг. 2 показана блок-схема варианта осуществления системы, имеющей регулятор напряжения для уменьшения колебания напряжения при передаче I/O. Система 200 включает в себя локальное устройство 210, которое связывается с удаленным устройством 220. Основное внимание в описании системы 200 направлено на передачу сигнала из локального устройства 210 в удаленное устройство 220. Локальное устройство 210 является "локальным" для схемы интерфейса линии передачи, которая возбуждает линию 240 передачи при передаче. Таким образом, при передаче из устройства 210 в устройство 220 удаленное устройство 220 является удаленным относительно схемы интерфейса линии передачи. Следует понимать, что роли двух устройств, как передатчика и приемника, могут быть обратными. Схема инициатора передачи устройств 210 и 220 не обязательно одинакова.

Локальное устройство 210 включает в себя схему 230 I/O, которая составляет интерфейсы для линий 240 передачи через контактную площадку 212. Схема 230 включает в себя инициатор 232, который управляет линией 240 передачи для связи с удаленным устройством 220. В одном варианте осуществления линия 240 передачи представляет собой сигнальную линию (например, дорожку), соединяющую выводы I/O локального устройства 210 с удаленным устройством 220. Линия 240 передачи, в качестве альтернативы, может представлять собой провод или другое взаимное соединение.

В одном варианте осуществления инициатор 232 представляет собой структуру CMOS (комплементарный металло-оксидный полупроводник) со схемой, эквивалентной элементу подъема напряжения и элементу опускания напряжения. Любой один или оба из ответвлений подъема напряжения и опускания напряжения инициатора 232 может быть соединен с соответствующим опорным напряжением через регулятор напряжения. В одном варианте осуществления регулятор напряжения предусмотрен в ответвлении подъема напряжения. В одном варианте осуществления регулятор напряжения предусмотрен в ответвлении опускания напряжения. В одном варианте осуществления регуляторы напряжения предусмотрены в обоих ответвлениях подъема и опускания напряжения. Например, ответвление подъема натяжения может быть соединено с VDD через регулятор (VR) 234 напряжения, и ответвление опускания напряжения может быть соединено с VSS через VR 236. Таким образом, эффективное логическое высокое напряжение для передачи локальным устройством 210 может составлять VDD-Vvr 234 или VDD минус величина опускания напряжения, предусмотренная в VR 234. Эффективное логически низкое значение для передачи локальным устройством 210 может составлять VSS+Vvr 236 или VSS плюс величина подъема напряжения, обеспечиваемая VR 236. Следует понимать, что изменение напряжения, предусмотренное VR 234 и VR 236, не обязательно является одинаковым. В обоих случаях колебания напряжения могли бы быть уменьшены посредством эквивалентной схемы без регулятора напряжения.

Уменьшение колебаний выходного напряжения может обеспечить экономию энергии для схемы 230 по сравнению с конструкцией, в которой колебания происходят от одной шины питания до другой шины питания. Предположим, что VR 234 включен в схему 230, обеспечивая выходное напряжение VDD-Vvr234. Если VR 234 представляет собой линейный регулятор напряжения, тогда конструкция системы 200 будет уменьшать мощность передачи в линейной зависимости относительно уменьшения напряжения, обеспечиваемого Vvr234. Если VR 234 разработан как переключающийся регулятор напряжения или переключающий схему регулятор (например, регулятор с переключением конденсаторов, регулятор с переключаемой индуктивностью), конструкция системы 200 может уменьшать мощность передачи приблизительно в квадратичной взаимосвязи с уменьшением напряжения, обеспечиваемым Vvr234. В одном варианте осуществления, как описано более подробно ниже со ссылкой на фиг. 4 и 5, точное целевое значение размаха напряжения для одного или обоих регуляторов напряжения может быть оптимизировано после изготовления фактического физического устройства, используя тренировочный поток из системы тестирования, которая позволяет выполнить поиск для уменьшения общей энергии, при поддержании определенных значений высоты и/или ширины глазковой диаграммы.

В одном варианте осуществления один или оба регулятора 234 и 236 напряжения могут быть локально интегрированы на одном и том же полупроводниковом кристалле или в интегральной схеме, как схема 230, занимая очень мало площади поверхности. Например, конструкция устройства часто имеет достаточно пустых мест для размещения варианта осуществления регулятора напряжения в схеме 230. Известны технологии для разработки линейных регуляторов, которые позволяют получить низкие затраты энергии, не требуя существенной величины уменьшения связи емкости на кристалле. В одном варианте осуществления один или оба регулятора 234 и 236 напряжения воплощены в том же корпусе или на той же плате, что и схема 230, без размещения на той же полупроводниковой подложке. Размещение регуляторов напряжения за пределами кристалла может привести к более высоким издержкам при конструировании и/или затратам при воплощении.

В одном варианте осуществления (который явно не показан) один или оба регулятора 234 и 236 напряжения можно избирательно обойти через путь обхода. Путь обхода может избирательно активироваться для переключения соединения на опорное напряжение через регулятор напряжения или соединение непосредственно с опорным напряжением. Таким образом, например, вход в регулятор и выход из регулятора могут быть соединены через избирательный (например, переключаемый) путь с низким импедансом, который позволяет выполнить обход регулятора, когда он активирован. Такая конструкция может использоваться для формирования интерфейса с разными типами систем (например, интерфейса как с LPDDR3 (с обходом для полного колебания напряжения), так и LPDDR4 (активированный регулятор для малого колебания напряжения)). Кроме того, регулятор напряжения можно отключать, если он не требуется, таким образом, чтобы принять сигнал вместо возбуждения передачи сигнала. Таким образом, при низких состояниях напряжения регулятор напряжения может удваивать энергию как затвор для энергии, и может отключать энергию для инициатора, когда он не используется, что позволяет уменьшить утечку по цепи.

На фиг. 3А показана блок-схема варианта осуществления системы, имеющей регулятор напряжения, подключенный для уменьшения размаха колебаний в отношении опорного высокого напряжения выходного сигнала. Система 302 может представлять собой один пример варианта осуществления системы 200. Передатчик 310 представляет собой локальное устройство, и приемник 320 представляет собой удаленное устройство. Для передачи приемник 320 представлен в системе 302, как импеданс R2322 нагрузки. Передатчик 310 включает в себя предварительный инициатор 332 для обеспечения управления и передачи сигналов в инициатор 334, для возбуждения и вывода сигнала передачи по линии 354 передачи через контактную площадку 352.

Инициатор 334 включает в себя элемент 342 подъема напряжения и элемент 344 опускания напряжения. Элемент 344 представляет собой элемент n-типа (например, NMOS), который опускает напряжение в линии 354 передачи для генерирования логически низкого сигнала. Элемент 342 представляет собой элемент р-типа (например, PMOS), который поднимает напряжение в линии 354 передачи для генерирования логически высокого сигнала. Следует понимать, что "логически низкий" и "логически высокий" относится к уровням напряжения, а не к протоколу связи или сигналам, используемым между устройствами 310 и 320. Например, в одной схеме передачи сигналов логически низкое напряжение может соответствовать передаче "нуля", и логически высокое напряжение может соответствовать передаче "единицы". Однако схема передачи сигналов может быть построена на обратном представлении, где логически высокое напряжение может соответствовать передаче нуля, и логически низкое напряжение может соответствовать передаче единицы.

Передатчик 310 включает в себя регулятор 362 напряжения для уменьшения уровня высокого напряжения передачи от VDD до VDDTX, которое представляет собой VDD минус падение напряжения на регуляторе 362 напряжения. В одном варианте осуществления передатчик 310 включает в себя обходной путь 372, который позволяет обходить регулятор 362 напряжения. Сглаживающий конденсатор может быть размещен между VDDTX и VSS для фильтрации шумов, которые могут быть введены регулятором 362 напряжения. Инициатор 334 включает в себя выходной импеданс, Ron, R346, включенный между комплементарными выходными элементами 342 и 344, и контактной площадкой 352. Конструкция системы 302 обеспечивает хорошо управляемые уровни Ron и выходного напряжения. Кроме того, уровни выходного напряжения могут быть настраиваемыми путем регулирования выхода регулятора 362 напряжения.

Система 302 может использоваться как воплощение схемы нагрузки VSS для низкого размаха колебания LPDDR4. Кроме того, система 302 может быть воплощена как для LPDDR3, так и для LPDDR4, например, путем избирательного обхода регулятора 362 напряжения. Таким образом, система 302 поддерживает конструкцию, представляющую комбинацию LPDDR3/4 с высокими рабочими характеристиками. В одном варианте осуществления обходной путь 372 составляет часть или воплощение регулятора 362 напряжения, что обеспечивает для регулятора возможность короткого замыкания VDD в VDDTX. Для специалиста в данной области техники будет понятно, что конструкция системы 302 не будет сильно влиять на padcap или общие характеристики передатчика 310.

Использование буфера CMOS обеспечивает присущие ему преимущества целостности сигнала, благодаря представлению постоянного импеданса Ron для контактной площадки 352. Таким образом, передатчик 310 может соответствовать характерному импедансу линии 354 передачи и может поглощать любую избыточную энергию в результате отражения. Однако путем регулирования целевого напряжения регулятора 362 напряжения, система 302 может регулировать размах колебаний, представленный приемником 320, для достижения требуемого размаха колебаний или напряжения общего режима. В результате система 302 обеспечивает независимое регулирование над размахом колебаний буфера I/O и Ron.

На фиг. 3В показана блок-схема варианта осуществления системы, имеющей регулятор напряжения, включенный для уменьшения размаха колебаний относительно низкого опорного напряжения выходного сигнала. Система 304 может представлять собой один пример варианта осуществления системы 200. Передатчик 310 представляет собой локальное устройство, и приемник 320 представляет собой удаленное устройство. С целью передачи приемник 320 представлен в системе 304 как импеданс R322 нагрузки, который может представлять собой нагрузочный резистор на кристалле VDD, напряжение общего назначения или заземление, в зависимости от конкретного воплощения. Передатчик 310 включает в себя предварительный инициатор 332 для обеспечения управления и передачи сигнала, для инициатора 334, для возбуждения и вывода или передачи сигнала по линии 354 передачи через контактную площадку 352. Инициатор 334 включает в себя элемент 342 подъема напряжения и элемент 344 опускания напряжения. Элемент 344 представляет собой элемент n-типа (например, NMOS), элемент, который выполняет опускание напряжения в линии 354 передачи для генерирования логически низкого сигнала. Элемент 342 представляет собой элемент р-типа (например, PMOS), который выполняет подъем напряжения в линии 354 передачи, для генерирования логически высокого сигнала.

Передатчик 310 включает в себя регулятор 364 напряжения для подъема передаваемого уровня низкого напряжения от VSS до VSSTX, который представляет собой VSS плюс напряжение регулятора 364 напряжения. В одном варианте осуществления передатчик 310 включает в себя обходной путь 374, который позволяет выполнять обход регулятора 364 напряжения. Сглаживающий конденсатор может быть включен от VSSTX до VSS (или от VDD, в зависимости от окружающей среды), для фильтрации шумов, которые могут быть введены регулятором 364 напряжения. Инициатор 334 включает в себя выходной импеданс, Ron, R346, включенный между комплементарными выходными элементами 342 и 344 и контактной площадкой 352. Конструкция системы 304 обеспечивает хорошо управляемые уровни Ron и выходного напряжения. Кроме того, уровни выходного напряжения можно настраивать путем регулирования выхода регулятора 364 напряжения.

На фиг. 3С показана блок-схема варианта осуществления системы, имеющая регуляторы напряжения, соединенные для уменьшения колебаний напряжения, как в отношении низкого опорного напряжения, так и в отношении высокого опорного напряжения выходного сигнала. Система 306 может представлять собой один пример варианта осуществления системы 200. Передатчик 310 представляет собой локальное устройство, и приемник 320 представляет собой удаленное устройство. Для передачи приемник 320 представлен в системе 306, как импеданс R322 нагрузки, который может составлять нагрузку для напряжения общего режима или VDD. Передатчик 310 включает в себя предварительный инициатор 332 для обеспечения управления и подачи сигналов для инициатора 334, для возбуждения и вывода сигнала передачи по линии 354 передачи через контактную площадку 352. Инициатор 334 включает в себя элемент 342 подъема напряжения и элемент 344 опускания напряжения. Элемент 344 представляет собой элемент n-типа (например, NMOS), который опускает напряжение в линии 354 передачи для генерирования низкого логического сигнала. Элемент 342 представляет собой элемент р-типа (например, PMOS), который поднимает напряжение в линии 354 передачи для генерирования высокого логического сигнала.

Передатчик 310 включает в себя регулятор 366 напряжения для понижения передаваемого напряжения высокого уровня от VDD до VDDTX, который представляет собой VDD минус падение напряжения на регуляторе 366 напряжения. В одном варианте осуществления передатчик 310 включает в себя обходной путь для обхода регулятора 366 напряжения (не представлен в явном виде). Передатчик 310 также включает в себя регулятор 368 напряжения для повышения низкого уровня напряжения передачи от VSS до VSSTX, который представляет собой VSS плюс напряжение регулятора 368 напряжения. В одном варианте осуществления передатчик 310 включает в себя обходной путь для обхода регулятора 368 напряжения (не показан в явном виде). Конденсатор может быть включен между VDDTX и VSSTX для фильтрации шумов выходного сигнала. Инициатор 334 не представлен в явном виде, как включающий в себя выходной импеданс, но выходной импеданс может быть предусмотрен. Уровни выходного напряжения инициатора 334 могут быть отрегулированы как в отношении высокого напряжения, так и в отношении низкого напряжения.

Система 306 может использоваться как вариант осуществления выходного инициатора WIDEIO, а также выходного инициатора LPDDR3 и применима для любого I/O, где колебание напряжения достигает VDD/2. Используя WIDEIO, известные конструкции генерируют на контактной площадке 352 напряжение, достигающее уровней напряжения питания (от VSS до VDD). При использовании LPDDR3 приемник ожидает общий режим VDD/2. Инициатор потребляет энергию, равную CVF (где С представляет собой емкость, V представляет напряжение и F представляет собой частоту сигнала). Стандарты JEDEC, такие как спецификация для LPDDR3 и предложенная спецификация для WIDEIO, разрешают колебания напряжения на контактной площадке от приблизительно 0,2*VDD до 0,8*VDD, так чтобы оно находилось в пределах допустимых требований. Однако в известных конструкциях напряжение достигает полного напряжения питания. Если регуляторы 366 и 368 напряжения будут установлены на 20% VDD, тогда выходное колебание напряжения все еще будет соответствовать стандартам, при уменьшении потребления энергии на 40% по сравнению с колебанием от 0 до VDD. В качестве альтернативы, регуляторы 366 и 368 напряжения могли бы быть установлены на разные значения, и не обязательно требуется устанавливать для получения равного шага напряжения. Следует понимать, что регуляторы 366 и 368 напряжения могут быть выполнены с возможностью работы симметрично (например, регулируя колебание напряжения на равные величины) для сохранения общего режима VDD/2 для приемника 320.

В варианте осуществления для WIDEIO схема приемника обычно воплощена как простой инвертор. Таким образом, потребление энергии за счет утечки увеличивается экспоненциально, когда колебания на контактной площадке 352 напряжения не достигают полного напряжения питания. Использование обходных путей для подъема напряжения на контактной площадке 352 до опорного напряжения питания (VDD или VSS) во время периодов простоя может уменьшить потребление энергии за счет утечки. Во время периодов высокой активности, когда преобладает мощность CVF, система 306 может регулировать размах выходного напряжения, уменьшая его для экономии энергии. Во время периодов простоя, когда преобладает энергии утечки, система 306 может выполнять обход регуляторов напряжения, чтобы обеспечить размах напряжения на контактной площадке 352 до полного напряжения питания, что позволяет уменьшить или устранить утечку. В одном варианте осуществления обходные пути могут быть воплощены как слабые пути подъема/понижения напряжения, для подъема напряжения на контактной площадке 352 до VDD/VSS во время периодов простоя. Обычно обходной путь может быть воплощен либо как путь с малым импедансом для обеспечения равенства выходного напряжения опорному напряжению вместо смещения регулятора напряжения, или как путь с высоким импедансом (например, силовой вентиль).

В любом варианте осуществления на любой из фиг. 3А, 3В или 3С система тестирования может дополнительно быть добавлена для программирования размаха выходного напряжения на основе конкретного изготовленного устройства (например, регулируя операцию устройства на месте установки). Таким образом, точные целевые значения VSSTX и/или VDDTx могут быть настроены системой тестирования на основе оценки высоты и/или ширины глазковой диаграммы для мощности. Несимметричное значение VSSTX и VDDTX могло бы обеспечить для системы возможность выравнивания запасов напряжения на высокой и низкой стороне, дополнительно уменьшая энергию. Такие технологии дополнительно описаны ниже.

На фиг. 4 показана блок-схема варианта осуществления подсистемы памяти, имеющей систему тестирования, которая обеспечивает тестирование в системе для управления размахом выходного напряжения. Конкретный размах выходного напряжения может быть рассчитан для определенного устройства во время работы, для определения компромиссов между высотой и/или шириной глазковой диаграммы в общей мощности. В то время как, в частности, представлена подсистема 400 памяти, следует понимать, что другая подсистема электронного устройства, в которой используется передача данных между устройствами, в равной степени может использоваться. Подсистема 400 памяти может включать в себя запоминающее устройство 410, систему 420 тестирования, логику 430 регулирования параметра, логику 440 измерения и логику 450 поиска. Такая функциональная логика может относиться к аппаратным средствам, программному обеспечению, встроенному программному обеспечению или их комбинации. Функциональная логика также может быть воплощена непосредственно в SoC (система на кристалле) или может быть удаленной и может связываться через отдельный интерфейс I/O.

Запоминающее устройство 410 представляет одно или больше устройств накопителя в подсистеме памяти. Система 420 тестирования обеспечивает тестирование передачи данных с запоминающим устройством 410 для определения, как установить рабочие параметры I/O в отношении связи с запоминающим устройством 410. Помимо других рабочих параметров I/O система 420 тестирования может определять специфичные установки регулятора напряжения для уменьшения колебания напряжения на выходе конкретного запоминающего устройства 410 (или другого приемного устройства из устройства передачи). В одном варианте осуществления система 420 тестирования включает в себя контур 422 тестирования, который представляет контур для выполнения тестирования. В частности, в одном варианте осуществления тестирование и измерение выполняются итеративно в контуре 422 для определения, как запоминающее устройство 410 работает в различных условиях. В одном варианте осуществления система 420 тестирования включает в себя логику экстраполяции (не представлена в явном виде), которая может использоваться для экстраполяции рабочей характеристики (например, рабочей характеристики в наихудшем случае) запоминающего устройства 410 на основе множества измерений для разных установок параметров. В одном варианте осуществления система 420 тестирования включает в себя логику корреляции (не показана, в частности), которая может использоваться для коррелирования множества результатов тестов друг с другом, для уменьшения или компенсации шумов в результатах тестов.

Логика 430 регулирования параметра представляет логику для изменения параметра рабочих характеристик. В одном варианте осуществления логика 430 представляет логику, которая регулирует значение регулятора напряжения или регулирует опорное напряжение для запоминающего устройства 410. Регуляторы напряжения могут включать в себя схемы переменного выхода для обеспечения переменного напряжения, для регулирования колебания выходного напряжения в ответ на логику управления. В одном варианте осуществления логика 430 представляет логику, которая регулирует один или более скрытых параметров. Например, логика 430 может регулировать электрические параметры, такие как Ron (выходной импеданс), Rodt (импеданс завершения на кристалле), скорость нарастания выходного напряжения, выравнивание, центровка по времени между стробами данных, частота или другие электрические параметры. В одном варианте осуществления логика 430 представляет логику, которая регулирует один или более параметров частоты. Например, логика 430 может регулировать параметры, относящиеся к любому из скрытых параметров, описанных выше, или к другим временным параметрам, время на отправку и возвращение или другие параметры I/O. Задержка и/или частота могут влиять на установку для регулятора напряжения.

В одном варианте осуществления логика 430 регулирования параметра составляет часть контроллера памяти, и влияет на установки конфигурации в контроллере памяти, которые управляют задержкой. В одном варианте осуществления логика 430 существует за пределами контроллера памяти, например в механизме тестирования, рядом с контроллером памяти. В одном варианте осуществления логика 430 обеспечивает регулировку контроллером памяти установок в самом запоминающем устройстве, такую как варианты конфигурации установок. В одном варианте осуществления логика 430 регулировки параметра может регулировать частоту, на которой работает подсистема памяти с мелким размером шага гранулярности. Система 420