Усовершенствование интерфейса pci express

Иллюстрации

Показать всеИзобретение относится к технологиям сетевой связи. Технический результат заключается в повышении скорости передачи данных. Устройство обработки данных содержит логическую схему ввода/вывода для: идентификации, что канал передачи данных должен выйти из активного состояния, причем канал передачи данных содержит множество линий; поддержки информации о четности для указанных линий на основе данных, ранее переданных по каналу передачи данных, и передачи указания информации о четности перед выходом из активного состояния. 4 н. 21 з.п. ф-лы, 19 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к компьютерным системам, в частности (но не исключительно) к соединениям точка-точка.

Уровень техники

Достижения в области технологии полупроводниковых приборов и в проектировании логических устройств позволили увеличить объем логических устройств, которые могут быть размещены в одной интегральной схеме. Как следствие, произошло развитие конфигураций компьютерных систем от одной или более интегральных схем до систем с множеством ядер, множеством аппаратных потоков и множеством логических процессоров в одной индивидуальной интегральной схеме, равно как и других интерфейсов, интегрированных в таких процессорах. Процессор или интегральная схема обычно содержит один физический процессорный кристалл, где этот процессорный кристалл может содержать произвольное число ядер, аппаратных потоков, логических процессоров, интерфейсов, запоминающих устройств, контроллеров-концентраторов и т.п.

В результате возросших возможностей вместить больше процессорных мощностей в корпуса меньшего размера выросла популярность малогабаритных компьютерных устройств. Численность и сфера применения смартфонов, планшетов, ультратонких ноутбуков и других пользовательских устройств росли экспоненциально. Однако эти малогабаритные устройства зависят от серверов как для хранения данных, так и для осуществления сложной обработки данных, для которой не хватает возможностей, ограниченных форм-фактором малогабаритных устройств. Следовательно, потребности в создании рынка высокопроизводительных вычислений (т.е. в серверном пространстве) тоже выросли. Например, современный сервер обычно содержит не только один многоядерный процессор, но и несколько физических процессоров (также называемых несколькими сокетами) для увеличения вычислительной мощности. Но по мере роста процессорных мощностей вместе с числом устройств в компьютерной системе связь между сокетами и другими устройствами становится все более критичной.

На деле технология соединений между устройствами прошла путь развития от более традиционных многоотводных шин, осуществлявших преимущественно электрическую связь, до полностью развитой полнофункциональной архитектуры соединений, способствующей осуществлению высокоскоростной связи. К сожалению, по мере роста требований к процессорам будущего работать на все более высоких скоростях, соответствующие требования предъявляются и к возможностям существующих архитектур соединений.

Краткое описание чертежей

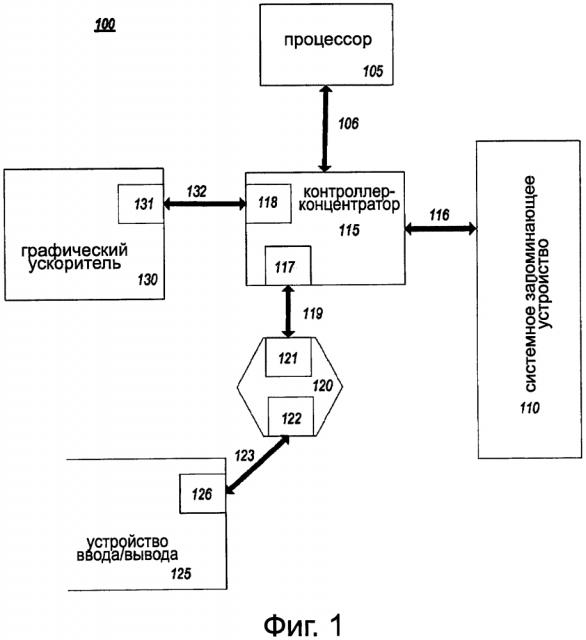

Фиг. 1 иллюстрирует вариант компьютерной системы, содержащей архитектуру соединений.

Фиг. 2 иллюстрирует вариант архитектуры соединений, содержащей многоуровневый стек.

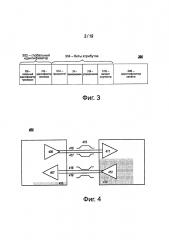

Фиг. 3 иллюстрирует вариант запроса или пакета, какие следует генерировать или принимать в архитектуре соединений.

Фиг. 4 иллюстрирует варианты пары из передатчика и приемника для архитектуры соединений.

Фиг. 5 иллюстрирует вариант примера канала для соединения между двумя разъемами.

Фиг. 6 представляет упрощенную блок-схему соединительной структуры, имеющей сквозные соединения, в разрезе.

Фиг. 7 представляет соединение в разрезе с использованием «высверливания» столбиков сквозных соединений сзади.

Фиг. 8 представляет блок-схему структуры возможностей, включая регистр состояния ошибки линии.

Фиг. 9 представляет упрощенную схему, иллюстрирующую потоки данных в много линейном соединении.

Фиг. 10 показывает представление примера символов кадрирующего маркера.

Фиг. 11 представляет упрощенную схему, иллюстрирующую потоки данных, включая пример упорядоченного множества пропуска (SKP).

Фиг. 12 представляет упрощенную схему, иллюстрирующую ошибки линии, сообщение о которых может быть передано в регистр ошибок.

Фиг. 13A-13D представляют логические схемы, иллюстрирующие примеры передачи сообщений об ошибках линий канала связи.

Фиг. 14 иллюстрирует вариант блок-схемы компьютерной системы, содержащей многоядерный процессор.

Фиг. 15 иллюстрирует другой вариант блок-схемы компьютерной системы, содержащей многоядерный процессор.

Фиг. 16 иллюстрирует вариант блок-схемы процессора.

Фиг. 17 иллюстрирует другой вариант блок-схемы компьютерной системы, содержащей процессор.

Фиг. 18 иллюстрирует вариант блок-схемы компьютерной системы, содержащей несколько процессоров.

Фиг. 19 иллюстрирует пример системы, реализованной в виде системы на кристалле (SoC).

Подобные цифровые и иные позиционные обозначения на разных чертежах указывают подобные элементы.

Осуществление изобретения

В последующем описании приведены многочисленные конкретные детали, такие как примеры конкретных типов процессоров и конфигурации систем, конкретные структуры аппаратуры, конкретные архитектурные и микроархитектурные подробности, конкретные конфигурации регистров, конкретные типы команд, конкретные компоненты систем, конкретные размеры/высоты, конкретные ступени процессорных конвейеров и операций и т.п., с целью предоставления возможности полного понимания настоящего изобретения. Однако специалисту в рассматриваемой области должно быть понятно, что эти конкретные детали не обязательно использовать при практической реализации настоящего изобретения. В других случаях хорошо известные компоненты или способы, такие как конкретные и альтернативные процессорные архитектуры, конкретные логические схемы/коды для описываемых алгоритмов, конкретные коды встроенного программного обеспечения, конкретные соединительные операции, конкретные логические конфигурации, конкретные способы изготовления и материалы, конкретные варианты реализации компилятора, конкретные выражения алгоритмов в виде кода, конкретные способы/логические устройства для выключения питания/стробирования и другие конкретные подробности работы компьютерных систем здесь не были описаны подробно, чтобы избежать нежелательного загромождения и «затемнения» описания настоящего изобретения.

Хотя последующие варианты могут быть описаны с точки зрения энергосбережения и энергетической эффективности конкретных интегральных схем, таких как компьютерные платформы или микропроцессоры, другие варианты применимы к другим типам интегральных схем и логических устройств. Способы и принципы, аналогичные описываемым здесь вариантам, могут быть применены к другим типам схем или полупроводниковых приборов, которые также могут выиграть от лучшей энергетической эффективности и сбережения энергии. Например, описываемые варианты не ограничиваются настольными компьютерными системами или компьютерами типа Ultrabooks™. Они могут быть также использованы в других устройствах, таких как ручные устройства, планшеты, другие тонкие ноутбуки, системы на кристалле (system on а chip (SOC)) и встроенные приложения. В качестве некоторых примеров ручных устройств можно указать сотовые телефоны, устройства Интернет-протокола, цифровые фото и видеокамеры, персональные цифровые помощники (personal digital assistants (PDA)) и ручные персональные компьютеры. Встроенные приложения обычно содержат микроконтроллер, цифровой процессор сигнала (digital signal processor (DSP)), систему на кристалле, сетевые компьютеры (network computers (NetPC)), приставки, сетевые концентраторы, коммутаторы глобальной сети связи (wide area network (WAN)) или какие-либо другие системы, которые могут осуществлять функции и операции, рассматриваемые ниже. Более того, аппаратура, способы и системы, рассматриваемые здесь, не ограничиваются физическими компьютерными устройствами, а могут также относиться к программным оптимизациям с целью сбережения энергии и энергетической эффективности. Как станет легко понятно из приведенного ниже описания, варианты способов, аппаратуры и систем, описываемые здесь (будь то со ссылками на аппаратуру, встроенное программное обеспечение, загружаемое программное обеспечение или сочетания этих компонентов) являются жизненно важными для так называемой «зеленой технологии» будущего, сбалансированной с учетом соображений производительности.

По мере совершенствования компьютерных систем компоненты таких систем становятся все более сложными. В результате сложность архитектуры соединений для связи между компонентами также возрастает, чтобы удовлетворить требованиям к широкополосности связи для оптимальной работы компонентов. Более того, разные сегменты рынка требуют различных аспектов архитектуры соединений для удовлетворения разных потребностей рынка. Например, от серверов требуется высокая производительность, тогда мобильная экосистема иногда может пожертвовать общей производительностью в пользу энергосбережения. До сих пор единственным требованием к большинству систем соединений являлось достижение наивысшей возможной производительности при максимальном энергосбережении. Ниже обсуждаются некоторые системы соединений, которые потенциально должны были бы выиграть от некоторых аспектов настоящего изобретения, рассматриваемых здесь.

Одна из архитектур соединений содержит архитектуру соединений периферийных устройств Peripheral Component Interconnect (PCI) Express (PCIe). Основной целью архитектуры PCIe является обеспечение возможности для компонентов и устройств от разных поставщиков взаимодействовать в открытой архитектуре, охватывая несколько сегментов рынка: а именно Клиентов (Client) (настольных (Desktop) и мобильных (Mobile)), Серверов (Server) (обычных (Standard) и серверов предприятий (Enterprise)), а также встроенных (Embedded) устройств и устройств связи (Communication). Стандарт интерфейса PCI Express представляет собой стандарт высокопроизводительной системы соединений ввода/вывода общего назначения, созданный для самого широкого спектра компьютерных платформ и платформ связи будущего. Некоторые атрибуты интерфейса PCI, такие как модель использования, архитектура загрузки-хранения и программные интерфейсы, были сохранены во всех редакциях этого интерфейса, тогда как прежняя параллельная реализация шины была заменена в высокой степени масштабируемым полностью последовательным интерфейсом. Более новые версии интерфейса PCI Express используют достижения в области двухпунктовых соединений, технологии на основе коммутации и протокола передачи пакетов данных для достижения новых, более высоких уровней производительности и характеристик. Среди усовершенствованных характеристик интерфейса PCI Express можно указать управление питанием (Power Management), управление качеством обслуживания (Quality Of Service (QoS)), поддержку «горячего» подключения в рабочем состоянии (Hot-Plug) и «горячей» замены в рабочем состоянии (Hot-Swap) устройств, обеспечение целостности данных (Data Integrity) и обработку ошибок (Error Handling).

На Фиг. 1 представлен вариант архитектуры соединений, составленной из каналов связи точка-точка, соединяющих множество компонентов. Система 100 содержит процессор 105 и системное запоминающее устройство ПО, соединенные с контроллером-концентратором 115. Процессор 105 содержит какой-либо процессорный элемент, такой как микропроцессор, главный процессор, встроенный процессор, сопроцессор или какой-либо другой процессор. Процессор 105 соединен с контроллером-концентратором 115 посредством внешней шины (front-side bus (FSB)) 106. В одном из вариантов шина FSB 106 представляет собой последовательное двухпунктовое соединение, как описано ниже. В другом варианте канал 106 связи содержит последовательную дифференциальную архитектуру соединений, совместимую с другим стандартом соединений.

Системное запоминающее устройство 110 представляет собой запоминающее устройство какого-либо типа, такое как запоминающее устройство с произвольной выборкой (RAM), энергонезависимое запоминающее устройство (non-volatile (NV) memory) или какое-нибудь другое запоминающее устройство, доступное для других устройств в системе 100. Системное запоминающее устройство 110 связано с контроллером-концентратором 115 через интерфейс 116 памяти. Среди примеров таких интерфейсов памяти можно указать интерфейс памяти с удвоенной скоростью передачи данных (double-data rate (DDR)) двухканальный DDR-интерфейс памяти и интерфейс памяти для динамического (DRAM).

В одном из вариантов контроллер-концентратор 115 представляет собой корневой концентратор, корневой комплекс или корневой контроллер в иерархии соединений Peripheral Component Interconnect Express (PCIe или PCIE). К примерам таких контроллеров-концентраторов 115 относятся чипсет, контроллер-концентратор памяти (МСН), схема «Северный мост» (northbridge), контроллер-концентратор соединений (ICH), схема «Южный мост» (southbridge) и корневой контроллер/концентратор. Часто термин «чипсет» относится к двум физически раздельным контроллерам-концентраторам, т.е. к контроллеру-концентратору памяти (МСН), связанному с контроллером-концентратором соединений (ICH). Отметим, что современные системы часто содержат блок МСН, интегрированный с процессором 105, тогда как контроллер 115 предназначен для связи с устройствами ввода/вывода аналогично тому, как описано ниже. В некоторых вариантах корневым комплексом 115 в качестве опции поддерживается одноранговая маршрутизация.

Здесь контроллер-концентратор 115 соединен с коммутатором/мостом 120 посредством последовательного канала 119 связи. Модули 117 и 121 ввода/вывода, которые могут также называться интерфейсами/портами 117 и 121, содержат/реализуют многоуровневый стек протоколов для осуществления связи между контроллером-концентратором 115 и коммутатором 120. В одном из вариантов с коммутатором 120 могут быть соединены несколько устройств.

Коммутатор/мост 120 осуществляет маршрутизацию пакетов/сообщений от устройства 125 «вверх», т.е. вверх по иерархии по направлению к корневому комплексу, к контроллеру-концентратору 115 и «вниз», т.е. вниз по иерархии прочь от корневого контроллера, от процессора 105 или системного запоминающего устройства 110 к устройству 125. Коммутатор 120 в одном из вариантов называется логической сборкой из нескольких виртуальных мостовых устройств PCI-k-PCI/. Устройство 125 содержит какое-либо внутреннее устройство или компонент для соединения с электронной системой. Это устройство или компонент может представлять собой устройство ввода/вывода, контроллер сетевого интерфейса (Network Interface Controller (NIC)), расширительную плату, аудио процессор, сетевой процессор, накопитель на жестком диске, запоминающее устройство, накопитель CD/DVD ROM, монитор, принтер, мышь, клавиатуру, маршрутизатор, портативное запоминающее устройство, устройство с шиной сверхбыстрой передачи данных (Firewire), устройство с универсальной последовательной шиной (Universal Serial Bus (USB)), сканер или другое устройство ввода/вывода. Часто на жаргоне PCIe такое устройство называется конечной или крайней точкой. Хотя это не показано специально, устройство 125 может содержать мост для соединения PCIe с PCI/PCI-X с целью поддержки PCI-устройств, соответствующих прежним устаревшим или другим версиям. Устройства конечных точек в системах PCIe часто классифицируют как прежние, устаревшие конечные точки, конечные точки PCIe или интегральные конечные точки корневого комплекса.

С контроллером-концентратором 115 по последовательному каналу 132 связи соединен также графический ускоритель 130. В одном из вариантов графический ускоритель 130 соединен с блоком МСН, который связан с блоком ICH. Коммутатор 120 и соответственно устройство 125 ввода/вывода затем соединены с блоком ICH. Модули 131 и 118 ввода/вывода также реализуют многоуровневый стек протоколов для осуществления связи между графическим ускорителем 130 и контроллером-концентратором 115. Аналогично обсуждавшемуся выше блоку МСН графический контроллер или графический ускоритель 130 сам может быть интегрирован в процессор 105.

На Фиг. 2 показан вариант многоуровневого стека протоколов. Этот многоуровневый стек 200 протоколов может содержать какую-либо форму многоуровневого стека связи, такую как стек шины быстрого соединения (Quick Path Interconnect (QPI)), стек PCIe, стек высокопроизводительных компьютерных соединений следующего поколения или другой многоуровневый стек. Хотя приведенное непосредственно ниже со ссылками на Фиг. 1-4 обсуждение относится к стеку PCIe, те же самые принципы могут быть применены и к другим стекам соединений. В одном из вариантов стек 200 протоколов является PCIe-стеком протоколов, содержащим уровень 205 транзакций, канальный уровень 210 и физический уровень 220. Интерфейс, такой как интерфейсы 117, 118, 121, 122, 126 и 131, может быть представлен в виде стека 200 протоколов связи. Представление в виде стека протоколов связи может также называться модулем или интерфейсом, реализующим/содержащим стек протоколов.

Интерфейс PCI Express использует пакеты для передачи информации между компонентами. Пакеты формируются на уровне 205 транзакций (Transaction Layer) и на уровне 210 канала передачи данных или канальном уровне (Data Link Layer) для переноса информации от передающего компонента к приемному компоненту. Когда передаваемые пакеты проходят через другие уровни, происходит расширение этих пакетов за счет добавления дополнительной информации, необходимой для обработки пакетов на этих уровнях. На приемной стороне осуществляется обратный процесс и происходит преобразование пакетов от представления, которое они имели на физическом уровне 220 (Physical Layer) к представлению на канальном уровне 210 и, в конце концов (для пакетов уровня транзакций) к форме, в которой эти пакеты могут быть обработаны на уровне 205 транзакций в приемном устройстве.

Уровень транзакций

В одном из вариантов уровень 205 транзакций служит интерфейсом между процессорным ядром устройства и архитектурой соединений, такой как канальный уровень 210 и физический уровень 220. С этой точки зрения главной сферой ответственности уровня 205 транзакций является сборка и разборка пакетов (т.е. пакетов уровня транзакций (transaction layer packet) или TLP). Уровень 205 транзакций обычно осуществляет управление потоком на кредитной основе для пакетов TLP. Интерфейс PCIe осуществляет расщепленные транзакции, т.е. транзакции, для которых запрос и ответ разделены во времени, что позволяет каналу связи передавать другой трафик, пока целевое устройство собирает данные для ответа.

Кроме того, интерфейс PCIe использует управление потоком на кредитной основе. При использовании такой схемы устройство объявляет первоначальный объем кредита для каждого из приемных буферов на уровне 205 транзакций. Внешнее устройство на противоположном конце канала связи, такое как контроллер-концентратор 115, показанный на Фиг. 1, подсчитывает число кредитов, израсходованных каждым пакетом TLP. Любая транзакция может быть передана, только если она не превышает кредитный лимит. После приема ответа объем кредита восстанавливается. Преимущество такой кредитной схемы состоит в том, что задержка возврата кредита не влияет на производительность при условии, что кредитный лимит не достигнут.

В одном из вариантов совокупность четырех адресных пространств транзакций содержит адресное пространство конфигурации, адресное пространство памяти, адресное пространство ввода/вывода и адресное пространство сообщений. К транзакциям в пространстве памяти относятся один или несколько запросов считывания и запросов записи для передачи данных в/из позиций памяти. В одном из вариантов транзакции в пространстве памяти могут использовать два разных формата адресов, например, короткий адресный формат, такой как 32-битовые адреса, или длинный адресный формат, такой как 64-битовые адреса. Транзакции в пространстве конфигурации используются для доступа в пространство конфигурации PCIe-устройств. Транзакции в пространстве конфигурации содержат запросы считывания и запросы записи. Транзакции в пространстве сообщений (или просто сообщения) определены для поддержки передачи данных через сеть между PCIe-агентами.

Поэтому в одном из вариантов уровень 205 транзакций собирает заголовок/полезную нагрузку пакета 206. Формат для заголовков/полезной нагрузки пакетов, действующий на сегодня, можно найти в спецификациях интерфейса PCIe на веб-сайте спецификаций PCIe.

Фиг. 3 иллюстрирует один из вариантов дескриптора транзакции для интерфейса PCIe. В одном из вариантов дескриптор 300 транзакции представляет собой механизм для передачи информации о транзакции. В этом смысле дескриптор 300 транзакции поддерживает идентификацию транзакций в системе. Среди других потенциальных областей использования дескриптора можно указать отслеживание модификаций порядка транзакций по умолчанию и ассоциирование транзакций с каналами.

Дескриптор 300 транзакции содержит поле глобального идентификатора 302, поле 304 атрибутов и поле идентификатора 306 канала. В иллюстрируемом примере показано, что поле глобального идентификатора 302 содержит поле локального идентификатора 308 транзакции и поле идентификатора 310 источника. В одном из вариантов глобальный идентификатор 302 транзакции является уникальным для всех ожидающих выполнения запросов.

Согласно одному из вариантов поле локального идентификатора 308 транзакции представляет собой поле идентификатора, генерируемого запросившим агентом и являющегося уникальным для всех невыполненных запросов, которые нуждаются в выполнении, от этого запросившего агента. Более того, в этом примере идентификатор 310 источника однозначно идентифицирует запросившего агента в иерархии PCIe. Соответственно, вместе с идентификатором 310 источника поле локального идентификатора 308 транзакции обеспечивает глобальную идентификацию транзакции в иерархической области.

Поле 304 атрибутов определяет характеристики и взаимосвязи транзакции. С этой точки зрения поле 304 атрибутов потенциально используется для предоставления дополнительной информации, которая позволяет модифицировать обработку транзакций по умолчанию. В одном из вариантов поле 304 атрибутов содержит поле 312 приоритета, зарезервированное поле 314, поле 316 упорядочения и поле 318 запрета снупинга (несанкционированного вмешательства). Здесь субполе 312 приоритета может быть модифицировано инициатором, чтобы назначить приоритет транзакции. Зарезервированное поле 314 атрибута остается в резерве на будущее или для использования в целях, заданных поставщиком. С применением этого зарезервированного поля атрибутов могут быть реализованы возможные модели использования, применяющие атрибуты приоритета или безопасности.

В этом примере поле 316 атрибута упорядочения используется для передачи информации об опциях, которая несет тип упорядочения и которая может модифицировать правила упорядочения по умолчанию. Согласно одному из примеров реализации атрибут упорядочения, равный "0", обозначает, что следует применять правила упорядочения по умолчанию, тогда как атрибут упорядочения, равный "1", обозначает ослабленные правила упорядочения, где операции записи могут проходить по записям в одном и том же направлении, и завершения считывания могут проходить по записям в одном и том же направлении. Поле 318 атрибута снупинга используется для определения, производится ли снупинг транзакций. Как показано, поле идентификатора 306 канала обозначает канал, с которым ассоциирована транзакция.

Канальный уровень

Канальный уровень 210, также именуемый уровнем 210 канала передачи данных, служит промежуточным уровнем между уровнем 205 транзакций и физическим уровнем 220. В одном из вариантов ответственность уровня 210 канала передачи данных состоит в создании надежного механизма обмена пакетами уровня транзакций (Transaction Layer Packet (TLP)) между двумя компонентами канала связи. Одна сторона уровня 210 канала передачи данных принимает пакеты TLP, собранные уровнем 205 транзакций, присваивает идентификатор 211 последовательности пакетов, т.е. идентификационный номер или номер пакета, вычисляет и применяет код контроля ошибок, т.е. циклически избыточный контрольный код CRC 212, и передает модифицированные пакеты TLP на физический уровень 220 для передачи по физическим линиям связи внешнему устройству.

Физический уровень

В одном из вариантов физический уровень 220 содержит логический субблок 221 и электрический субблок 222 для физической передачи пакета внешнему устройству. Здесь логический субблок 221 отвечает за «цифровые» функции физического уровня 220. Для этого логический субблок содержит передающую секцию для подготовки исходящей информации к передаче посредством физического субблока 222 и приемную секцию для идентификации и подготовки принятой информации перед тем, как передать ее на канальный уровень 210.

Физический блок 222 содержит передатчик и приемник. Передатчик получает символы от логического субблока 221, преобразует эти символы в последовательную форму и передает внешнему устройству. Приемник получает преобразованные в последовательную форму символы от внешнего устройства и преобразует принятые сигналы в поток битов данных. Этот поток битов данных преобразуют из последовательной формы и передают логическому субблоку 221. В одном из вариантов используется код передачи 8b/10b, где передают/принимают 10-битовые символы. Здесь специальные символы используются для разбиения пакета на кадры 223. Кроме того, в одном из примеров приемник генерирует также тактовый сигнал символов, выделенный из входящего последовательного потока данных.

Как указано выше, хотя уровень 205 транзакций, канальный уровень 210 и физический уровень 220 обсуждаются здесь применительно к конкретному варианту стека протоколов PCIe, многоуровневый стек протоков этим не ограничивается. На деле, здесь может быть включен/реализован любой многоуровневый протокол. В качестве примера, порт/интерфейс, представленный в виде многоуровневого протокола, содержит: (1) первый уровень для сборки пакетов, т.е. уровень транзакций; второй уровень для выстраивания последовательности пакетов, т.е. канальный уровень; и третий уровень, для передачи пакетов, т.е. физический уровень. В качестве конкретного примера используется многоуровневый протокол общего стандартного интерфейса (common standard interface (CSI)).

Далее, на Фиг. 4 показаны последовательные двухпунктовые соединения согласно стандарту PCIe. Хотя здесь показан вариант последовательного двухпунктового канала согласно стандарту PCIe, само условие последовательного двухпунктового канала не является столь уж ограничивающим, поскольку оно охватывает любой передающий тракт, позволяющий передавать последовательные данные. В показанном варианте базовый канал связи интерфейса PCIe содержит две пары устройств для работы с низковольтными дифференциальными сигналами: пару передатчиков 406/411 и пару приемников 412/407. Соответственно, устройство 405 содержит передающую логическую схему 406 для передачи данных устройству 410 и приемную логическую схему 407 для приема данных от устройства 410. Другими словами, в канал связи интерфейса PCIe входят два передающих тракта, т.е. тракты 416и417, и два приемных тракта, т.е. тракты 418 и 419.

Передающим трактом называется любой тракт для передачи данных, такой как линия передачи, медный провод, оптическая линия передачи, канал радиосвязи, инфракрасная линия связи или другой тракт связи. Соединение между двумя устройствами, такими как устройство 405 и устройство 410, называется каналом связи, таким как канал 415 связи. Канал связи может поддерживать одну линию - где каждая линия представляет набор пар дифференциальных сигналов (одна пара для передачи и одна пара для приема). Для масштабирования полосы канал связи может агрегировать несколько линий, обозначенных xN, где N - какая-либо поддерживаемая ширина канала, такая как 1, 2, 4, 8, 12, 16, 32, 64 или шире.

Дифференциальная пара обозначает два передающих тракта, таких как проводники 416 и 417, для передачи дифференциальных сигналов. В качестве примера, когда проводник 416 переключается с низкого уровня напряжения на высокий уровень, т.е. происходит восходящий перепад уровней, проводник 417 переходит с высокого логического уровня на низкий логический уровень, т.е. имеет место нисходящий перепад уровней. Дифференциальные сигналы потенциально демонстрируют лучшие электрические характеристики, такие как лучшая целостность сигнала, т.е. меньше перекрестные связи, меньше положительные/отрицательные выбросы напряжения, меньше «звон» и т.д. Это позволяет лучше определить временное окно синхронизации и, тем самым, дает возможность использовать более высокие частоты передачи.

Высокоскоростной канал

Новой редакцией спецификаций ввода/вывода для интерфейса PCIe является стандарт PCIe редакция 4.0 (или PCIe 4.0). При скорости 16 ГТ/с (Гигатранзакций/с) (GT/s) интерфейс PCIe 4.0 имеет целью удвоить полосу соединения по сравнению со стандартом PCIe 3.0, сохраняя при этом совместимость с программными и механическими интерфейсами. Расширение рабочей полосы по сравнению с интерфейсами PCIe предшествующих поколений может обеспечить масштабирование производительности, согласованное с потребностями расширения полосы со стороны разнообразных вновь разрабатываемых приложений, и при этом нацелено на достижение небольшой стоимости, небольшой потребляемой мощности и минимальных возмущений на уровне платформы. Одним из основных факторов широкого применения архитектуры PCIe является ее чувствительность к возможностям массового производства и соответствующим материалам, таким как недорогие печатные платы, дешевые разъемы и т.д.

Скорость передачи данных 16 ГТ/с направлена на достижение оптимального компромисса между производительностью, технологичностью, стоимостью, мощностью и совместимостью. Для выработки рекомендаций о характеристиках для устройств и каналов связи, поддерживающих скорость передачи данных 16 ГТ/с для интерфейса PCIe 4.0, был проведен анализ реализуемости. Анализ PCI-SIG охватывал множество топологий. Например, анализ определил, что достижение скорости 16 ГТ/с при использовании медных проводников, что должно удвоить ширину полосы по сравнению с возможностями интерфейса PCIe 3.0, технически реализуемо при приблизительно таких же уровнях мощности, какие используют интерфейсы PCIe 3.0. Здесь соединения со скоростью передачи данных 16 ГТ/с потенциально могут быть изготовлены с применением типовой кремниевой технологии и развернуты с использованием существующих недорогих материалов и инфраструктуры при сохранении совместимости с архитектурами PCIe предшествующих поколений.

Системы с последовательным вводом/выводом и высокой скоростью передачи данных (например, 16 ГТ/с согласно стандарту PCIe 4.0) должны рассеивать значительную мощность и обладать повышенной сложностью схем, что потенциально ведет к увеличению используемой площади кремния (Si). Эти соображения в перспективе имеют потенциал ограничить интеграцию интерфейсов стандарта PCIe 4.0 (и других подобных высокоскоростных архитектур соединений) в центральные процессоры CPU и системы, использующие увеличенное число линий. В некоторых примерах реализаций, например, ограничения накладываются на длину соединений и число соединителей, используемых в высокоскоростной архитектуре, такой как PCIe 4.0. Например, такое ограничение определено на уровне спецификаций. В одном из примеров, длина соединительного канала связи ограничена одним (1) соединителем и двенадцатью (12) или меньшим числом дюймов.

Наложение ограничений на соединительные каналы связи может ограничить их применимость в некоторых системах. Например, в серверных соединительных приложениях соединения платформы могут достигать в длину двадцать (20) дюймов и более и иметь два соединителя. Если архитектура ограничивает соединительные каналы связи максимальной длиной 12 дюймов и наличием только одного соединителя, придется вводить отдельный кристалл ретранслятора или другое дополнительное устройство для соединения двух каналов по 12 дюймов и адаптации к расстояниям между устройствами, присущим серверной системе, это среди потенциально других примерах.

В некоторых вариантах реализации может быть организован соединительный канал связи, конфигурированный в соответствии со стандартом интерфейса PCIe 4.0 и другими соединениями, допускающий создание имеющего два соединителя канала длиной не меньше двадцати дюймов и при этом все еще поддерживающего скорости передачи данных 16 ГТ/с. Например, схема и соединение могут быть совместно оптимизированы таким образом, чтобы можно было исключить ретрансляторы и другие устройства из более длинных «пролетов» соединительных каналов. Это может помочь снизить производственные затраты, уменьшить задержку ввода/вывода и расширить область применения более широкополосных архитектур с повышенной скоростью на новые, дополнительные приложения. Например, кристалл ретранслятора может содержать передатчик, приемник, тактовый генератор (например, контур фазовой автоподстройки частоты (phase lock loop (PLL))), схему выделения тактового сигнала и ассоциированные функции. Такие компоненты могут использовать ценную площадь на плате. Кроме того, в соединении х16 PCIe 4.0 каждый ретранслятор может рассеивать дополнительную мощность и вносить дополнительные затраты при изготовлении системы, среди прочих потенциальных недостатков. Например, ретрансляторы могут также вносить дополнительную задержку ввода/вывода.

На Фиг. 5 показан пример конфигурации канала связи с двумя соединителями. Например, канал 500 может содержать несколько секций, таких как секции сокета (например, центрального процессора CPU), материнскую плату, расширительную плату, надстроечную плату среди других элементов, через которые может проходить канал связи для соединения двух устройств (например, 505, 510) в системе. Каждая секция канала может иметь свою длину, в этом примере длины секций равны L1=1ʺ, L2=10.5ʺ, L3=0.5ʺ, L4=4ʺ, L5=3ʺ и L6=lʺ, всего 20ʺ для полной длины канала 500. Этот канал связи может быть соединен с каждым из устройств 505, 510 с использованием соответствующего соединителя 515, 520 (в каждом корпусе).

При использовании традиционных способов конфигурация, такая как показана на Фиг. 5, может дать отрицательный запас по всему каналу связи. В одном из примеров может быть создан имеющий два соединителя канал связи длинной 20ʺ, поддерживающий скорость 16 ГТ/с передачи данных (например, 500), минимизирующий эффект столбиков сквозных соединений, минимизирующий эффект сокетов серверных процессоров (SPU), использующий усовершенствованные и обладающие небольшими потерями платы персональных компьютеров (personal computer board (РСВ)) и обеспечивающий увеличение усиления входного блока выполненного на кристалле приемника среди потенциально других признаков, для реализации положительного коэффициента усиления по длине канала связи.

Соединитель может содержать одно или более сквозных соединений, используемых для создания электрических соединений между слоями. Сквозные соединения могут быть использованы, например, для передачи сигналов или питания между слоями печатной платы или компонента. В высокоскоростных системах часть такого сквозного соединения остается поверх соединителя, кристалла или платы, так что эта часть не используется в двухпунктовом канале электрической связи, проходящем через это сквозное соединение. На Фиг. 6 показано упрощенное представление 600 одного или нескольких столбиковых сквозных соединений 605, 610. Сквозное соединение может создать электрические соединения между слоями печатной платы, например, с использованием технологии металлизированных сквозных отверстий (plated through hole (РТН)). Например, сквозные соединения могут электрически соединять штырьки соединителей с внутренними сигнальными слоями (например, дорожками). В примере, показанном на Фиг. 6, часть канала связи может быть реализована с использованием участка (например, 615, 620) металлизированного сквозного отверстия (РТН) для соединения одного отрезка канала связи с другим (например, дорожки (например, 625), проходящей в слое 630 рассматриваемого компонента к другому компоненту, другому сквозному соединению и т.п. по каналу связи). Остальная часть (например, 635) сквозного соединения может считаться столбиком. В высокоскоростных соединениях с использованием сквозных соединений столбик 635 в составе сквозного соединения может создавать резонансные эффекты (например, нули на резонансных частотах), что ведет к деградации сигнала в канале связи (например, в линии). Соответственно, в некоторых вариантах столбики в составе сквозных соединений могут быть «высверлены», как показано поз. 650, чтобы ослабить указанные эффекты. «Высверливание» столбиков в сквозных соединений мож