Способ измерения относительного временного сдвига импульсов и устройство его реализующее

Иллюстрации

Показать всеИзобретение относится к области радиоизмерений и позволяет измерять временные сдвиги, возникающие между последовательностями импульсов с равными или малоотличающимися периодами следования, например между исходной последовательностью и задержанной. Находят оценку временного сдвига путем формирования и измерения временного интервала, равного измеряемому временному сдвигу, границы которого определяются положением передних фронтов импульсов, относительный временной сдвиг которых оценивается. До формирования вышеуказанного временного интервала измеряют период Т следования импульсов, далее расширяют импульсы до величины, не превышающей измеренный период Т, после чего формируют временной интервал между передними фронтами расширенных импульсов путем выполнения логической операции «неоднозначность». Технический результат заключается в повышении точности измерений. 3 н. и 1 з.п. ф-лы, 3 ил.

Реферат

Изобретение относится к области радиоизмерений и позволяет измерять временные сдвиги, возникающие между последовательностями импульсов с равными или малоотличающимися периодами следования, например между исходной последовательностью и задержанной.

Классический способ измерения относительного временного сдвига импульсов, принятый за прототип, предусматривает формирование временного интервала, равного измеряемому временному сдвигу, границы которого определяются положением передних фронтов импульсов, относительный временной сдвиг которых оценивается, причем началом упомянутого временного интервала считается момент появления первого импульса, концом - момент появления следующего импульса, а оценкой служит результат измерения полученного временного интервала [см., например, Метрология и радиоизмерения/ Под ред. В.И. Нефедова. - М.: Высшая школа, 2003, стр. 302-311].

Существенным недостатком способа является то, что опережающим импульсом считается не импульс из опережающей последовательности, а первый появившийся импульс из любой последовательности, как опережающей, так и запаздывающей. Это приводит к появлению абсолютной ошибки измерения, в ряде случаев близкой к периоду следования импульсов Т, что считается недопустимой погрешностью.

Устройство, реализующее способ в обобщенном виде, на функциональном уровне, содержит фазовый детектор, в простейшем случае RS-триггер или логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, и измеритель временных интервалов, входами устройства являются входы фазового детектора, а выходом - выход измерителя временных интервалов, вход которого соединен с выходом фазового детектора [Соловов В.Я. Фазовые измерения. - М.: Энергия, 1973, стр. 28, рис. 1-13]. Недостатки устройства предопределены особенностями способа: в общем случае устройство обладает невысокой точностью.

Технический результат, достигаемый при использовании настоящего изобретения, состоит в повышении точности измерений за счет исключения ошибки, связанной с нарушением порядка поступления информационных импульсов.

Технический результат достигается тем, что в способе измерения относительного временного сдвига импульсов, согласно которому оценку временного сдвига находят путем формирования и измерения временного интервала, равного измеряемому временному сдвигу, границы которого определяются положением передних фронтов импульсов, относительный временной сдвиг которых оценивается, согласно изобретению до формирования вышеуказанного временного интервала измеряют период Т следования импульсов, далее расширяют импульсы до величины, не превышающей измеренный период Т, после чего формируют временной интервал между передними фронтами расширенных импульсов путем выполнения логической операции «неоднозначность».

Кроме того, для достижения технического результата в устройство для измерения относительного временного сдвига импульсов, содержащее фазовый детектор и измеритель временных интервалов, выход которого является выходом устройства, а вход соединен с выходом фазового детектора, согласно изобретению введены измеритель периода и два расширителя импульсов, входы первого и второго расширителей импульсов являются соответственно первым и вторым информационными входами устройства, выходы первого и второго расширителей импульсов соединены соответственно с первым и вторым входами фазового детектора, выход измерителя периода соединен с управляющими входами расширителей импульсов, а вход с любым из информационных входов устройства.

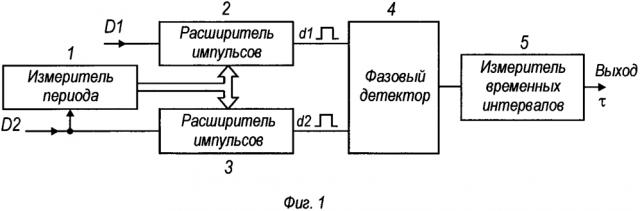

Сущность изобретения поясняется графическим материалом. На фиг. 1 представлена функциональная схема устройства, на фиг. 2 показаны временные диаграммы, поясняющие принцип измерений, а на фиг. 3 - функциональная схема расширителя импульсов.

Функциональная схема по фиг. 1 содержит измеритель 1 периода, расширители 2, 3 импульсов, фазовый детектор 4 и измеритель 5 временных интервалов, выход которого является выходом устройства, входами D1 и D2 устройства являются информационные входы расширителей 2, 3 импульсов соответственно, выходы которых соединены со входами фазового детектора 4, выход которого соединен со входом измерителя 5 временных интервалов, управляющие входы расширителей 2, 3 объединены и подключены к выходу измерителя 1 периода, вход которого объединен со входом D2.

Временные диаграммы (фиг. 2) содержат последовательности импульсов D1 и D2 на входах устройства, следующие с периодом Т и относительным временным сдвигом τ, последовательности импульсов d1 и d2 на выходах расширителей 2, 3 импульсов и импульсы на выходе фазового детектора (Выход ФД).

Функциональная схема по фиг. 3 содержит D-триггер 6, элемент И 7, счетчик 8, компаратор 9 двоичных кодов и регистр 10, вход которого является управляющим входом расширителя, информационным входом которого является тактовый вход D-триггера 6, выход которого соединен с первым входом элемента И 7, второй вход которого является тактовым входом CLK расширителя, выход элемента И 7 соединен со счетным входом счетчика 8, выход которого соединен с первым входом компаратора 9, второй вход которого соединен с выходом регистра 10, обнуляющие входы D-триггера 6 и счетчика 8 объединены и подключены к выходу компаратора 9, D-вход D-триггера 6 является входом логической единицы, выходом расширителя является выход D-триггера 6.

Суть предложенного способа проиллюстрируем, рассматривая работу устройства (см. фиг. 1). Входные импульсы D1 и D2 с относительным временным сдвигом τ и периодом Т перед поступлением на входы фазового детектора 4 расширяются в расширителях 2, 3 до величины, которая определяется по результатам измерения периода Т (см. фиг. 2). После чего в фазовом детекторе 4 выделяется информация о временном сдвиге, представляемая в виде импульса длительностью τ, которая определяется измерителем 5 временных интервалов (предполагается, что погрешностью преобразования в фазовом детекторе можно пренебречь). Необходимость предварительного расширения входных импульсов вызвана следующими причинами. Допустим, импульсы, которые могут быть произвольной длительности, поступают на входы фазового детектора в исходном виде, без расширения. Положим, что первым поступил не импульс u1, а импульс u2, то есть импульс из запаздывающей последовательности (см. левую часть фиг. 2). В этом случае обычный фазовый детектор, например на RS-триггере, определит временной сдвиг между поступающими импульсами не как τ, а как τу, формируя в полном соответствии с алгоритмом своей работы выходной импульс длительностью τу. Причем τу=Т-τ, следовательно, абсолютная погрешность определения длительности составит ⎢Т-2τ⎢, а относительная погрешность δ, как это несложно видеть: , которая при больших Т может привести к достаточно серьезным ошибкам. Типичный случай - это оценка расхождения шкал времени: при оценке временного сдвига последовательностей секундных синхронизирующих импульсов (Т=1 с) и максимально допустимом временном сдвиге τ, не превышающем сотен наносекунд, относительная погрешность может быть около 107. Что, строго говоря, следует считать уже не погрешностью, а артефактом. Однако применяемые на практике измерители не выделяют артефакты, так как это не предусматривается принципом их функционирования. В то же время операция предварительного расширения импульсов, приводящая к их перекрытию во времени, позволяет исключить принятие фазовым детектором импульса u2 за первый (опережающий), так как в это же время будет действовать расширенный импульс u1, что легко видеть из графиков, показанных на фиг. 2. Следовательно, если считать, что фазовое детектирование сводится к распространенной в подобных схемах логической операции «неравнозначность», то ошибка исключается на алгоритмическом уровне.

Перекрытие импульсов во времени, показанное на фиг. 2 в виде заштрихованных участков, должно осуществляться при любых временных сдвигах τ. Это обеспечивается при принудительном расширении импульсов до значения Т/2. В этом случае импульсы d1 и d2 будут перекрываться как в диапазоне изменения τ от 0 до T/2, так и при изменении от Т/2 до Т. При τ=Т/2 перекрытия не будет, если считать, что импульсы прямоугольные. Однако при указанном значении τ перекрытия импульсов не требуется, так как на произвольно выбранном отрезке времени при τ=Т/2, если нет априорной информации о знаке временного рассогласования сигналов, учитывая периодический характер последовательностей, определить какая из них опережающая, а какая запаздывающая, невозможно. При этом сдвиг любого импульса из одной последовательности относительно соседних импульсов другой последовательности будет одинаковым как слева, так и справа. В этом случае фазовый детектор не может неверно сформировать выходной импульс. При дальнейшем увеличении относительного сдвига, то есть при τ>Т/2, импульсы начинают перекрываться, но временной сдвиг, определяемый как расстояние по оси времени t от переднего фронта первого импульса слева до переднего фронта ближайшего импульса справа, будет уменьшаться и соответственно уменьшится длительность импульса на выходе фазового детектора 4. То есть оценкой τ будет величина, меньшая T/2. Это несложно увидеть из временных диаграмм, показанных в правой части фиг. 2. Указанное полностью соответствует характеристике классического фазового детектора, реализуемого на логическом элементе ИСКЛЮЧАЮЩЕЕ ИЛИ (операция «неоднозначность»), более подробно см. [Аванесян Г.Р. Цифровые интегральные микросхемы. - М.: Радиотехника, 2008, стр. 250-251].

Фазовый детектор вышеупомянутого типа, работающий с сигналами со скважностью, равной двум («меандр»), выдает на выходе по два импульса на период, как показано на фиг. 2. Однако «вторые» импульсы, показанные на фиг. 2 штриховыми линиями, следует использовать для последующих измерений с обязательным учетом того, что их длительность равна τ+(t2-t1), здесь t2 и t1 - длительности импульсов соответственно второй (d2) и первой (d1) последовательностей. В общем случае следует исходить из того, что во «вторые» импульсы вносится дополнительная погрешность, численно равная модулю разности длительностей импульсов: ⎢t2-t1⎢. Указанная погрешность может возникать по причине неидеальной идентичности параметров расширителей 2 и 3.

На практике нередко приходится измерять с высокой точностью временные сдвиги между последовательностями импульсов значительно меньшие (на несколько порядков) их периода. В этом случае, если априори известно, что временной сдвиг не превысит значения τmах, входные информационные импульсы целесообразно расширять до τmax. В ряде случаев это может существенно упростить аппаратную часть измерителей.

Существенной операцией способа является измерение периода Т, что необходимо для корректного расширения входных импульсов. Строго говоря, измеритель 1 периода совместно с управляемыми расширителями импульсов служит для преобразования входных импульсных последовательностей с произвольной скважностью, в последовательности типа «меандр». Расширители 2, 3 импульсов идентичны, служат для получения импульсов с равными длительностями и могут быть построены по схеме, показанной на фиг. 3. Принцип действия расширителя достаточно прост: по переднему фронту импульса на входе D-триггер 6 переходит в состояние логической единицы на выходе, в связи с чем на счетный вход счетчика 8 начинают поступать счетные импульсы с выхода элемента И 7, при этом текущий код на разрядных выходах счетчика 8 сравнивается в компараторе 9 с кодом, хранящимся в буферном регистре 10. В момент равенства кодов D-триггер 6 обнуляется и таким образом на выходе указанного триггера формируется импульс, длительность которого задается кодом, хранящимся в регистре 10. В указанный регистр информация поступает с выхода измерителя 1 периода. Поскольку импульсы на выходе расширителя должны иметь длительность, вдвое меньшую периода Т, то разумно предположить, что на вход регистра 10 (управляющий вход расширителя) следует подавать код величины T/2. Такое возможно, но потребует дополнительных аппаратурных и/или вычислительных затрат на выполнение относительно сложной арифметической операции деления. Более интересным и рациональным как с практической, так и с теоретической точек зрения является другой подход: на вход регистра 10 подают код величины Т, но частоту счетных импульсов CLK, определяющую скорость наращивания кода на выходе счетчика 8, увеличивают в два раза по отношению к частоте счетных импульсов, которые использовались при измерении периода. Это эквивалентно уменьшению значения кода на входе регистра 10 в два раза. Убедиться в этом несложно, если положить, что временной интервал Т, измеряемый с дискретом Δt1 в блоке 1, представлен кодом числа N=T/Δt1±1 (для упрощения последующих записей положим, что дискрет Δt1 выбран таким образом, что T/Δt1>>1 и, следовательно, ошибкой в виде единицы младшего разряда можно пренебречь). В то же время в расширителе импульсов при периоде следования счетных импульсов Δt2 формируемый временной интервал TX связан с кодом N следующим образом: ТX=NΔt2, следовательно, при

или, учитывая, что N=Т/Δt1

Последняя запись устанавливает простую количественную связь между измеренным периодом Т и длительностью импульсов ТX на выходе расширителей. Для реализации показанного целесообразно использовать единый для блоков 1-3 генератор тактовых (счетных) импульсов, частота которого в измерителе 1 делится в два раза (на функциональной схеме по фиг. 1 единые цепи синхронизации не показаны).

Касаясь вопроса реализации измерителя 1 периода, заметим, что особые требования, кроме выше предложенного единого тактирования, к нему не предъявляются, он может быть построен по известным схемам. Обновление информации на выходе измерителя 1 периода целесообразно подтверждать импульсом с его выхода, который может быть использован как синхроимпульс, подаваемый на тактовый вход регистра 10 (на схеме не показан).

Представленные способ и устройство свободны от недостатка, свойственного прототипу, и позволяют полностью исключить ошибку определения относительного временного сдвига, вызванную нарушением порядка поступления информационных импульсов. Некоторое алгоритмическое усложнение по сравнению с прототипом достаточно просто реализуется в цифровом базисе, поскольку все основные дополнительные операции осуществляются во временной области.

1. Способ измерения относительного временного сдвига импульсов, согласно которому оценку временного сдвига находят путем формирования и измерения временного интервала, равного измеряемому временному сдвигу, границы которого определяются положением передних фронтов импульсов, относительный временной сдвиг которых оценивается, отличающийся тем, что до формирования вышеуказанного временного интервала измеряют период Т следования импульсов, далее расширяют импульсы до величины, не превышающей измеренный период Т, после чего формируют временной интервал между передними фронтами расширенных импульсов путем выполнения логической операции «неоднозначность».

2. Способ по п. 1, отличающийся тем, что импульсы расширяют до величины, равной T/2.

3. Устройство для измерения относительного временного сдвига импульсов, содержащее фазовый детектор и измеритель временных интервалов, выход которого является выходом устройства, а вход соединен с выходом фазового детектора, отличающееся тем, что в него введены измеритель периода и два расширителя импульсов, входы первого и второго расширителей импульсов являются соответственно первым и вторым информационными входами устройства, выходы первого и второго расширителей импульсов соединены соответственно с первым и вторым входами фазового детектора, выход измерителя периода соединен с управляющими входами расширителей импульсов, а вход с любым из информационных входов устройства.

4. Расширитель импульсов для применения в устройстве по п. 3, отличающийся тем, что содержит D-триггер, элемент И, счетчик, компаратор двоичных кодов и регистр, вход которого является управляющим входом расширителя, информационным входом которого является тактовый вход D-триггера, выход которого соединен с первым входом элемента И, второй вход которого является тактовым входом расширителя, выход элемента И соединен со счетным входом счетчика, выход которого соединен с первым входом компаратора, второй вход которого соединен с выходом регистра, обнуляющие входы D-триггера и счетчика объединены и подключены к выходу компаратора, D-вход D-триггера является входом логической единицы, выходом расширителя является выход D-триггера.