Широкополосное приемопередающее устройство с программной перестройкой фазы сигнала

Иллюстрации

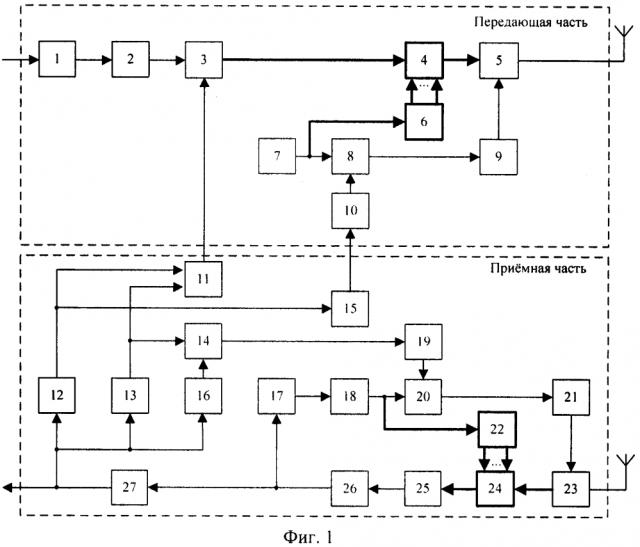

Показать всеИзобретение относится к области беспроводной связи, в частности к цифровой радиосвязи, и предназначено для использования в системах передачи информации посредством помехозащищенных сигналов с многофазной манипуляцией. Технический результат заключается в повышении помехозащищенности формируемого радиосигнала в условиях воздействия имитационных помех за счет псевдослучайного изменения фазы сигнала. Широкополосное приемопередающее устройство состоит из передающей и приемной частей дополнительно в передающую часть устройства введен блок управления фазовым сдвигом (БУФС) (4), информационный вход которого подключен к выходу высокочастотного ключа (3), а управляющие входы соединены с соответствующими выходами дешифратора (6). Вход дешифратора (6) подключен к выходу генератора псевдослучайной последовательности (7), выход БУФС (4) подключен к первому входу частотного смесителя (5). В приемную часть устройства дополнительно введен БУФС (24), информационный вход которого подключен к выходу смесителя (23), а управляющие входы соединены с соответствующими выходами дешифратора (22), вход которого подключен к выходу генератора псевдослучайной последовательности (18), а выход БУФС (24) подключен к входу усилителя промежуточной частоты (25). 1 з.п. ф-лы, 2 ил.

Реферат

Заявленное устройство относится к электросвязи, а именно к цифровой радиосвязи, и может быть использовано в системах передачи информации посредством помехозащищенных сигналов с программной перестройкой фазы сигнала.

Известно широкополосное приемопередающее устройство, осуществляющее передачу сообщений в режиме программной перестройки рабочей частоты (ППРЧ), патент РФ №2185029 от 10.07.2002 г. Данное устройство содержит на передающей стороне: кодер, блок синхронизации, генератор псевдослучайной последовательности (ПСП), блок управления, синтезатор частот, модулятор, усилитель мощности, передающую антенну, преобразователь ПСП. На приемной стороне: приемную антенну, входной усилитель, смеситель-гетеродин, детектор, блок автоматической регулировки усиления, решающее устройство, декодер, блок синхронизации, генератор ПСП, блок управления, преобразователь псевдослучайной последовательности.

Недостатком данного аналога является относительно низкая помехозащищенность в условиях воздействия преднамеренных помех, имитирующих структуру радиосигнала.

Известно широкополосное устройство с ППРЧ, патент РФ №2210187 от 10.08.2003 г., содержащее: смеситель, полосовой фильтр, амплитудный детектор, решающий блок, управляемый генератор тактовой частоты, перестраиваемый синтезатор частот (генератор кода).

Недостатком данного аналога является низкая помехозащищенность при воздействии имитационных помех.

Наиболее близким по технической сущности к заявленному устройству является широкополосное приемопередающее устройство с повышенной помехоустойчивостью, патент РФ №2296420 от 27.03.2007 г. Данное устройство выбрано в качестве прототипа.

Известное устройство-прототип содержит на передающей стороне кодер, первый фазовый манипулятор, второй фазовый манипулятор, первый высокочастотный ключ, второй высокочастотный ключ, элемент «НЕ», сумматор, смеситель, частотный синтезатор, управляемый ключ, генератор псевдослучайной последовательности, генератор управления ключом.

Вход кодера является информационным входом устройства. Выход кодера подключен параллельно к первому фазовому манипулятору и второму фазовому манипулятору, а их выходы соединены с первым и вторым входами сумматора через первый и второй высокочастотные ключи соответственно. Вход первого канала соединен со вторым входом первого высокочастотного ключа и через элемент «НЕ» со вторым входом второго высокочастотного ключа, выход сумматора соединен с первым входом смесителя, второй вход которого подключен к выходу частотного синтезатора, вход которого через управляемый ключ, соединен с выходом генератора псевдослучайной последовательности. Второй (управляющий) вход управляемого ключа соединен с выходом генератора управления ключом, вход которого соединен с приемной частью, а выход смесителя соединен с передающей антенной.

В приемной части устройство содержит смеситель, усилитель промежуточной частоты, демодулятор, первый и второй фазовые детекторы, первый и второй ключи, элемент «НЕ», элемент «ИЛИ», декодер, дешифратор команды изменения скорости, анализатор качества канала, дешифратор квитанции, блок формирования сообщения, блок памяти, линию задержки, блок синхронизации, генератор псевдослучайной последовательности, генератор управления ключом, управляемый ключ, частотный синтезатор.

Приемная антенна соединена с первым входом смесителя, выход последнего подключен к входу усилителя промежуточной частоты, выход которого соединен с входом демодулятора. Первый выход демодулятора одновременно подключен к входам элемента «НЕ» декодера и блока синхронизации. Второй и третий выходы демодулятора подключены соответственно к входам первого и второго фазовых детекторов, выходы которых соединены с первым и вторым входами элемента «ИЛИ», через первый и второй ключи соответственно. Второй вход второго ключа соединен с выходом элемента «НЕ». Выход элемента «ИЛИ» является информационным выходом второго канала.

Выход декодера подключен одновременно к входам дешифратора команды изменения скорости, анализатору качества канала и дешифратору квитанции. Выход дешифратора команды изменения скорости подключен к первому входу блока формирования сообщения и к входу линии задержки, выход которой подключен к входу генератора управления ключом передающей части.

Выход анализатора качества канала подключен ко второму входу блока формирования сообщения и первому входу блока памяти, второй вход которого соединен с выходом дешифратора квитанции, а выход соединен с входом генератора управления ключом, выход последнего подключен к управляющему входу управляемого ключа, частотный вход которого через генератор псевдослучайной последовательности и блок синхронизации подключен к первому выходу демодулятора, а выход через частотный синтезатор подключен ко второму входу смесителя. Выход блока формирования сообщения подключен к входу первого канала передающей части.

Устройство-прототип позволяет вести передачу и прием сообщений в условиях помех с заданным качеством в условиях преднамеренных ответных помех. Недостатком прототипа является относительно низкая помехозащищенность к воздействию имитационных помех.

Целью изобретения является разработка широкополосного приемопередающего устройства, обеспечивающего повышение помехозащищенности формируемого радиосигнала в условиях воздействия имитационных помех за счет псевдослучайного изменения фазы сигнала.

Для достижения указанного технического результата в известном широкополосном приемопередающем устройстве, состоящем из передающей части, приемной части и содержащем на передающей стороне кодер (1), вход которого является информационным входом устройства, а выход подключен к фазовому манипулятору (2). Выход фазового манипулятора (2) подключен к первому входу высокочастотного ключа (3), причем выходом передающей части устройства является выход частотного смесителя (5), второй вход которого соединен с выходом частотного синтезатора (9).

Вход частотного синтезатора (9) подключен к выходу высокочастотного ключа (8), на первый вход которого подключен выход генератора псевдослучайной последовательности (7), а второй вход соединен с генератором управления ключом (10), выход частотного смесителя (5) соединен с передающей антенной.

В приемной части приемная антенна соединена с первым входом смесителя (23), выход усилителя промежуточной частоты (25) соединен с входом демодулятора (26), выход которого подключен к входам блока синхронизации (17) и декодера (27), а выход декодера (27) является выходом приемной части устройства и подключен к входам дешифратора изменения скорости (12), анализатора качества канала (13), дешифратора квитанции (16).

Выход дешифратора квитанции (16) подключен к второму входу блока памяти (14), первый вход которого соединен с выходом анализатора качества канала (13) и первым входом блока формирования сообщения (11), второй вход которого подключен к выходу дешифратора команды изменения скорости (12) и к входу линии задержки (15). Причем выход блока формирования сообщения (11) соединен со вторым входом высокочастотного ключа (3) передающей части, выход линии задержки (15) подключен к входу генератора управления ключом (10) передающей части, а выход блока памяти (14) соединен с входом генератора управления ключом (19), выход которого подключен к второму входу высокочастотного ключа (20).

Первый вход высокочастотного ключа (20) через генератор псевдослучайной последовательности (18) соединен с выходом блока синхронизации (17), а выход высокочастотного ключа (20) подключен к входу частотного синтезатора (21), выход которого соединен с вторым входом частотного смесителя (23). Дополнительно в передающую часть устройства введен блок управления фазовым сдвигом (БУФС) (4), информационный вход которого подключен к выходу высокочастотного ключа (3), а управляющие входы соединены с соответствующими выходами дешифратора (6). Вход дешифратора (6) подключен к выходу генератора псевдослучайной последовательности (7), выход БУФС (4) подключен к первому входу частотного смесителя (5).

В приемную часть устройства дополнительно введен БУФС (24), информационный вход которого подключен к выходу смесителя (23), а управляющие входы соединены с соответствующими выходами дешифратора (22), вход которого подключен к выходу генератора псевдослучайной последовательности (18), а выход БУФС (24) подключен к входу усилителя промежуточной частоты (25).

БУФС (4(24)) состоит из управляемых ключей (4.1(24.1))-(4.N (24.N)), фазовращателей (4,m(24.m))-(4.М (24.М)), причем первый вход управляемого ключа (4.1(24.1)) и входы фазовращателей (4.m (24.m))-(4.M(24.M)) объединены и являются информационным входом БУФС (4 (24)), а выходы фазовращателей (4.m (24.m))-(4.М(24.М)) подключены к первым входам управляемых ключей (4.2 (24.2))-(4.N (24.N)) соответственно. Вторые входы управляемых ключей (4.1 (24.1))-(4.N (24.N)) являются управляющими входами БУФС (4(24)), выходы управляемых ключей (4.1 (24.1))-(4.N (24.N)) объединены и являются выходом БУФС (4 (24)). Значения N, m, М выбираются исходя из количества значений фазы формируемого сигнала. Величина N численно равна количеству значений фазы формируемого сигнала, m=N+1, M=2N-1.

Благодаря новой совокупности существенных признаков за счет преобразования схемы и введения новых блоков приемной и передающей частей устройства появляется возможность имитации функционирования радиолинии сигналами ФМ-N при фактическом использовании более помехоустойчивого радиосигнала двухпозиционной модуляции ФМ-2. Заявляемое устройство поясняется чертежами, на которых показаны:

фиг. 1 - структурная схема широкополосного приемопередающего устройства с программной перестройкой фазы сигнала;

фиг. 2 - схема блока управления фазовым сдвигом.

Заявленное устройство, показанное на фиг.1, состоит из передающей части и приемной части и содержит в передающей части кодер (1), вход которого является информационным входом устройства, а выход подключен к фазовому манипулятору (2), выход которого подключен к первому входу высокочастотного ключа (3).

Выход высокочастотного ключа (3) подключен к информационному входу БУФС (4), управляющие входы которого подключены к соответствующим выходам дешифратора (6), вход которого подключен к выходу генератора псевдослучайной последовательности (7). Выход БУФС (4) подключен к первому входу частотного смесителя (5), выход которого является выходом передающей части устройства. К выходу частотного смесителя (5) подключена передающая антенна.

Вход (2) частотного смесителя (5) соединен с выходом частотного синтезатора (9), вход которого подключен к выходу высокочастотного ключа (8), на первый вход которого подключен выход генератора псевдослучайной последовательности (7), а второй вход соединен с генератором управления ключом (10).

В приемной части устройства приемная антенна соединена с первым входом частотного смесителя (23), выход которого подключен к информационному входу БУФС (24), управляющие входы которого подключены к соответствующим выходам дешифратора (22). Вход дешифратора (22) подключен к выходу генератора псевдослучайной последовательности (18).

Выход БУФС (24) соединен с входом усилителя промежуточной частоты (25), выход которого соединен с входом демодулятора (26), выход которого подключен к входам блока синхронизации (17) и декодера (27). Выход декодера (27) является выходом приемной части устройства и подключен к входам дешифратора изменения скорости (12), анализатора качества канала (13), дешифратора квитанции (16).

Выход дешифратора квитанции (16) подключен к второму входу блока памяти (14), первый вход которого соединен с выходом анализатора качества канала (13) и первым входом блока формирования сообщения (11), второй вход которого подключен к выходу дешифратора команды изменения скорости (12) и к входу линии задержки (15). Причем выход блока формирования сообщения (11) соединен с вторым входом высокочастотного ключа (3) передающей части устройства.

Выход линии задержки (15) подключен к входу генератора управления ключом (10) передающей части устройства, а выход блока памяти (14) соединен с входом генератора управления ключом (19), выход которого подключен к второму входу (2) высокочастотного ключа (20). Причем первый вход высокочастотного ключа (20) через генератор псевдослучайной последовательности (18) соединен с выходом блока синхронизации (17), а выход высокочастотного ключа (20) подключен к входу частотного синтезатора (21), выход которого соединен с вторым входом частотного смесителя (23).

БУФС (4(24)) состоит из управляемых ключей (4.1 (24.1))-(4.N (24.N), фазовращателей (4.m (24.m))-(4.M (24.M)), причем первый вход управляемого ключа (4.1 (24.1)) и входы фазовращателей (4.m (24.m))-(4.M (24.М)) объединены и являются информационным входом БУФС (4 (24)), а выходы фазовращателей (4.m (24.m))-(4.M (24.M)) подключены к первым входам управляемых ключей (4.2 (24.2))-(4.N (24.N)) соответственно. Вторые входы управляемых ключей (4.1 (24.1))-(4.N (24.N)) являются управляющими входами БУФС (4(24)), выходы управляемых ключей (4.1 (24.1))-(4.N (24.N)) объединены и являются выходом БУФС (4 (24)).

Кодер (1) предназначен для преобразования входной информационной последовательности импульсов в выходную последовательность с дополнительной кодовой избыточностью, позволяющей в декодере (27), служащем для восстановления исходной информационной последовательности, исправлять ошибки, появляющиеся из-за помех, в частотном канале. Варианты реализации кодера (1) и декодера (27) известны и приведены, например, в [1], стр. 323-330, рис. 8.16.

Фазовый манипулятор (2) предназначен для формирования фазоманипулированного сигнала (ФМ-2). Фазовый манипулятор (2) известен и может быть реализован по схеме, представленной в работе [2], стр. 119, рис. 4.25.

Высокочастотный ключ (3), предназначен для подключения к тракту передачи информационной последовательности с блока формирования сообщения (11). Схема реализации высокочастотного ключа (3) известна и описана, например, в [9], с. 372-401.

БУФС (4(24)) состоит из управляемых ключей (4.1 (24.1))-(4.N (24.N)), фазовращателей (4.m (24.m))-(4.M (24.M)) и предназначен для формирования случайного значения сдвига текущей фазы сигнала на величину, кратную сдвигу фазы сигнала ФМ-N.

Фазовращатели (4.m (24.m))-(4.M (24.M)) БУФС (4 (24)) предназначены для сдвига фазы сигнала на случайную величину, кратную 2π/N. Фазовращатели (4.m (24.m))-(4.M (24.M)) известны, их схемотехническая реализация представлена, например, в [7], стр. 35-42.

Варианты реализации управляемых ключей (4.1 (24.1))-(4.N (24.N)) известны и представлены, например, в [11], с. 161-162.

В качестве частотных смесителей (5) и (23) могут быть использованы выпускаемые промышленностью смесители, используемые, например, в радиостанциях комплекса Р-168.

Дешифратор (6 (22)) предназначен для выдачи управляющего сигнала, формируемого на основе случайной последовательности генератора псевдослучайной последовательности (7 (18)) на соответствующий управляющий вход БУФС (4 (24)). Структура дешифраторов (6), (22) является известной и может быть реализована на основе структурной схемы [8], стр. 19, рис. 22, с использованием микросхем К155ИД4.

Генераторы псевдослучайной последовательности (7) и (18) предназначены для формирования одинаковых на передающей (7) и приемной (18) сторонах радиолинии последовательностей равновероятных номеров частот в диапазоне i=1,2, …, I. В качестве генераторов ПСП (7), (18) можно использовать любой генератор ПСП, производимый промышленностью, например генератор ПСП, используемый в радиостанциях комплекса Р-168.

Высокочастотные ключи (8) и (20) предназначены для коммутации генераторов ПСП (7) и (18) соответственно на вход частотных синтезаторов (9) и (21) соответственно для передачи цифровой последовательности, в соответствии с которой частотные синтезаторы (9) и (21) генерируют рабочие частоты. Схемы реализации высокочастотных ключей (8) и (20) известны и описаны в [9], с. 372-401.

Частотные синтезаторы (9) и (21) служат для формирования несущего колебания согласно последовательности генератора псевдослучайной последовательности. Вариант реализации частотных синтезаторов (9) и (21) известен и представлен, например, в [6], стр. 214, рис. 7.7 (а).

Генераторы управления ключом (10) и (19) представляют из себя генератор импульсов с регулируемой частотой генерации и служат для генерации импульсов, поступающих на вход высокочастотных ключей (8) и (20) соответственно. Частота генерации импульсов может быть увеличена в случае браковки канала. В качестве генератора управления ключом (10), (19) можно использовать любой генератор с изменяющейся частотой импульсов, например, описанный в патенте РФ №2133076 от 10.07.1999 г.

Блок формирования сообщения (11) предназначен для формирования цифрового кода, обозначающего изменение скорости переключения частоты, при подаче импульса на вход (1) и формирования цифрового кода, обозначающего квитанцию, при подаче импульса на вход (2). Структурная схема блока формирования сообщения (11) известна и описана в патенте РФ №2296420 от 27.03.2007 г.

Дешифратор команды изменения скорости (12) предназначен для преобразования цифрового кода, сформированного в блоке формирования сообщения (11) приемной части корреспондента «Б», в сигнал для перестройки частоты генерирования импульсов управления в генераторе управления ключом (10) предающей части устройства. Схема дешифратора (12) описана, например, в [4], стр. 47, рис. 2.4.

Анализатор качества канала (13) предназначен для контроля качества рабочего канала. Оценка рабочего канала производится по отношению уровней полезного сигнала и помех. В качестве анализатора качества канала (13) можно взять анализатор канала, применяемый в аппаратуре Р-163-АР [4].

Блок памяти (14) предназначен для формирования при поступлении импульсов на входы (1) и (2) управляющего импульса, поступающего на вход генератора управления ключом (19). Структурная схема блока памяти (14) известна и описана в патенте РФ №2296420 от 27.03.2007 г.

Линия задержки (15) предназначена для задержки сигнала на изменение скорости перестройки частоты на время передачи сообщения корреспонденту. В качестве линии задержки (15) можно использовать выпускаемые промышленностью линии задержки с требуемым временем задержки. Схемы линий задержки представлены в [10], с. 20.

Дешифратор квитанции (16) предназначен для дешифрации цифрового кода, означающего, что корреспондент получил команду на изменение скорости перестройки частоты. В качестве дешифратора квитанции (16) можно использовать дешифратор, аналогичный дешифратору команды изменения скорости (12).

Блок синхронизации (17) служит для формирования тактовой последовательности импульсов с периодом следования T/2, где Т - длительность работы радиолинии на одной частоте. Вариант реализации блока синхронизации (17) известен и описан, например, в [1], стр. 193, рис. 5-19.

Усилитель промежуточной частоты (25) предназначен для усиления принятого радиосигнала на промежуточной частоте до величины, необходимой для работы последующих блоков приемного тракта. Вариант реализации усилителя промежуточной частоты (25) известен и описан, например, в [5], стр. 100, рис. 3-3.

Демодулятор (26) может быть реализован по известным схемам, представленным, например, в [3].

Устройство фиг. 1 функционирует следующим образом. Дискретные сигналы поступают на вход кодера (1), преобразуются в информационную последовательность импульсов с дополнительной кодовой избыточностью и с выхода кодера (1) поступают на вход фазового манипулятора (2), на выходе которого формируется сигнал ФМ-2.

Сформированный сигнал ФМ-2 через высокочастотный ключ (3) поступает на информационный вход БУФС (4). В БУФС (4) осуществляется случайный сдвиг мгновенной фазы сигнала ФМ-2 на величину, кратную значению 2π/N. Для этого на одном из управляющих входов БУФС (4) формируется значение напряжения логической единицы, которое через соответствующий управляемый ключ (4.1)-(4.N) БУФС (4) подключает одну из ветвей БУФС. Сигнал логической единицы формируется дешифратором (6) посредством преобразования кода псевдослучайной последовательности, поступающего с выхода генератора псевдослучайной последовательности (7).

С выхода БУФС (4) сформированный сигнал, имитирующий сигнал ФМ-N, поступает на первый вход частотного смесителя (5), на второй вход которого подается перестраиваемое по псевдослучайной программе опорное колебание рабочей частоты с выхода частотного синтезатора (9), управляемого с помощью генератора псевдослучайной последовательности (7). Код псевдослучайной последовательности переключается на частотный синтезатор (9) через ключ (8). При этом частотный синтезатор (9) формирует опорное колебание рабочей частоты передачи по псевдослучайной программе из совокупности I частот, выделенных для связи, со скоростью перестройки, которая может быть изменена по команде приемной части. Изменение скорости перестройки частотного синтезатора осуществляется с помощью высокочастотного ключа (8), первый вход которого подключен к выходу генератора псевдослучайной последовательности (7), второй вход подключен к выходу генератора управления ключом (10), а выход подключен к входу частотного синтезатора (9).

Таким образом, на выходе частотного смесителя (5) формируется широкополосный сигнал в режиме ППРЧ с сдвигом мгновенного значения фазы сигнала на случайную величину, кратную значению 2π/N, при каждом изменении рабочей частоты , i=1, 2, …, I, который излучается передающей антенной в сторону корреспондента.

Принятый широкополосный сигнал со случайным изменением фазы поступает с выхода антенны на первый вход частотного смесителя (23), на второй вход которого подается перестраиваемое по псевдослучайной программе опорное колебание с выхода частотного синтезатора (21).

В результате преобразования в частотном смесителе (23) принятого и опорного сигналов на его выходе формируется сигнал ФМ-N промежуточной частоты, который подается на информационный вход (1) БУФС (24), в котором с помощью команд, поступающих от дешифратора (22) на управляющие входы, производится компенсация внесенного на передающей части случайного значения мгновенной фазы сигнала.

Алгоритм функционирования БУФС (24) аналогичен алгоритму функционирования БУФС (4). С выхода БУФС (24) сигнал ФМ-2 поступает на вход усилителя промежуточной частоты (25) и подается на вход демодулятора (26). На выходе демодулятора (26) формируется дискретный сигнал, который поступает на вход декодера (27) и одновременно на вход блока синхронизации (17), обеспечивающего формирование очередного номера рабочей частоты генератора псевдослучайной последовательности (18) и синхронную перестройку частотного синтезатора (21), а с выхода декодера (27) - к получателю сообщения и одновременно на входы анализатора качества канала (13), дешифратора квитанции (16) и дешифратора команды изменения скорости (12).

Дешифратор команды изменения скорости (12) преобразует полученный цифровой код сформированного в блоке формирования сообщения (11) приемной части корреспондента в сигнал для перестройки частоты генерирования импульсов управления, который через линию задержки (15) поступает на вход генератора управления ключом (10) предающей части устройства.

При браковке канала с выхода анализатора качества канала (13) подается сигнал логической единицы одновременно на вход (1) блока памяти (14) и на вход (1) блока формирования сообщения (11). Блок памяти (14) при поступлении на его входы (1) и (2) импульсов от блоков (13) и (16) формирует управляющий импульс, поступающий на генератор управления ключом (19), управляющий высокочастотным ключом (20). Блок формирования сообщений (11) при подаче импульса на вход (1) формирует необходимый цифровой код для изменения скорости переключения рабочей частоты, а при подаче импульса на вход (2) - цифровой код, обозначающий квитанцию, который с помощью высокочастотного ключа (3) коммутируется с трактом передачи.

Для оценки свойств помехозащищенности реализуемого с использованием разработанного устройства широкополосного радиосигнала в среде MatLAB проведен эксперимент по имитации передачи информации в цифровых линиях радиосвязи информационной битовой последовательности из 106 бит. При проведении эксперимента полагалось, что N=16, а система противодействия радиолинии идентифицирует режим ее функционирования как ППРЧ с многофазной манипуляцией. Получен выигрыш по помехозащищенности 2 дБ, что подтверждает достижение цели изобретения.

Литература

1. Королев А.И. Автоматика, телемеханика и связь на железнодорожном транспорте. - М.: Воениздат, 1985. - 488 с. 2. Грачев Н.П., Грачев В.П., Грецев С.Е. и др. Вычислительная техника и информационные технологии. - СПб: ВАС, 2013. - 204 с.

2. Радиоприемные устройства / Под ред. Л.Г. Барулина. - М.: Радио и связь, 1984. - 272 с.

3. Широкополосное приемопередающее устройство (патент на изобретение РФ №2157051, 2000 г.).

4. Комплекс средств радиосвязи «Арбалет». - СПб.: ВАС, 1996. - 132 с.

5. Батушев В.А. Микросхемы и их применение. - М.: Радио и связь, 1983. - 271 с.

6. Системы с прыгающей частотой / В кн.: Кларк Дж., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. - М: Радио и связь, 1987. - С. 352-356.

7. Авраменко А.А., Галямичев Ю.П., Ланнэ А.А. Электрические линии задержки и фазовращатели. - М.: Связь, 1973. - 120 с.

8. Бирюков С.И. Цифровые устройства на интегральных микросхемах. - М.: Радио и связь, 1984. - 88 с.

9. Аналоговая и цифровая электроника / Под ред. О.П. Глудкина. - М.: Горячая линия - Телеком, 2000. - 768 с.

10. Филинов В.В. Электротехника и схемотехника. Основы радиотехнических цепей и сигналов: учебное пособие. - М., 2014. - 169 с.

11. Хоровиц П., Хилл У. Искусство схемотехники: В 3-х томах: Т. 1. - М.: Мир, 1993. - 407 с.

1. Широкополосное приемопередающее устройство с программной перестройкой фазы сигнала, состоящее из передающей части, приемной части и содержащее на передающей стороне кодер (1), вход которого является информационным входом устройства, а выход подключен к фазовому манипулятору (2), выход которого подключен к первому входу высокочастотного ключа (3), причем выходом передающей части устройства является выход частотного смесителя (5), второй вход которого соединен с выходом частотного синтезатора (9), вход частотного синтезатора (9) подключен к выходу высокочастотного ключа (8), на первый вход которого подключен выход генератора псевдослучайной последовательности (7), а второй вход соединен с генератором управления ключом (10), выход частотного смесителя (5) соединен с передающей антенной, в приемной части приемная антенна соединена с первым входом смесителя (23), выход усилителя промежуточной частоты (25) соединен с входом демодулятора (26), выход которого подключен к входам блока синхронизации (17) и декодера (27), а выход декодера (27) является выходом приемной части устройства и подключен к входам дешифратора изменения скорости (12), анализатора качества канала (13), дешифратора квитанции (16), выход которого подключен к второму входу блока памяти (14), первый вход которого соединен с выходом анализатора качества канала (13) и первым входом блока формирования сообщения (11), второй вход которого подключен к выходу дешифратора команды изменения скорости (12) и к входу линии задержки (15), причем выход блока формирования сообщения (11) соединен со вторым входом высокочастотного ключа (3) передающей части, выход линии задержки (15) подключен к входу генератора управления ключом (10) передающей части, а выход блока памяти (14) соединен с входом генератора управления ключом (19), выход которого подключен к второму входу высокочастотного ключа (20), причем первый вход высокочастотного ключа (20) через генератор псевдослучайной последовательности (18) соединен с выходом блока синхронизации (17), а выход высокочастотного ключа (20) подключен к входу частотного синтезатора (21), выход которого соединен с вторым входом частотного смесителя (23), отличающееся тем, что в передающую часть устройства дополнительно введен блок управления фазовым сдвигом (БУФС) (4), информационный вход которого подключен к выходу высокочастотного ключа (3), а управляющие входы соединены с соответствующими выходами дешифратора (6), вход которого подключен к выходу генератора псевдослучайной последовательности (7), выход БУФС (4) подключен к первому входу частотного смесителя (5), в приемную часть устройства дополнительно введен БУФС (24), информационный вход которого подключен к выходу смесителя (23), а управляющие входы соединены с соответствующими выходами дешифратора (22), вход которого подключен к выходу генератора псевдослучайной последовательности (18), а выход БУФС (24) подключен к входу усилителя промежуточной частоты (25).

2. Устройство по п. 1, отличающееся тем, что БУФС (4 (24)) состоит из управляемых ключей (4.1 (24.1)) - (4.N (24.N)), фазовращателей (4.m (24.m))-(4.М (24.М)), причем первый вход управляемого ключа (4.1 (24.1)) и входы фазовращателей (4.m (24.m)) - (4.М (24.М)) объединены и являются информационным входом БУФС (4 (24)), а выходы фазовращателей (4.m (24.m)) - (4.М (24.М)) подключены к первым входам управляемых ключей (4.2 (24.2)) - (4.N (24.N)) соответственно, вторые входы управляемых ключей (4.1 (24.1)) - (4.N (24.N)) являются управляющими входами БУФС (4(24)), выходы управляемых ключей (4.1 (24.1)) - (4.N (24.N)) объединены и являются выходом БУФС (4 (24)).