Устройство для передачи многофазной системы напряжений по оптоволоконной линии

Иллюстрации

Показать всеИзобретение относится к области электротехники и может быть использовано для передачи n-фазного напряжения по оптоволоконной линии. Технический результат состоит в повышении надежности устройства за счет передачи многофазных напряжений на большие расстояния. Для этого в устройстве передачи многофазной системы напряжений по оптоволоконной линии дополнительно включены генератор синусоидальной ЭДС 8, фазосдвигающие схемы 9i (i=2..n), вторые транзисторные ключи 10i (i=1…n), группа инверторов 12i (i=1…n), сумматоры 13i (i=1…n), аналого-цифровые преобразователи дискретных напряжений фаз (АЦП) 14i (i=1…n), группа элементов ИЛИ 15, первая оптоволоконная линия связи (ВОЛС) 16, вторая оптоволоконная линия ВОЛС 17, второй дешифратор 18, группы вторых элементов И 19i (i=1…n, n - число фаз в сети), цифроаналоговые преобразователи (ЦАП) 20i (i=1…n), усилители мощности. 1 ил.

Реферат

Изобретение относится к области электротехники. Технический результат заключается в расширении функциональных возможностей за счет передачи n-фазного напряжения по оптоволоконной линии.

Известно устройство для передачи многофазной системы напряжений [1], которое позволяет передавать многофазную систему напряжений по радиосети.

Недостатком данного устройства является низкая надежность при передаче многофазной системы напряжений на большие расстояния.

Задача изобретения - создать устройство, обеспечивающее повышение надежности устройства за счет передачи многофазной системы напряжений по оптоволоконной линии.

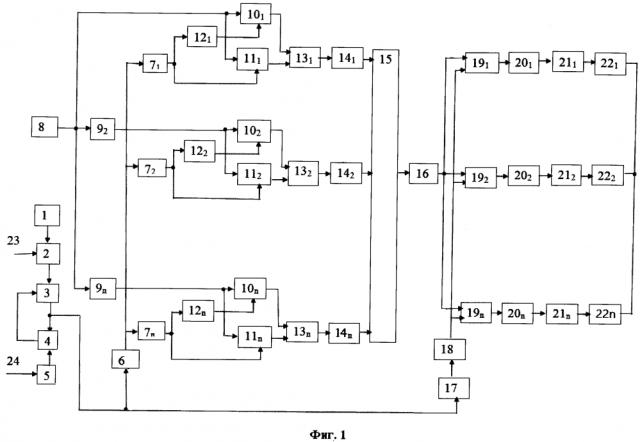

Это решение достигается тем, что в устройство, содержащее генератор тактовых импульсов (ГТИ) 1, первый элемент И 2, счетчик числа фаз 3, схему сравнения 4, регистр 5, первый дешифратор 6, формирователи импульсов 7i (i=1…n, n - число фаз), первая группа транзисторных ключей 11i (i=1…n), блоки нагрузки 22i (i=1…n), выход ГТИ 1 подсоединен к первому входу первого элемента И 2, второй вход которого подсоединен к первому входу 23 устройства, а выход - к первому входу счетчика 3, выход которого подсоединен к входу первого дешифратора 6, а также к первому входу схемы сравнения 4, второй вход которой подсоединен к выходу регистра 5, а выход - ко второму входу счетчика 3, вход регистра 5 подсоединен ко второму входу 24 устройства, выходы дешифратора 6 подсоединены к входам формирователей импульсов 7i (i=1…n), управляющий вход первого транзисторного ключа 11i (i=1…n) подсоединен к выходу формирователя импульсов 7i, включены генератор синусоидальной ЭДС 8, фазосдвигающие схемы 9i (i=2..n), вторые транзисторные ключи 10i (i=1…n), группа инверторов 12i (i=1…n), сумматоры 13i (i=1…n), аналого-цифровые преобразователи дискретных напряжений фаз (АЦП) 14i (i=1…n), группа элементов ИЛИ 15, первая оптоволоконная линия связи (ВОЛС) 16, вторая оптоволоконная линия ВОЛС 17, второй дешифратор 18, группы вторых элементов И 19i (i=1…n, n - число фаз в сети), цифроаналоговые преобразователи (ЦАП) 20i (i=1…n), усилители мощности 21i (i=1…n), выход генератора синусоидальной ЭДС 8 подсоединен к входам фазосдвигающих схем 9i (i=2…n, n - число фаз), ко второму входу первого транзисторного ключа 111 и ко второму входу второго транзисторного ключа 101, выход фазосдвигающей схемы 9i (i=2..n, n - число фаз) подсоединен ко второму входу первых транзисторных ключей 11i (i=2…n) и ко второму входу вторых транзисторных ключей 10i (i=2…n), управляющий вход второго транзисторного ключа 10i (i=1…n) через инвертор 12i подсоединен к выходу формирователя импульсов 7i, выходы первых транзисторных ключей 11i (i=1…n) подсоединены к первым входам сумматоров 13i (i=1…n), выходы вторых транзисторных ключей 10i (i=1…n) подсоединены ко вторым входам сумматоров 13i (i=1…n), выходы которых подсоединены к входам АЦП 14i (i=1…n), выходы которых подсоединены к одноименному входу группы элементов ИЛИ 15, выход которой подсоединен к входу первой ВОЛС 16, выход которой подсоединен к первым входам вторых элементов И 19i (i=1..n), выходы вторых элементов И 19i подсоединены к входам ЦАП 20i (i=1…n), вторые входы вторых элементов И 19i, (i=1…n) подсоединены к одноименным выходам второго дешифратора 18, вход которого подсоединен к выходу второй ВОЛС 17, вход которой подсоединен к выходу счетчика 3, выходы ЦАП 20i (i=1…n) подсоединены к входам усилителей мощности 21i (i=1…n), выходы которых подсоединены к фазам нагрузки 22i (i=1…n).

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

Сущность изобретения поясняется чертежом, где на чертеже (фиг. 1) представлены: генератор тактовых импульсов (ГТИ) 1, логический элемент И 2, счетчик числа фаз 3, схема сравнения 4, регистр 5, дешифратор 6, источник опорного синусоидального напряжения 8, схемы для сдвига фазы опорного напряжения на величину (360*(i-1)/n) 9i (i=2…n, n - число фаз в сети), формирователи импульсов 7i, транзисторные n-p-n ключи 10i, (i=1…n), предназначенные для выделения импульсов мгновенных значений напряжений фаз отрицательной полярности, управление открытым состоянием которых осуществляется управляющими импульсами, поступающими от формирователей импульсов 7i через инверторы импульсов 12i, (i=1…n), транзисторные p-n-р ключи 11i, (i=1…n), предназначенные для выделения импульсов мгновенных значений напряжений фаз положительной полярности, управление открытым состоянием которых осуществляется управляющими импульсами, поступающими от формирователей импульсов 7i, сумматоры 13i, (i=1…n), на входы которых поступают мгновенные значения напряжений фаз с выходов ключей 10i и 11i, (i=1…n), аналого-цифровые преобразователи дискретных напряжений фаз (АЦП) 14i (i=1…n), группа элементов ИЛИ 15, оптоволоконная линия связи (ВОЛС) 16, ВОЛС 17, дешифратор 18, группа элементов И 19i (i=1…n, n - число фаз в сети), цифроаналоговые преобразователи (ЦАП) 20i (i=1…n), усилители мощности 21i (i=1…n), нагрузки фаз 22i (i=1…n), входы 23 и 24 вместе со связями.

Устройство работает следующим образом.

В исходном состоянии на регистре 5 по входу 24 записан код числа фаз n. На счетчике 3 хранится код нуля (вход сброса в ноль на счетчике 3 на фиг. 1 не показан). Работа устройства начинается после подачи пускового сигнала по входу 23 логического элемента И 2, после чего импульсы с выхода ГТИ 1 через открытый элемент И 2 начинают поступать на вход счетчика 3. Код с выхода счетчика 3 поступает на вход схемы сравнения 4, на вход ВОЛС 17 и на вход дешифратора 6, на выходе которого появляется единичный сигнал только на одном из его выходов.

Единичный сигнал на i-м (i=1…n) выходе дешифратора 6 подается на вход формирователя импульсов 7i, с выхода которого управляющий импульс поступает на управляющие электроды транзисторных ключей 11i и, через инвертор 12i, на ключ 10i. В зависимости от полярности мгновенного значения источника напряжения срабатывает ключ 10i или 11i. Импульсы напряжения отрицательной полярности проходят через ключ 10i, а напряжения положительной полярности - через ключ 11i. Прошедшие через ключи 10i или 11i импульсы напряжения суммируются сумматором 13i. С выхода сумматора 13i выделенные импульсы фаз напряжений поступают на вход АЦП 14i (i=1…n), а далее на вход группы элементов ИЛИ 15, с выхода которых код поступает в ВОЛС 16.

Код с выхода ВОЛС 16 поступает на первые входы группы элементов И 19i (i=1…n, n - число фаз в сети). На вторые входы элементов И 19i поступают сигналы от дешифратора 18, работа которого аналогична работе дешифратора 6. На вход дешифратора 18 код поступает по линии ВОЛС 17 с выхода счетчика 3. С выходов группы элементов И 19i код поступает на вход ЦАП 20i (i=1…n), с выхода которого сигнал поступает на усилитель мощности 21i (i=1…n), а далее в нагрузку фаз линии 22i (i=1…n). Усилители мощности 21i в фазах нагрузки необходимы для обеспечения необходимого уровня напряжения и мощности на нагрузке.

При достижении счетчиком 3 числа n на выходе схемы сравнения 4 появляется единичный сигнал, который сбрасывает счетчик 3 в нулевое состояние, после чего цикл передачи импульсов в устройстве повторяется.

Использованные источники

1. RU N 2594290, кл. Н04В 17/00, 2016 г.

Устройство передачи многофазной системы напряжений по оптоволоконной линии, содержащее генератор тактовых импульсов (ГТИ) 1, первый элемент И 2, счетчик числа фаз 3, схему сравнения 4, регистр 5, первый дешифратор 6, формирователи импульсов 7i (i=1…n, n - число фаз), первую группу транзисторных ключей 11i (i=1…n), блоки нагрузки 22i (i=1…n), выход ГТИ 1 подсоединен к первому входу первого элемента И 2, второй вход которого подсоединен к первому входу 23 устройства, а выход - к первому входу счетчика 3, выход которого подсоединен к входу первого дешифратора 6, а также к первому входу схемы сравнения 4, второй вход которой подсоединен к выходу регистра 5, а выход - ко второму входу счетчика 3, вход регистра 5 подсоединен ко второму входу 24 устройства, выходы дешифратора 6 подсоединены к входам формирователей импульсов 7i (i=1…n), управляющий вход первого транзисторного ключа 11i (i=1…n) подсоединен к выходу формирователя импульсов 7i, отличающееся тем, что в него дополнительно включены генератор синусоидальной ЭДС 8, фазосдвигающие схемы 9i (i=2..n), вторые транзисторные ключи 10i (i=1…n), группа инверторов 12i (i=1…n), сумматоры 13i (i=1…n), аналого-цифровые преобразователи дискретных напряжений фаз (АЦП) 14i (i=1…n), группа элементов ИЛИ 15, первая оптоволоконная линия связи (ВОЛС) 16, вторая оптоволоконная линия ВОЛС 17, второй дешифратор 18, группы вторых элементов И 19i (i=1…n, n - число фаз в сети), цифроаналоговые преобразователи (ЦАП) 20i (i=1…n), усилители мощности 21i (i=1…n), выход генератора синусоидальной ЭДС 8 подсоединен к входам фазосдвигающих схем 9i (i=2…n, n - число фаз), ко второму входу первого транзисторного ключа 111 и ко второму входу второго транзисторного ключа 101, выход фазосдвигающей схемы 9i (i=2..n, n - число фаз) подсоединен ко второму входу первых транзисторных ключей 11i (i=2…n) и ко второму входу вторых транзисторных ключей 10i (i=2…n), управляющий вход второго транзисторного ключа 10i (i=1…n) через инвертор 12i подсоединен к выходу формирователя импульсов 7i, выходы первых транзисторных ключей 11i (i=1…n) подсоединены к первым входам сумматоров 13i (i=1…n), выходы вторых транзисторных ключей 10i (i=1…n) подсоединены ко вторым входам сумматоров 13i (i=1…n), выходы которых подсоединены к входам АЦП 14i (i=1…n), выходы которых подсоединены к одноименному входу группы элементов ИЛИ 15, выход которой подсоединен к входу первой ВОЛС 16, выход которой подсоединен к первым входам вторых элементов И 19i (i=1..n), выходы вторых элементов И 19i подсоединены к входам ЦАП 20i (i=1…n), вторые входы вторых элементов И 19i, (i=1…n) подсоединены к одноименным выходам второго дешифратора 18, вход которого подсоединен к выходу второй ВОЛС 17, вход которой подсоединен к выходу счетчика 3, выходы ЦАП 20i (i=1…n) подсоединены к входам усилителей мощности 21i (i=1…n), выходы которых подсоединены к фазам нагрузки 22i (i=1…n).