Частотно-фазовый компаратор

Иллюстрации

Показать всеИзобретение относится к области измерительной техники и может быть использовано в качестве логического элемента сравнения частот следования и формирования фазового рассогласования импульсов задающего генератора и датчика обратной связи в системах автоматического управления, построенных на основе принципа фазовой автоподстройки частоты. Технический результат заключается в расширении линейной зоны работы частотно-фазового компаратора в режиме синхронизации контура фазовой автоподстройки частоты. Частотно-фазовый компаратор содержит третий, четвертый и пятый логические элементы И, сумматор-вычитатель, третий и четвертый D-триггеры, второй логический элемент ИЛИ и RS-триггер. Первый и второй входы третьего логического элемента И подключены соответственно к инверсным выходам первого и второго блокирующих D-триггеров. Выход третьего логического элемента И является П выходом компаратора и подключен к S-входу RS-триггера и к R-входам третьего и четвертого D-триггеров. 1 ил.

Реферат

Изобретение относится к области измерительной техники и может быть использовано в качестве логического элемента сравнения частот следования и формирования фазового рассогласования импульсов задающего генератора и датчика обратной связи в системах автоматического управления, построенных на основе принципа фазовой автоподстройки частоты.

Известен частотно-фазовый компаратор (А.С. RU №484621, опубл. 15.09.1975 г.), содержащий схемы И-НЕ, два блокирующих и фазовый триггер, входы которого подключены к клеммам источников контролируемой и эталонной частоты и к входам двух схем И-НЕ, к вторым входам которых подключены соответственно единичный и нулевой выходы фазового триггера, а к выходам - первые входы блокировочных триггеров, нулевые выходы которых соединены с их вторыми входами через третью схему И-НЕ, а единичные выходы соответственно - с первыми входами четвертой и пятой схем И-НЕ, при этом второй вход пятой схемы И-НЕ соединен с выходом четвертой схемы И-НЕ, второй вход которой подключен к нулевому выходу фазового триггера. В данной схеме имеется возможность получения сигналов, соответствующих прохождению двух импульсов одной из сравниваемых частот между двумя импульсами другой из сравниваемых частот.

Недостатком этого устройства является низкая надежность работы частотно-фазового компаратора, в значительной степени связанная с зависимостью от длительности импульсов источников контролируемой и эталонной частоты, что определяет необходимость использования на входе компаратора дополнительных формирователей коротких импульсов, усложняющих компаратор.

Наиболее близким техническим решением к заявляемому устройству является частотно-фазовый компаратор (Патент RU №2469461, опубл. 10.12.2003 г.), содержащий фазовый триггер, входы которого подключены к клеммам источников контролируемой и эталонной частоты, прямой и инверсный выходы фазового триггера подключены соответственно к информационным D-входам первого и второго D-триггеров, синхровходы которых подключены соответственно к источникам контролируемой и эталонной частоты, выходы первого и второго D-триггеров подключены соответственно к входам первого и второго одновибраторов, при этом выход первого одновибратора подключен к первому входу первого логического элемента И, к первому входу логического элемента ИЛИ, к R-входу первого D-триггера и является 2/2 выходом частотно-фазового компаратора, а выход второго одновибратора является 0/2 выходом частотно-фазового компаратора, подключен к первому входу второго логического элемента И, к второму входу логического элемента ИЛИ, к R-входу второго D-триггера, выход логического элемента ИЛИ через элемент задержки подключен к синхровходам первого и второго блокирующих D-триггеров, информационный D-вход первого блокирующего D-триггера подключен к выходу первого логического элемента И, второй вход которого подключен к инверсному выходу второго блокирующего D-триггера, информационный D- вход которого подключен к выходу второго логического элемента И, второй вход которого подключен к инверсному выходу первого блокирующего D-триггера, прямой выход которого является Т выходом частотно-фазового компаратора, Р выходом которого является прямой выход второго блокирующего D-триггера, инверсные выходы фазового триггера и первого блокирующего D-триггера подключены соответственно к первому и второму входам первого логического элемента И-НЕ, выход которого подключен к первому входу второго логического элемента И-НЕ, второй вход которого подключен к инверсному выходу второго блокирующего D-триггера, выход второго логического элемента И-НЕ является γ выходом частотно-фазового компаратора.

Недостатком данного устройства являются узкие функциональные возможности частотно-фазового компаратора.

Техническим результатом изобретения является расширение линейной зоны работы частотно-фазового компаратора в режиме синхронизации контура фазовой автоподстройки частоты, что позволяет расширить функциональные возможности компаратора при его использовании в системах управления.

Данный технический результат достигается тем, что в частотно-фазовый компаратор, содержащий фазовый триггер, входы которого подключены к клеммам источников контролируемой и эталонной частоты, прямой и инверсный выходы фазового триггера подключены соответственно к информационным D-входам первого и второго D-триггеров, синхровходы которых подключены соответственно к источникам контролируемой и эталонной частоты, выходы первого и второго D-триггеров подключены соответственно к входам первого и второго одновибраторов, при этом выход первого одновибратора подключен к первому входу первого логического элемента И, к первому входу логического элемента ИЛИ, к R-входу первого D-триггера и является 2/2 выходом частотно-фазового компаратора, а выход второго одновибратора является 0/2 выходом частотно-фазового компаратора, подключен к первому входу второго логического элемента И, к второму входу логического элемента ИЛИ, к R-входу второго D-триггера, выход логического элемента ИЛИ через элемент задержки подключен к синхровходам первого и второго блокирующих D-триггеров, информационный D-вход первого блокирующего триггера подключен к выходу первого логического элемента И, второй вход которого подключен к инверсному выходу второго блокирующего D-триггера, информационный D-вход которого подключен к выходу второго логического элемента И, второй вход которого подключен к инверсному выходу первого блокирующего D-триггера, прямой выход которого является Т выходом частотно-фазового компаратора, Р выходом которого является прямой выход второго блокирующего триггера, инверсные выходы фазового триггера и первого блокирующего триггера подключены соответственно к первому и второму входам первого логического элемента И-НЕ, выход которого подключен к первому входу второго логического элемента И-НЕ, второй вход которого подключен к инверсному выходу второго блокирующего D-триггера, выход второго логического элемента И-НЕ является γ выходом частотно-фазового компаратора, согласно заявляемому техническому решению введены третий, четвертый и пятый логические элементы И, сумматор-вычитатель, третий и четвертый D-триггеры, второй логический элемент ИЛИ и RS-триггер, первый и второй входы третьего логического элемента И подключены соответственно к инверсным выходам первого и второго блокирующих D-триггеров, а выход третьего логического элемента И является П выходом компаратора и подключен к S-входу RS-триггера и к R-входам третьего и четвертого D-триггеров, D-входы которых подключены соответственно к прямым выходам второго и первого блокирующих D-триггеров, а синхровходы подключены соответственно к выходам первого и второго одновибраторов, выходы третьего и четвертого D-триггеров подключены соответственно к первому и второму входам второго логического элемента ИЛИ, выход которого подключен к R-входу RS-триггера, выход которого является Пр выходом устройства, и подключен ко вторым входам четвертого и пятого логических элементов И, первые входы которых подключены соответственно к прямым выходам второго и первого блокирующих D-триггеров, а выходы подключены соответственно ко второму суммирующему и вычитающему входам сумматора-вычитателя, первый суммирующий вход которого подключен к инверсному выходу фазового RS-триггера, выход сумматора-вычитателя является Δϕp выходом устройства.

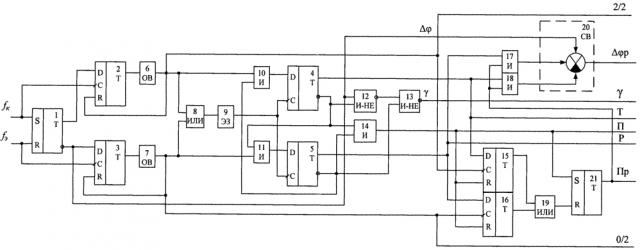

Сущность технического решения пояснена чертежом, где на приведена функциональная электрическая схема предлагаемого устройства.

Частотно-фазовый компаратор содержит: фазовый RS-триггер 1, D-триггеры 2, 3, 15, 16, блокирующие D-триггеры 4 и 5, одновибраторы 6 и 7, логические элементы ИЛИ 8 и 19, элемент задержки 9, схемы И 10, 11, 14, 17, 18, логические элементы И-НЕ 12 и 13, сумматор-вычитатель 20.

Входы фазового RS-триггера 1 в устройстве являются синхровходами первого D-триггера 2 и второго D-триггера 3 и подключены к клеммам источников контролируемой и эталонной частоты. Информационные D-входы первого D-триггера 2 и второго D-триггера 3 подключены соответственно к прямому и инверсному выходу фазового RS-триггера 1. Выходы первого D-триггера 2 и второго D-триггера 3 подключены соответственно к входам первого одновибратора 6 и второго одновибратора 7. Выход первого одновибратора 6 подключен к первому входу первого логического элемента И 10, к первому входу первого логического элемента ИЛИ 8, к R-входу первого D-триггера 2 и подключен к синхровходу третьего D-триггера 15 и является 2/2 выходом частотно-фазового компаратора. Выход одновибратора 7 подключен к первому входу второго логического элемента И 11, к второму входу первого логического элемента ИЛИ 8, к R-входу второго D-триггера 3, подключен к синхровходу четвертого D-триггера 16 и является 0/2 выходом частотно-фазового компаратора. Выход первого логического элемента ИЛИ 8 через элемент задержки 9 подключен к синхровходам первого и второго блокирующих D-триггеров 4 и 5. Информационный D-вход первого блокирующего D-триггера 4 подключен к выходу первого логического элемента И 10, второй вход которого подключен к инверсному выходу второго блокирующего D-триггера 5, ко второму входу третьего логического элемента И 14 и ко второму входу второго логического элемента И-НЕ 13, информационный D-вход второго блокирующего D-триггера 5 подключен к выходу второго логического элемента И 11, второй вход которого подключен к инверсному выходу первого блокирующего D-триггера 4, к первому входу третьего логического элемента И 14 и к первому входу первого логического элемента И-НЕ 12. Прямые выходы первого и второго блокирующих D-триггеров 4 и 5 являются соответственно Т и Р выходами частотно-фазового компаратора и подключены соответственно к информационным D-входам третьего и четвертого D-триггеров 15 и 16. Второй вход первого логического элемента И-НЕ 12 подключен к инверсному выходу фазового RS-триггера 1 и к первому суммирующему входу сумматора-вычитателя 20. Выход первого логического элемента И-НЕ 12 подключен к первому входу второго логического элемента И-НЕ 13, выход которого является γ выходом частотно-фазового компаратора. Выход третьего логического элемента И 14 является П выходом частотно-фазового компаратора, подключен к S-входу RS-триггера 21 и к R-входам третьего и четвертого D-триггеров 15 и 16, синхровходы которых подключены соответственно к выходам первого и второго одновибраторов 6 и 7, выходы третьего и четвертого D-триггеров 15 и 16 подключены соответственно к первому и второму входам второго логического элемента ИЛИ 9, выход которого подключен к R-входу RS-триггера 21, выход которого является Пр выходом устройства и подключен ко вторым входам четвертого и пятого логических элементов И 17 и И 18, первые входы которых подключены соответственно к прямым выходам второго и первого блокирующих D-триггеров 5 и 4, а выходы подключены соответсвенно ко второму суммирующему и вычитающему входам сумматора-вычитателя 20, выход сумматора-вычитателя является Δϕp выходом устройства.

Частотно-фазовый компаратор работает следующим образом.

Компаратор имеет два режима работы: режим сравнения частот и режим сравнения фаз. При сближении частот компаратор автоматически переходит от режима сравнения частот к режиму сравнения фаз.

При превышении частоты эталонного сигнала над контролируемым обязательно возникает состояние, при котором в промежутке между поступлением на вход двух импульсов контролируемой частоты на вход подаются два импульса эталонной частоты. Первый импульс эталонной частоты устанавливает инверсный выход фазового RS-триггера 1 в состояние логической «1» (высокий уровень напряжения), подготовив D-триггер 3 к записи в него логической «1» при приходе второго импульса эталонной частоты. Второй импульс устанавливает D-триггер 3 в состояние логической «1». Импульс с выхода D-триггера 3 поступает на вход одновибратора 7, который формирует на выходе импульс (0/2 – ситуация отсутствия импульсов контролируемой частоты между двумя соседними импульсами эталонной частоты) требуемой длительности, обеспечивающей надежную работу частотно-фазового компаратора. Импульс с выхода одновибратора 7 одновременно поступает на R-вход D-триггера 3, устанавливая его в состояние логического «0», на первый вход схемы И 11 и с задержкой τ, равной времени срабатывания схем И, через схему ИЛИ 8 и элемент задержки 9 – на синхровходы блокирующих D-триггера 4 и D-триггера 5.

Если в предшествующий момент времени блокирующий D-триггер 4 находился в состоянии логического «0» (Т=0, ƒэ≥ƒк), то в момент прихода импульса на синхровход блокирующего D-триггера 5 на его D-входе уже будет сформирован сигнал логической «1», т.к. импульс, который поступит с одновибратора 7 через схему И 11, придет на время τ раньше. В результате блокирующий D-триггер 5 перейдет в состояние логической «1», формируя сигнал (Р=1, ƒэ>ƒк) о превышении эталонной частоты над контролируемой. Инверсный выход блокирующего D-триггера 5 при этом блокирует работу схемы И-НЕ 13 и на выходе γ частотно-фазового компаратора устанавливается состояние логической «1». Состояние блокирующего D-триггера 4 при этом остается неизменным, т.к. в момент прихода импульса на его синхровход на D-входе присутствует логический «0».

Если в предшествующий момент времени блокирующий D-триггер 4 был включен (Т=1), то в момент прихода импульса на синхровход блокирующего D-триггера 5 его D-вход будет находиться в состоянии «0», т.к. импульс с одновибратора 7 не пройдет через заблокированный инверсным выходом блокирующего D-триггера 4 логический элемент И 11. В результате на прямом выходе блокирующего D-триггера 5 установится сигнал логического «0» (Р=0), а инверсный выход устанавливается в состояние «1» и тем самым разблокирует работу логического элемента И-НЕ 13. Блокирующий D-триггер 4 при этом переходит в выключенное состояние (Т=0), т.к. в момент прихода импульса на его синхровход на D-входе присутствует сигнал логического «0». Компаратор переходит от режима сравнения частот к режиму сравнения фаз. Поскольку при этом на логические элементы И-НЕ 12 и И-НЕ 13 с инверсных выходов блокирующих D-триггеров 4 и 5 поданы «разрешающие» сигналы логической «1», то на выход компаратора проходит сигнал фазовой ошибки γ=Δϕ с инверсного выхода фазового RS-триггера 1, длительность выходных импульсов которого пропорциональна фазовому сдвигу импульсов сравниваемых частот. С помощью логического элемента И 14 формируется сигнал П, соответствующий режиму фазового сравнения компаратора (-π≤Δϕ<π).

При превышении частоты контролируемого сигнала над эталонным формирование выходного сигнала компаратора γ осуществляется аналогично (вследствие симметрии схемы компаратора), начиная с установки прямого выхода фазового RS-триггера 1 в состояние логической «1».

При переходе компаратора в режим фазового сравнения на выходе логического элемента И 14 появляется сигнал П=1, по которому происходит установка RS-триггера 21 в состояние логической «1» и формирование выходного сигнала Пр компаратора, являющегося индикатором режима фазового сравнения с расширенной в 3 раза линейной зоной формирования сигнала фазовой ошибки. При появлении сигнала Пр=1, открываются цифровые ключи, выполненные на логических элементах И17, И18, разрешая прохождения сигналов Р и Т соответственно на суммирующий и вычитающий входы сумматора-вычитателя 20, на выходе которого появляется сигнал фазовой ошибки Δϕp с расширенной в 3 раза линейной зоной пропускания (-3π≤Δϕp<3π). Прибавление сигнала Р=1 к сигналу Δϕ позволяет расширить линейную зону определения фазовой ошибки до 3π, а вычитание сигнала Т=1 – расширить линейную зону определения фазовой ошибки до минус 3π. Трехкратное расширение линейной зоны определения фазовой ошибки позволяет исключить в режиме синхронизации контура фазовой автоподстройки частоты ситуации повторного выхода компаратора в режимы насыщения, которые могут происходить при больших начальных условиях по ошибке по частоте при входе в режим синхронизации, и в результате повысить быстродействие контура фазовой автоподстройки частоты в переходных режимах работы.

Сброс RS-триггера 21 в состояние логического «0» (Пр=0) и соответственно сужение линейной зоны в 3 раза до исходного состояния происходит в случае повторного формирования сигналов 0/2 или 2/2, что соответствует скачкообразному изменению задающей (эталонной) частоты ƒэ. Определение ситуации повторного прохождения импульсов 2/2 осуществляется с помощью третьего D-триггера 15, на информационный D-вход которого подается сигнал Т (соответствующий первому появлению импульса 2/2), а на тактовый С-вход – сигнал 2/2. Определение ситуации повторного прохождения импульсов 0/2 осуществляется с помощью четвертого D-триггера 16, на информационный D-вход которого подается сигнал Р (соответствующий первому появлению импульса 0/2), а на тактовый С-вход – сигнал 0/2. Сброс третьего и четвертого D-триггеров 15, 16 осуществляется по сигналу П, соответствующему работе компаратора в режиме фазового сравнения. При появлении сигнала логической «1» на выходе третьего или четвертого D-триггеров 15, 16 на R-вход RS-триггера 21 через логический элемент ИЛИ 19 проходит сигнал логической «1», сбрасывая RS-триггера 21 в состояние логического «0», что соответствует окончанию режима работы компаратора в расширенной линейной зоне (Пр=0).

Таким образом, предлагаемое техническое решение позволяет расширить функциональные возможности частотно-фазового компаратора за счет введения в устройство трех логических элементов И, сумматора-вычитателя, двух D-триггеров, логического элемента ИЛИ и RS-триггера. В результате введения данных элементов в схему компаратора дополнительно обеспечивается формирование расширенной в 3 раза линейной зоны определения фазовой ошибки и индикация ее наличия (дополнительные функции компаратора), что позволяет исключить в режиме синхронизации контура фазовой автоподстройки частоты ситуаций повторного выхода компаратора в режимы насыщения, которые могут происходить при больших начальных условиях по ошибке по частоте при входе в режим синхронизации, и в результате повысить быстродействие контура фазовой автоподстройки частоты в переходных режимах работы.

Частотно-фазовый компаратор, содержащий фазовый триггер, входы которого подключены к клеммам источников контролируемой и эталонной частоты, прямой и инверсный выходы фазового триггера подключены соответственно к информационным D-входам первого и второго D-триггеров, синхровходы которых подключены соответственно к источникам контролируемой и эталонной частоты, выходы первого и второго D-триггеров подключены соответственно к входам первого и второго одновибраторов, при этом выход первого одновибратора подключен к первому входу первого логического элемента И, к первому входу логического элемента ИЛИ, к R-входу первого D-триггера и является 2/2 выходом частотно-фазового компаратора, а выход второго одновибратора является 0/2 выходом частотно-фазового компаратора, подключен к первому входу второго логического элемента И, к второму входу логического элемента ИЛИ, к R-входу второго D-триггера, выход логического элемента ИЛИ через элемент задержки подключен к синхровходам первого и второго блокирующих D-триггеров, информационный D-вход первого блокирующего D-триггера подключен к выходу первого логического элемента И, второй вход которого подключен к инверсному выходу второго блокирующего D-триггера, информационный D-вход которого подключен к выходу второго логического элемента И, второй вход которого подключен к инверсному выходу первого блокирующего D-триггера, прямой выход которого является Т выходом частотно-фазового компаратора, Р выходом которого является прямой выход второго блокирующего D-триггера, инверсные выходы фазового триггера и первого блокирующего D-триггера подключены соответственно к первому и второму входам первого логического элемента И-НЕ, выход которого подключен к первому входу второго логического элемента И-НЕ, второй вход которого подключен к инверсному выходу второго блокирующего D-триггера, выход второго логического элемента И-НЕ является γ выходом частотно-фазового компаратора, отличающийся тем, что введены третий, четвертый и пятый логические элементы И, сумматор-вычитатель, третий и четвертый D-триггеры, второй логический элемент ИЛИ и RS-триггер, первый и второй входы третьего логического элемента И подключены соответственно к инверсным выходам первого и второго блокирующих D-триггеров, а выход третьего логического элемента И является П выходом компаратора и подключен к S-входу RS-триггера и к R-входам третьего и четвертого D-триггеров, D-входы которых подключены соответственно к прямым выходам второго и первого блокирующих D-триггеров, а синхровходы подключены соответственно к выходам первого и второго одновибраторов, выходы третьего и четвертого D-триггеров подключены соответственно к первому и второму входам второго логического элемента ИЛИ, выход которого подключен к R-входу RS-триггера, выход которого является Пр выходом устройства, и подключен ко вторым входам четвертого и пятого логических элементов И, первые входы которых подключены соответственно к прямым выходам второго и первого блокирующих D-триггеров, а выходы подключены соответственно ко второму суммирующему и вычитающему входам сумматора-вычитателя, первый суммирующий вход которого подключен к инверсному выходу фазового RS-триггера, выход сумматора-вычитателя является Δϕp выходом устройства.