Устройство межмодульного обмена по магистрали lvds-m с канальным резервированием и прямым доступом в память

Иллюстрации

Показать всеИзобретение относится к обработке цифровых данных и передаче дискретной информации по линиям связи. Технический результат – повышение помехоустойчивости межмодульного обмена. Устройство межмодульного обмена по магистрали LVDS-M с канальным резервированием и прямым доступом в память, содержащее первый и второй каналы обмена данными, состоящие из первого триггера синхронизатора, соединенного со вторым триггером синхронизатором в первом канале, первого триггера синхронизатора и соединенного со вторым триггером синхронизатором во втором канале, фильтра фазовой автоподстройки частоты для каждого канала, соединенного со вторым триггером синхронизатором своего канала и соединенного с контроллером протокола обмена своего канала, преобразователя из последовательного кода в параллельный для каждого канала, соединенного с выходом второго триггера синхронизатора своего канала и фильтром фазовой автоподстройки частоты своего канала, при этом в него введен декодер балансных кодов, соединенный с преобразователем последовательного кода в параллельный и соединенный с контроллером протокола обмена. 4 з.п. ф-лы, 5 ил.

Реферат

Изобретение относится к устройствам для обработки цифровых данных и устройствам передачи дискретной информации по линиям связи. Изобретение может найти применение в бортовой радиоэлектронной аппаратуре.

Известно устройство [Патент RU №2205445 С1, МПК G06F 13/14], содержащее блок приема данных и блок передачи данных, при этом блок передачи данных содержит генератор синхросигналов, сдвиговый регистр, элемент "Исключающее ИЛИ", триггер, два усилителя, блок приема данных содержит два усилителя, два формирователя импульсов, элемент ИЛИ, блок фазовой автоподстройки частоты, триггер.

Описанное устройство предназначено для синхронного приема и передачи данных по каналам связи. Взаимосвязь принимаемых и передаваемых данных осуществляется за счет сопровождения сигналом опорной частоты, по которому идет стробирование данных и восстановление согласно заданному протоколу обмена.

Недостатками данного устройства являются низкие помехозащищенность, надежность, а также отсутствие возможности работы на системы с гальванической развязкой и магистральные системы, высокие энергозатраты за счет передачи информации в стандартах типа «RS-485/422/232» или «TTL/CMOS», отсутствие типового контроллера прямого доступа в память «ПДП».

Известно устройство [Патент RU №95103054 А1, МПК Н04В 3/00], содержащее на передающей стороне генератор тактовых импульсов, два ключевых элемента, триггер, трансформатор, компаратор, элемент задержки, элемент И, диод, инвертор, а на приемной стороне - трансформатор, три диода, два конденсатора, два компаратора, триггер, ключевой элемент, элемент задержки, элемент И, инвертор. Устройство предназначено для асинхронной передачи данных по каналу связи.

Недостатком устройства является низкая надежность и высокие энергозатраты, низкая скорость приема-передачи, а также отсутствие типового контроллера «ПДП».

Известна полезная модель [Патент RU №148935 U1, МПК G06F 13/00], содержащая приемопередатчик, управляющий блок и блок гальванической развязки, приемопередатчик выполнен в виде гальваноизолированного драйвера последовательного интерфейса RS-422, управляющий блок - в виде микроконтроллера, а блок гальванической развязки - в виде согласующих импульсных трансформаторов, кроме того, в состав введена программируемая логическая интегральная схема, при этом сигналы с выхода прибора внешней системы сбора данных поступают через согласующие импульсные трансформаторы на входы программируемой логической матрицы, а с ее выходов - на входы микроконтроллера, с выходов последнего согласованные сигналы поступают на вход RS-422.

Устройство предназначено для асинхронной передачи данных по каналу связи, по протоколу RS-422 и организует взаимодействие при помощи контроллера протокола обмена на микросхеме программируемой вентильной матрицы и автомата управления контроллером на основе микроконтроллера.

Недостатком устройства является высокие энергозатраты приема-передачи по протоколу RS-422, низкая скорость приема-передачи, отсутствие типового контроллера «ПДП», отсутствие возможности работать на магистральные системы, а также низкая надежность ввиду отсутствия канального резервирования.

Известна полезная модель [Патент RU №140982 U1, МПК G06F 13/00], являющаяся наиболее близким аналогом к заявленному техническому решению и принятая за прототип. Устройство (микросхема) адаптера удаленных устройств, отличающаяся тем, что содержит двухканальный контроллер сети, по меньшей мере один контроллер последовательного периферийного интерфейса и блок конфигурации микросхемы, которые соединены между собой, а также по меньшей мере с одним универсальным периферийным портом и с микропроцессорным портом, при этом двухканальный контроллер выполнен с возможностью обеспечения управления микросхемой по протоколу, в частности с возможностью приема из сети и отправления в сеть меток времени и кодов распределенных прерываний; контроллер последовательного периферийного интерфейса выполнен с возможностью локального управления микросхемой; блок конфигурации микросхемы; микропроцессорный порт выполнен с возможностью подключения периферийных устройств с параллельными портами, поддерживающими адресацию, а также с возможностью эмуляции шин, имеющих различные сигналы управления; универсальный периферийный порт выполнен с возможностью подключения периферийных устройств, скорость обмена данными с которыми можно конфигурировать; четыре приемопередатчика низковольтных дифференциальных сигналов LVDS, соединенных с двухканальным контроллером сети, а универсальный периферийный порт выполнен с возможностью подключения широкого спектра периферийных устройств.

Вышеописанное устройство предназначено для асинхронного приема передачи данных. Содержит в себе типовой блок «ПДП», драйвер магистрали LVDS и организует обмен согласно заданному протоколу на скоростях от 2 Мбит/с до 100 Мбит/с.

Устройство имеет четыре ключевых недостатка:

1. В составе устройства применен кодер/декодер балансных кодов, который не обеспечивает возможность применения данного устройства в составе систем гальванической развязкой.

2. Примененный стандарт физической магистрали LVDS не позволяет использовать устройство в магистральных системах, а только в системах типа «точка - точка».

3. Среднеинтегральная скорость обмена между абонентами значительно ниже заявленной ввиду того, что в заданном протоколе обмена помехозащищенность основана на применении кодирования сигнала методом замещения (DS код) с дополнительной контрольной суммой (CRC8). Применение DS-кодирования не позволяет выявлять ошибки. Таким образом, количество верных транзакций на частоте свыше 10 Мбит будет снижено в условиях помеховой обстановки.

4. Устройство не содержит канального резервирования. Из описания следует, что оба драйвера каналов приема соединяются с контроллером протокола обмена. Выход контроллера приведет к отказу всей системы в целом.

Задачами изобретения являются: увеличение скорости обмена, повышение помехоустойчивости, снижение энергозатрат, возможность организации работы на магистральные линии связи с гальванической развязкой.

Задачи достигаются тем, что в устройство межмодульного обмена по магистрали LVDS-M с канальным резервированием и прямым доступом в память, содержащее первый и второй каналы обмена данными, состоящие из первого триггера синхронизатора, соединенного со вторым триггером синхронизатором в первом канале, первого триггера синхронизатора и соединенного со вторым триггером синхронизатором во втором канале, фильтра фазовой автоподстройки частоты для каждого канала, соединенного со вторым триггером синхронизатором своего канала и соединенного с контроллером протокола обмена своего канала, преобразователя из последовательного кода в параллельный для каждого канала, соединенного с выходом второго триггера синхронизатора своего канала и фильтром фазовой автоподстройки частоты своего канала, введен декодер балансных кодов, соединенный с преобразователем последовательного кода в параллельный и соединенный с контроллером протокола обмена, вход которого соединен с выходом преобразователя S-P и выход которого соединен со 2 входом автоматом управления, выход 1 и вход 3 автомата управления соединены с кодером балансных кодов, выход 2 автомата управления соединен с преобразователем параллельного кода в последовательный (P-S), выход P-S соединен с драйвером LVDS-M, выход 3 автомата управления первого и второго канала объединяются по схеме логического «ИЛИ» (Шина данных), выход 4 автомата управления первого и второго каналов объединены по схеме «И» (Шина управления), выход 4 автомата управления первого второго канала объединяются по схеме логического «ИЛИ» (Шина адреса), в устройства введена схема «ПДП», на входы которой поступают данные с выходов схем «И», первой схемы «ИЛИ», второй схемы «ИЛИ», выходы схемы «ПДП» связанны с внешними источниками (абонентами).

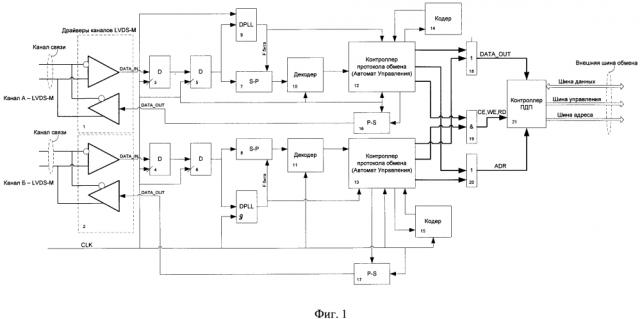

Устройство поясняется схемами и чертежами:

- на фиг. 1 представлена функциональная схема устройства межмодульного обмена по магистрали LVDS-M;

- на фиг. 2 - выход DPLL с замкнутой петлей ФАПЧ, стробирующий входной битовый поток;

- на фиг. 3 - выходной битовый поток декодера балансных кодов;

- на фиг. 4 - выходной битовый поток кодера балансных кодов;

- на фиг. 5 - работа контроллера «ПДП» в режимах чтения/записи данных.

Устройство межмодульного обмена по магистрали LVDS-M (фиг. 1) с канальным резервированием содержит в каждом канале драйверы приемопередатчиков LVDS-M 1, 2, первый триггер синхронизатора 3, 4, второй триггер синхронизатора 5, 6, преобразователь последовательного кода в параллельный «S-P» 7, 8, цифровой фильтр фазовой автоподстройки частоты «DPLL» 9, декодер балансных кодов 10, 11, контроллер протокола обмена «Автомат управления» 12, 13, кодер балансных кодов 14, 15, преобразователь из параллельного кода в последовательный «P-S» 16, 17; общие для обоих каналов: первый логический элемент «И» 19, первый логический элемент «ИЛИ» 18, второй логический элемент «ИЛИ» 20, контроллер «ПДП» 21.

Устройство (фиг. 1) работает следующим образом (описывается работа одного канала): на вход драйвера магистрали LVDS-M 1 поступает закодированный балансными кодами поток данных согласно заданному протоколу обмена. Дифференциальный приемник драйвера LVDS-M 1 производит перевод сигнала из дифференциальной формы в уровни стандарта «LVTTL/CMOS». Далее преобразованный сигнал поступает на два триггера синхронизатора 3, 5, которые служат для синхронизации входного сигнала с опорной частотой работы устройства. С последнего триггера синхронизатора 5 сигнал поступает на фильтр фазовой автоподстройки частоты «DPLL» 9 и преобразователь последовательного кода в параллельный «S-P» 7. «DPLL» 9 вырабатывает опорную частоту стробирования входного сигнала (фиг. 2). Частота стробирования с «DPLL» 9 поступает на преобразователь «S-Р» 7, где производится выборка слов на основе входного битового потока. Закодированное балансным кодом слово от «S-P» 7 поступает на декодер 10. Декодер 10 преобразует закодированное слово в байт данных (фиг. 3, и выявляет ошибки во время приема (верный баланс кода, отсутствие запрещенных кодов). Байт данных поступает на контроллер протокола обмена «Автомат управления» 12. Частота стробирования с «DPLL» 9 поступает на «Автомат управления» 12. На основе полученных данных от «DPLL» 9 и декодера 10 «Автомат управления» 12 восстанавливает принятые данные согласно заданному протоколу обмена и определяет ошибки приема на основе контрольной суммы «CRC8».

Во время отсутствия данных на любом из каналов или их недостоверности, а также любой неисправности канала шины с «Автомата управления» 12, 13 (DATA_OUT, ADR) находятся в состоянии логического "0", шина (CE,WE,RD) - в состоянии логической "1".

Сигналы «Автомата управления» 12, 13 первого и второго канала объединяются в логических схемах: первой схеме «ИЛИ» 18, схеме «И» 19, второй схеме «ИЛИ» 20. После объединения шины: «DATA_OUT» с выхода первой логической схемы «ИЛИ» 18; «CE, WR, RD» с выхода логической схемы «И» 19; «ADR» второй логической схемы «ИЛИ» 20 поступают на входы контроллера «ПДП» 21. Контроллер «ПДП» по внешним выводам устройства организует обмен с устройствами типа: "Микропроцессор", "ОЗУ", "ПЗУ", "Микроконтроллер", "Конечные Автоматы управления", "Регистры" (фиг. 5).

Данные из «Автомата управления» 12 поступают на вход кодера 14. Данные, закодированные балансным кодом с кодера 14, поступают на вход «Автомата управления» 12 (фиг. 4). Параллельные данные в балансном коде согласно определенному протоколу обмена с выхода «Автомата управления» 12 поступают на преобразователь данных из параллельных в последовательные «P-S» 16. С выхода «P-S» 16 закодированный битовый поток поступает на вход передатчика драйвера магистрали LVDS-M 1. Дифференциальные данные с выхода передатчика драйвера магистрали LVDS-M 1 в балансном коде поступают на внешнюю межмодульную магистраль.

Данное устройство используется в аппаратуре управления космических аппаратов в качестве контроллера внутриприборной магистрали.

Из известных автору патентных материалов и дополнительных источников информации не известен набор признаков, сходных с признаками заявляемого объекта.

1. Устройство межмодульного обмена по магистрали LVDS-M с канальным резервированием и прямым доступом в память, содержащее первый и второй каналы обмена данными, состоящие из первого триггера синхронизатора, соединенного со вторым триггером синхронизатором в первом канале, первого триггера синхронизатора и соединенного со вторым триггером синхронизатором во втором канале, фильтра фазовой автоподстройки частоты для каждого канала, соединенного со вторым триггером синхронизатором своего канала и соединенного с контроллером протокола обмена своего канала, преобразователя из последовательного кода в параллельный для каждого канала, соединенного с выходом второго триггера синхронизатора своего канала и фильтром фазовой автоподстройки частоты своего канала, отличающееся тем, что в него введен декодер балансных кодов, соединенный с преобразователем последовательного кода в параллельный и соединенный с контроллером протокола обмена.

2. Устройство по п. 1, отличающееся тем, что в него введен кодер балансных кодов, соединенный с контроллером протокола обмена.

3. Устройство по п. 1, отличающееся тем, что в него введен драйвер приема передачи LVDS-M, соединенный с первым триггером синхронизатором и преобразователем из параллельного кода в последовательный.

4. Устройство по п. 1, отличающееся тем, что в него введен контроллер прямого доступа в память, который соединен с первым логическим элементом «ИЛИ», логическим элементом «И», вторым логическим элементом «ИЛИ».

5. Устройство по п. 1, отличающееся тем, что два независимых канала объединяются по шинам: «Данные», «Адрес», «Управления» через первую логическую схему «ИЛИ», логическую схему «И» и вторую логическую схему «ИЛИ».