Устройство для определения нагрузочной способности микросхем

Иллюстрации

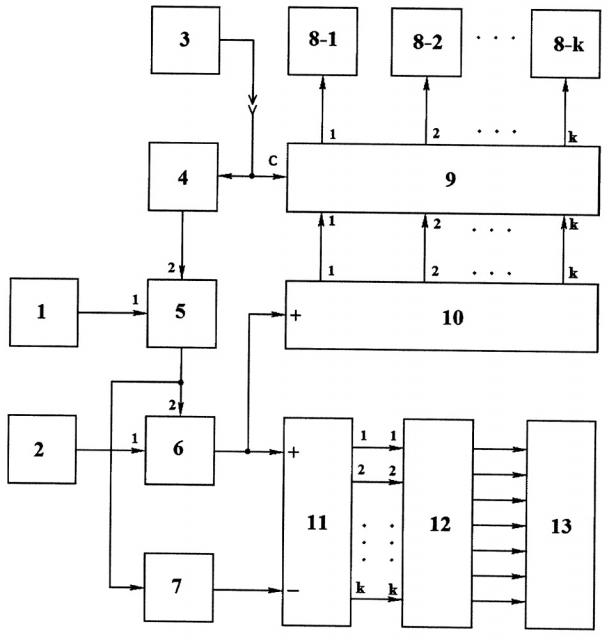

Показать всеУстройство для определения нагрузочной способности микросхем относится к области микроминиатюризации и технологии радиоэлектронной аппаратуры и может быть использовано для контроля параметров микросхем при их производстве. Устройство для определения нагрузочной способности микросхем содержит источник опорного напряжения 1, генератор прямоугольного напряжения 2, испытуемую микросхему 3, повторитель 4, компаратор 5, элемент И 6, одновибратор 7, элементы нагрузки 8-1…8-k, коммутатор 9, счетчик импульсов 10, реверсивный счетчик импульсов 11, дешифратор 12 и индикатор 13. Оно позволяет повысить точность и достоверность определения нагрузочной способности микросхем. 1 ил.

Реферат

Изобретение относится к области микроминиатюризации и технологии радиоэлектронной аппаратуры и может быть использовано для контроля параметров микросхем при их производстве.

Известен способ для определения нагрузочной способности микросхем (Фролкин В.Т., Попов Л.Н. Импульсные и цифровые устройства: Учеб. пособие для вузов. - М.: Радио и связь, 1992. - 336 с.: ил. - с. 127), связанный с нахождением наибольшего числа входов логических элементов, которые можно подключить к выходу испытуемой микросхемы без ухудшения ее параметров.

Недостатками устройств, реализующих этот способ, являются низкие точность и достоверность определения нагрузочной способности.

Наиболее близким к предлагаемому изобретению является устройство для определения нагрузочной способности дискретных схем (авторское свидетельство СССР №836606, МПК G01R 31/28, опубл. 07.06.81. Бюл. №21), содержащее коммутатор, три генератора, триггер, усилитель, индикатор, дифференцирующий элемент, элемент И и блок памяти.

Недостатками устройства являются низкие точность и достоверность определения нагрузочной способности.

В основу изобретения поставлена задача повысить точность и достоверность определения нагрузочной способности микросхем.

Данная задача решается в устройстве для определения нагрузочной способности микросхем, которое содержит элементы нагрузки, коммутатор и индикатор, а также последовательно соединенные генератор прямоугольного напряжения, элемент И и счетчик импульсов, согласно изобретению в него дополнительно введены повторитель, вход которого и сигнальный вход коммутатора объединены и подключены к выходной клемме испытуемой микросхемы, последовательно соединенные источник опорного напряжения и компаратор, второй вход которого подключен к выходу повторителя, а выход - ко второму входу элемента И, одновибратор, вход которого также подключен к выходу компаратора, реверсивный счетчик импульсов, вычитающий вход которого подключен к выходу одновибратора, а суммирующий также соединен с выходом элемента И, дешифратор, каждый из входов которого подключен к одноименному выходу реверсивного счетчика импульсов, каждый из выходов дешифратора подключен к одноименному входу индикатора, каждый из выходов счетчика импульсов подключен к одноименному входу коммутатора, каждый из выходов которого подключен к входу одноименного элемента нагрузки.

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит источник опорного напряжения 1, генератор прямоугольного напряжения 2, испытуемую микросхему 3, повторитель 4, компаратор 5, элемент И 6, одновибратор 7, элементы нагрузки 8-1…8-k, коммутатор 9, счетчик импульсов 10, реверсивный счетчик импульсов 11, дешифратор 12 и индикатор 13.

В устройстве последовательно соединены генератор прямоугольного напряжения 2, элемент И 6 и счетчик импульсов 10, а также источник опорного напряжения 1 и компаратор 5, выход которого подключен ко второму входу элемента И 6.

Вход повторителя 4 и сигнальный вход коммутатора 9 объединены и подключены к выходной клемме испытуемой микросхемы 3. Выход повторителя 4 связан со вторым входом компаратора 5.

Вход одновибратора 7 подключен также к выходу компаратора 5, а выход - к вычитающему входу реверсивного счетчика импульсов 11, суммирующий вход которого подключен также к выходу элемента И 6.

Каждый из входов дешифратора 12 подключен к одноименному выходу реверсивного счетчика импульсов 11. Каждый из выходов дешифратора 12 подключен к одноименному входу индикатора 13. Каждый из выходов счетчика импульсов 10 подключен к одноименному входу коммутатора 9. Каждый из выходов коммутатора 9 подключен к входу одноименного элемента нагрузки 8-1…8-k.

Устройство позволяет определять нагрузочную способность испытуемой микросхемы 3 по изменению высокого уровня (первый режим) и по изменению низкого уровня (второй режим) ее выходного сигнала.

В соответствии с первым режимом устройство работает следующим образом. Выходное напряжение испытуемой микросхемы 3 поступает на вход повторителя 4 и сигнальный вход коммутатора 9. Последний первоначально находится в состоянии, когда элементы нагрузки 8-1…8-k отключены от выхода испытуемой микросхемы 3. Компаратор 5 сравнивает выходное напряжение повторителя 4 (оно практически совпадает с выходным напряжением испытуемой микросхемы 3) с выходным напряжением источника опорного напряжения 1. Последнее совпадает с минимально допустимым значением напряжения высокого уровня (логической «1») выходного сигнала испытуемой микросхемы 3. На выходе компаратора 5 формируется логическая «1», если первое из сравниваемых напряжений превышает второе, в противном случае - логический «0».

В случае использования исправной испытуемой микросхемы 3, при первоначальном состоянии коммутатора 9, выходное напряжение повторителя 4 превышает напряжение источника опорного напряжения 1 и на выходе компаратора 5 формируется логическая «1». Она поступает на второй вход элемента И 6, разрешая прохождение с его первого входа на выход импульсов высокого уровня генератора прямоугольного напряжения 2. Выходные импульсы элемента И 6 поступают на входы счетчика импульсов 10 и реверсивного счетчика импульсов 11. На их выходах формируются цифровые сигналы, код которых несет информацию о числе этих импульсов. «Вес» каждого разряда счетчика 10 и реверсивного счетчика 11, начиная со второго, в два раза выше предыдущего. Сигнал с каждого из выходов счетчика 10 поступает на одноименные входы коммутатора 9.

Коммутатор 9, в соответствии с меняющимся кодом его входных сигналов, подключает элементы нагрузки 8-1…8-k к выходу испытуемой микросхемы 3, равномерно наращивая нагрузку. «Весовые» соотношения элементов нагрузки 8-1…8-k совпадают с «весовыми» соотношениями одноименных разрядов счетчика импульсов 10 и реверсивного счетчика импульсов 11.

При этом, с каждым новым переключением коммутатора 9, значение напряжения высокого уровня выходного сигнала испытуемой микросхемы 3, в связи с уменьшением сопротивления нагрузки (и возрастанием ее тока), уменьшается. До тех пор, пока это напряжение остается больше выходного напряжения источника опорного напряжения 1 (в течение всех рабочих циклов), на выходе компаратора 5 сохраняется логическая «1», поддерживающая процесс вычисления нагрузочной способности.

В противном случае на выходе компаратора 5 формируется логический «0», свидетельствующий о том, что значение выходного напряжения исследуемой микросхемы 3 вышло за пределы нормы и значение нагрузочной способности, зафиксированное реверсивным счетчиком импульсов 11 в последнем рабочем цикле, должно быть уменьшено на единицу. Для выполнения этого с выхода компаратора 5 поступает логический перепад с высокого уровня («1») на низкий («0») на вход одновибратора 7, который формирует на своем выходе импульс высокого уровня. Он поступает на инвертирующий вход реверсивного счетчика импульсов 11, уменьшая записанное в нем число на единицу.

Реверсивный счетчик импульсов 11 формирует код, который дешифратор 12 преобразует во входной код индикатора 13, производя тем самым запись числа n1, определяющего нагрузочную способность по первому режиму.

Для обеспечения второго режима работы устройства, позволяющего определять нагрузочную способность испытуемой микросхемы 3 по изменению низкого уровня ее выходного сигнала, необходимо:

- первый вход компаратора 5 подключить к выходу повторителя 4, а второй вход - к выходу источника опорного напряжения 1,

- значение выходного напряжения источника опорного напряжения 1 установить равным максимально допустимому значению напряжения низкого уровня (логического «0») выходного сигнала испытуемой микросхемы 3.

При этом, с каждым новым переключением коммутатора 9, значение напряжения низкого уровня выходного сигнала испытуемой микросхемы 3 увеличивается. До тех пор, пока это напряжение остается меньше выходного напряжения источника опорного напряжения 1 (в течение всех рабочих циклов), сохраняется процесс вычисления нагрузочной способности. Также выполняется ее коррекция на единицу. Индикатор 13 отображает число n2, определяющее нагрузочную способность по второму режиму. В остальном работа всех блоков устройства в обоих режимах одинакова.

Кроме этого, преимуществами устройства по сравнению с прототипом являются: возможность работы с микросхемами ТТЛ, ТТЛШ и МОП - серий, определение нагрузочной способности микросхем в двух режимах работы не меняя состав его блоков, обеспечение автоматического режима работы и адаптированность к смене испытуемых микросхем 3 и элементов нагрузки 8-1…8-k.

Устройство для определения нагрузочной способности микросхем, содержащее элементы нагрузки, коммутатор и индикатор, а также последовательно соединенные генератор прямоугольного напряжения, элемент И и счетчик импульсов, отличающееся тем, что в него дополнительно введены повторитель, вход которого и сигнальный вход коммутатора объединены и подключены к выходной клемме испытуемой микросхемы, последовательно соединенные источник опорного напряжения и компаратор, второй вход которого подключен к выходу повторителя, а выход - ко второму входу элемента И, одновибратор, вход которого также подключен к выходу компаратора, реверсивный счетчик импульсов, вычитающий вход которого подключен к выходу одновибратора, а суммирующий также соединен с выходом элемента И, дешифратор, каждый из входов которого подключен к одноименному выходу реверсивного счетчика импульсов, каждый из выходов дешифратора подключен к одноименному входу индикатора, каждый из выходов счетчика импульсов подключен к одноименному входу коммутатора, каждый из выходов которого подключен к входу одноименного элемента нагрузки.