Устройство формирования изображений

Иллюстрации

Показать всеИзобретение относится к устройству формирования изображений. Технический результат заключается в обеспечении линии управления для каждой ячейки в модуле формирования изображений. Предложен элемент формирования изображений, содержащий: модуль формирования изображений, который имеет: множество групп, каждая из которых включает в себя, по меньшей мере, один пиксель; и множество модулей считывания сигналов, каждый из которых обеспечен для каждой из групп и считывает сигнал из пикселя; и модуль управления, который управляет модулем считывания сигналов в, по меньшей мере, одной группе из множества групп. Каждая из множества групп может включать в себя множество пикселей. Модуль управления может выбирать, по меньшей мере, одну группу из множества групп и управлять модулем считывания сигналов посредством использования параметра управления, который отличается от параметра управления, который используется для другой группы из множества групп. 3 н. и 21 з.п. ф-лы, 92 ил.

Реферат

УРОВЕНЬ ТЕХНИКИ

1. ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Настоящее изобретение относится к устройству формирования изображений.

2. ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

[0002] Известен модуль формирования изображений, в котором соединены микросхема формирования изображений с освещением с задней стороны и микросхема обработки сигналов, через столбиковые микровыводы, для каждого модуля ячейки, включающего в себя множество пикселов.

ДОКУМЕНТЫ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

ПАТЕНТНЫЕ ДОКУМЕНТЫ

Патентный документ 1

Публикация заявки на патент Японии № 2006-49361

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0003] Предусмотрена линия управления для каждой ячейки в модуле формирования изображений. Тем не менее, период накопления электрического заряда и считывание пиксельных сигналов не управляются непрерывно на основе ячейка за ячейкой.

[0004] Первый аспект настоящего изобретения предоставляет элемент формирования изображений, содержащий: модуль формирования изображений, который имеет: множество групп, каждая из которых включает в себя, по меньшей мере, один пиксел; и множество модулей считывания сигналов, каждый из которых обеспечен для каждой из групп и считывает сигнал из пиксела; и модуль управления, который управляет модулем считывания сигналов в, по меньшей мере, одной группе из множества групп.

[0005] Второй аспект настоящего изобретения предоставляет элемент формирования изображений, содержащий: модуль формирования изображений, который имеет: множество групп, каждая из которых включает в себя, по меньшей мере, один пиксел; и множество модулей считывания сигналов, каждый из которых обеспечен для каждой из групп и считывает сигнал из пиксела; и множество модулей управления, каждый из которых обеспечен для каждой из групп и управляет модулем считывания сигналов на основе сигнала из пиксела.

[0006] Третий аспект настоящего изобретения предоставляет элемент формирования изображений, содержащий: модуль формирования изображений, имеющий область формирования изображений, в которой обеспечены первый пиксел и второй пиксел, первую схему считывания, которая считывает первый пиксельный сигнал, выводимый из первого пиксела, и вторую схему считывания, которая считывает второй пиксельный сигнал, выводимый из второго пиксела; первый вычислительный модуль, который вычисляет первое значение оценки на основе первого пиксельного сигнала; второй вычислительный модуль, который вычисляет второе значение оценки на основе второго пиксельного сигнала; первый модуль управления, который выполняет управление для экспозиции или считывания первого пиксела на основе первого значения оценки; и второй модуль управления, который выполняет управление для экспозиции или считывания второго пиксела на основе второго значения оценки.

[0007] Четвертый аспект настоящего изобретения предоставляет элемент формирования изображений, содержащий: модуль формирования изображений, который имеет: множество групп, каждая из которых включает в себя, по меньшей мере, один пиксел; и множество модулей считывания сигналов, каждый из которых обеспечен для каждой из групп и считывает сигнал из пиксела; и множество вычислительных модулей, которые обеспечены для каждой из групп и передают информацию относительно управления модулем считывания сигналов в модуль обработки изображений, который выполняет обработку изображений на упомянутом сигнале.

[0008] Пятый аспект настоящего изобретения предоставляет элемент формирования изображений, содержащий: модуль формирования изображений, имеющий область формирования изображений, в которой располагаются первый пиксел и второй пиксел, первую схему считывания, которая считывает первый пиксельный сигнал, выводимый из первого пиксела, и вторую схему считывания, которая считывает второй пиксельный сигнал, выводимый из второго пиксела; первый вычислительный модуль, который вычисляет первое значение оценки на основе первого пиксельного сигнала и передает вычисленное первое значение оценки на следующем этапе в модуль обработки изображений, который выполняет обработку изображений на первых пиксельных данных, которые соответствуют первому пиксельному сигналу; и второй вычислительный модуль, который вычисляет второе значение оценки на основе второго пиксельного сигнала и передает вычисленное второе значение оценки на следующем этапе в модуль обработки изображений, который выполняет обработку изображений на вторых пиксельных данных, которые соответствуют второму пиксельному сигналу.

[0009] Шестой аспект настоящего изобретения предоставляет элемент формирования изображений, содержащий: модуль формирования изображений, который имеет множество групп, каждая из которых включает в себя, по меньшей мере, один пиксел; и модуль хранения, который имеет множество блоков хранения, которые обеспечены согласно множеству групп и сохраняют сигнал из пиксела в надлежащей соответствующей группе и сохраняют сигнал из пиксела в группе, отличной от надлежащей соответствующей группы.

[0010] Раздел "Сущность изобретения" не обязательно описывает все требуемые признаки вариантов осуществления настоящего изобретения. Настоящее изобретение также может представлять собой субкомбинацию признаков, описанных выше.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0011] Фиг. 1 является видом в сечении МОП-элемента формирования изображений с освещением с задней стороны согласно настоящему варианту осуществления.

Фиг. 2 является схемой для пояснения пиксельной матрицы и единичной группы микросхемы формирования изображений.

Фиг. 3 является схематическим видом, который соответствует единичной группе микросхемы формирования изображений.

Фиг. 4 является блок-схемой, показывающей функциональную конфигурацию элемента формирования изображений.

Фиг. 5 является блок-схемой, показывающей конфигурацию устройства формирования изображений согласно настоящему варианту осуществления.

Фиг. 6 является функциональной блок-схемой модуля обработки изображений.

Фиг. 7 является блок-схемой последовательности операций способа, которая иллюстрирует операции устройства формирования изображений для того, чтобы формировать и записывать движущееся изображение.

Фиг. 8 иллюстрирует один пример изображения, сформированного посредством элемента формирования изображений.

Фиг. 9 иллюстрирует один пример изображения, сформированного посредством элемента формирования изображений.

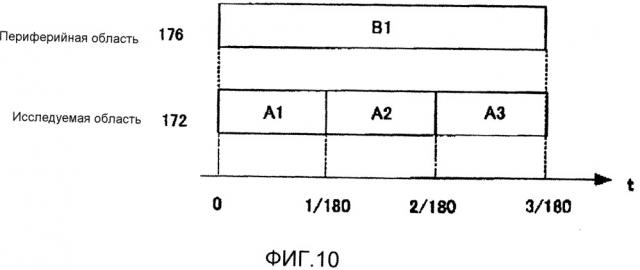

Фиг. 10 иллюстрирует взаимосвязь между соответствующими частотами кадров и тактированием вывода сигналов изображений.

Фиг. 11 схематично иллюстрирует движущееся изображение в исследуемой области и движущееся изображение в периферийной области, сформированные посредством модуля формирования движущихся изображений.

Фиг. 12 иллюстрирует один пример информации заголовка, добавляемой посредством модуля формирования движущихся изображений.

Фиг. 13 является блок-схемой последовательности операций способа, которая иллюстрирует операции устройства формирования изображений для того, чтобы воспроизводить и отображать движущееся изображение.

Фиг. 14 является блок-схемой последовательности операций способа, которая иллюстрирует другой пример операций устройства формирования изображений для того, чтобы формировать и записывать движущееся изображение.

Фиг. 15 иллюстрирует пример пикселов, которые должны считываться с показателем прореживания в 0,5 в одной единичной группе.

Фиг. 16 является блок-схемой последовательности операций способа, которая иллюстрирует операции устройства формирования изображений для того, чтобы воспроизводить и отображать движущееся изображение.

Фиг. 17 является схемой для пояснения примера сцены и разделения на области.

Фиг. 18 является схемой для пояснения управления накоплением электрического заряда для соответствующих областей, разделенных в примере на фиг. 17.

Фиг. 19 является таблицей, которая указывает взаимосвязь между числом интегрирований и динамическим диапазоном.

Фиг. 20 является блок-схемой последовательности операций способа, показывающей обработку операций формирования изображений.

Фиг. 21 является блок-схемой, которая иллюстрирует конкретную конфигурацию микросхемы обработки сигналов в качестве одного примера.

Фиг. 22 является видом в сечении другого МОП-элемента формирования изображений с освещением с задней стороны согласно настоящему варианту осуществления.

Фиг. 23 является схемой для пояснения пиксельной матрицы и единичной группы микросхемы формирования изображений.

Фиг. 24 является схематическим видом, который соответствует единичной группе микросхемы формирования изображений.

Фиг. 25 является блок-схемой, показывающей конфигурацию устройства формирования изображений согласно настоящему варианту осуществления.

Фиг. 26 является блок-схемой, которая иллюстрирует конкретную конфигурацию микросхемы обработки сигналов в качестве одного примера.

Фиг. 27 показывает один пример функциональных блоков арифметической схемы 1415.

Фиг. 28 иллюстрирует один пример соответствия между межкадровыми разностями d и частотами f кадров.

Фиг. 29 иллюстрирует один пример изображения, сформированного посредством элемента формирования изображений.

Фиг. 30 иллюстрирует один пример изображения, сформированного посредством элемента формирования изображений.

Фиг. 31 показывает один пример функциональных блоков другой арифметической схемы.

Фиг. 32 иллюстрирует пример пикселов 1188, которые должны считываться с показателем прореживания в 0,5 в одной единичной группе.

Фиг. 33 иллюстрирует один пример функциональных блоков еще одной другой арифметической схемы.

Фиг. 34 схематично иллюстрирует взаимосвязь между усилениями и пиксельными сигналами.

Фиг. 35 является видом в сечении МОП-элемента формирования изображений с освещением с задней стороны согласно настоящему варианту осуществления.

Фиг. 36 является схемой для пояснения пиксельной матрицы и пиксельного блока микросхемы формирования изображений.

Фиг. 37 является схематическим видом, который соответствует пиксельному блоку микросхемы формирования изображений.

Фиг. 38 является схемой, которая иллюстрирует часть конфигурации элемента формирования изображений и его пример работы.

Фиг. 39 является блок-схемой, показывающей конфигурацию устройства формирования изображений согласно настоящему варианту осуществления.

Фиг. 40 является функциональной блок-схемой модуля обработки изображений.

Фиг. 41 является блок-схемой последовательности операций способа, которая иллюстрирует операции устройства формирования изображений для того, чтобы формировать и записывать движущееся изображение.

Фиг. 42 иллюстрирует один пример изображения, сформированного посредством элемента формирования изображений.

Фиг. 43 иллюстрирует один пример изображения, сформированного посредством элемента формирования изображений.

Фиг. 44 иллюстрирует взаимосвязь между соответствующими частотами кадров и тактированием вывода сигналов изображений.

Фиг. 45 схематично иллюстрирует движущееся изображение в исследуемой области и движущееся изображение в периферийной области, сформированные посредством модуля формирования движущихся изображений.

Фиг. 46 иллюстрирует один пример информации заголовка, добавляемой посредством модуля формирования движущихся изображений.

Фиг. 47 является блок-схемой последовательности операций способа, которая иллюстрирует операции устройства формирования изображений для того, чтобы воспроизводить и отображать движущееся изображение.

Фиг. 48 является блок-схемой последовательности операций способа, которая иллюстрирует другой пример операций устройства формирования изображений для того, чтобы формировать и записывать движущееся изображение.

Фиг. 49 иллюстрирует пример пикселов, которые должны считываться с показателем прореживания в 0,5 в одном пиксельном блоке.

Фиг. 50 является блок-схемой последовательности операций способа, которая иллюстрирует операции устройства формирования изображений для того, чтобы воспроизводить и отображать движущееся изображение.

Фиг. 51A является схемой для пояснения сцены.

Фиг. 51B является схемой для пояснения разделения на области.

Фиг. 52 является схемой для пояснения управления накоплением электрического заряда для соответствующих областей, разделенных в примере на фиг. 51B.

Фиг. 53 является таблицей, которая указывает взаимосвязь между числом интегрирований и динамическим диапазоном.

Фиг. 54 является блок-схемой последовательности операций способа, показывающей обработку операций формирования изображений.

Фиг. 55 является блок-схемой, которая иллюстрирует конкретную конфигурацию микросхемы обработки сигналов в качестве одного примера.

Фиг. 56 является блок-схемой, показывающей конфигурацию модуля обработки периферийных пиксельных данных.

Фиг. 57 является блок-схемой, которая иллюстрирует один пример конфигурации арифметической схемы.

Фиг. 58 является блок-схемой последовательности операций способа, которая иллюстрирует пример операций арифметической схемы.

Фиг. 59 иллюстрирует конфигурацию массива данных, сформированного посредством выходной схемы.

Фиг. 60 иллюстрирует контент массива данных, проиллюстрированного на фиг. 59.

Фиг. 61 является видом в сечении МОП-элемента формирования изображений с освещением с задней стороны согласно настоящему варианту осуществления.

Фиг. 62 является схемой для пояснения пиксельной матрицы и пиксельного блока микросхемы формирования изображений.

Фиг. 63 является схематическим видом, который соответствует пиксельному блоку микросхемы формирования изображений.

Фиг. 64A является схемой, которая иллюстрирует часть конфигурации элемента формирования изображений и его пример работы.

Фиг. 64B является схемой, которая иллюстрирует другой пример работы элемента формирования изображений.

Фиг. 64C является схемой, которая иллюстрирует другой пример работы элемента формирования изображений.

Фиг. 65 является блок-схемой, показывающей конфигурацию устройства формирования изображений согласно настоящему варианту осуществления.

Фиг. 66 является функциональной блок-схемой модуля обработки изображений.

Фиг. 67 является блок-схемой последовательности операций способа, которая иллюстрирует операции устройства формирования изображений для того, чтобы формировать и записывать движущееся изображение.

Фиг. 68 иллюстрирует один пример изображения, сформированного посредством элемента формирования изображений.

Фиг. 69 иллюстрирует один пример изображения, сформированного посредством элемента формирования изображений.

Фиг. 70 иллюстрирует взаимосвязь между соответствующими частотами кадров и тактированием вывода сигналов изображений.

Фиг. 71 схематично иллюстрирует движущееся изображение в исследуемой области и движущееся изображение в периферийной области, сформированные посредством модуля формирования движущихся изображений.

Фиг. 72 иллюстрирует один пример информации заголовка, добавляемой посредством модуля формирования движущихся изображений.

Фиг. 73 является блок-схемой последовательности операций способа, которая иллюстрирует операции устройства формирования изображений для того, чтобы воспроизводить и отображать движущееся изображение.

Фиг. 74 является видом сверху пиксельной области элемента формирования изображений и его примера работы.

Фиг. 75 является видом сверху другой конфигурации пиксельной области элемента формирования изображений и его примера работы.

Фиг. 76 является видом сверху другой конфигурации пиксельной области элемента формирования изображений и его примера работы.

Фиг. 77 является видом сверху другой конфигурации пиксельной области элемента формирования изображений и его примера работы.

Фиг. 78 является видом сверху другой конфигурации пиксельной области элемента формирования изображений и его примера работы.

Фиг. 79 является блок-схемой последовательности операций способа, которая иллюстрирует другой пример операций устройства формирования изображений для того, чтобы формировать и записывать движущееся изображение.

Фиг. 80 иллюстрирует пример пикселов, которые должны считываться с показателем прореживания в 0,5.

Фиг. 81 является блок-схемой последовательности операций способа, которая иллюстрирует операции устройства формирования изображений для того, чтобы воспроизводить и отображать движущееся изображение.

Фиг. 82A является схемой для пояснения сцены.

Фиг. 82B является схемой для пояснения разделения на области.

Фиг. 83 является схемой для пояснения управления накоплением электрического заряда для соответствующих областей, разделенных в примере на фиг. 82B.

Фиг. 84 является таблицей, которая указывает взаимосвязь между числом интегрирований и динамическим диапазоном.

Фиг. 85 является блок-схемой последовательности операций способа, показывающей обработку операций формирования изображений.

Фиг. 86 является блок-схемой, которая иллюстрирует конкретную конфигурацию микросхемы обработки сигналов в качестве одного примера.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0012] В дальнейшем в этом документе описываются некоторые вариант(ы) осуществления настоящего изобретения. Вариант(ы) осуществления не ограничивают изобретение согласно формуле изобретения, и все комбинации признаков, описанных в варианте(ах) осуществления, не обязательно существенны для средств, обеспеченных посредством аспектов изобретения.

[0013] Фиг. 1 является видом в сечении элемента 100 формирования изображений с освещением с задней стороны согласно настоящему варианту осуществления. Элемент 100 формирования изображений включает в себя микросхему 113 формирования изображений, которая выводит пиксельный сигнал, соответствующий падающему свету, микросхему 111 обработки сигналов, которая обрабатывает пиксельный сигнал, и микросхему 112 запоминающего устройства, которая сохраняет пиксельный сигнал. Эти микросхема 113 формирования изображений, микросхема 111 обработки сигналов и микросхема 112 запоминающего устройства располагаются слоями и электрически соединяются между собой через проводящие столбиковые выводы 109, к примеру, Cu.

[0014] Следует отметить, что как проиллюстрировано, падающий свет падает, главным образом, в положительном направлении по оси Z, которое указывается с помощью обведенной стрелки. В настоящем варианте осуществления, поверхность микросхемы 113 формирования изображений на стороне, на которую падает падающий свет, называется задней стороной. Кроме того, как указано с помощью осей координат, направление влево на чертеже, которое является ортогональным к оси Z, упоминается в качестве положительного направления по оси X, а направление вперед на чертеже, которое является ортогональным к осям Z и X, упоминается в качестве положительного направления по оси Y. На нескольких чертежах, упомянутых ниже, оси координат отображаются таким образом, что ориентация каждого чертежа может быть известной на основе осей координат на фиг. 1.

[0015] Один пример микросхемы 113 формирования изображений представляет собой МОП-датчик изображений с освещением с задней стороны. PD-слой 106 располагается на задней стороне слоя 108 межсоединений. PD-слой 106 имеет множество PD 104 (фотодиодов), которые располагаются двумерным образом и накапливают электрические заряды согласно падающему свету, и транзисторов 105, обеспеченных согласно PD 104.

[0016] Цветные светофильтры 102 обеспечены на стороне падения падающего света PD-слоя 106 через пассивирующую пленку 103. Предусмотрено множество типов цветных светофильтров 102, которые дают возможность прохождения взаимно различных диапазонов длин волн, и цветные светофильтры 102 упорядочиваются, в частности, согласно соответствующим PD 104. Ниже описываются матрицы цветных светофильтров 102. Набор из цветного светофильтра 102, PD 104 и транзистора 105 формирует один пиксел.

[0017] Микролинза 101 предоставляется согласно каждому пикселу на стороне падения падающего света цветного светофильтра 102. Микролинза 101 конденсирует падающий свет к соответствующему PD 104.

[0018] Слой 108 межсоединений имеет межсоединения 107, которые передают пиксельный сигнал из PD-слоя 106 в микросхему 111 обработки сигналов. Межсоединение 107 может быть многослойным и может быть снабжено пассивным элементом и активным элементом.

[0019] Множество столбиковых выводов 109 располагается на поверхности слоя 108 межсоединений. Множество столбиковых выводов 109 совмещается с множеством столбиковых выводов 109, которые обеспечены на противостоящей поверхности микросхемы 111 обработки сигналов, и, например, микросхема 113 формирования изображений и микросхема 111 обработки сигналов прижимаются друг к другу; за счет этого совмещенные столбиковые выводы 109 подвергаются термокомпрессионной сварке и электрически соединяются между собой.

[0020] Аналогично, множество столбиковых выводов 109 располагается на взаимно противостоящих поверхностях микросхемы 111 обработки сигналов и микросхемы 112 запоминающего устройства. Эти столбиковые выводы 109 совмещаются друг с другом, и, например, микросхема 111 обработки сигналов и микросхема 112 запоминающего устройства прижимаются друг к другу; за счет этого совмещенные столбиковые выводы 109 подвергаются термокомпрессионной сварке и электрически соединяются между собой.

[0021] Следует отметить, что соединение между столбиковыми выводами 109 не ограничивается соединением столбиковых выводов из Cu посредством диффузии из твердой фазы, и может применяться соединение столбиковых микровыводов посредством припойного соединения. Кроме того, приблизительно один столбиковый вывод 109 может предоставляться, например, для каждой единичной группы, описанной ниже. Соответственно, размер столбиковых выводов 109 может превышать шаг PD 104. Кроме того, в периферийной области, отличной от пиксельной области, в которой упорядочиваются пикселы, также может предоставляться столбиковый вывод, который превышает столбиковые выводы 109, соответствующие пиксельной области.

[0022] Микросхема 111 обработки сигналов имеет TSV 110 (переходное отверстие в кремнии), которое соединяет схемы, которые обеспечены на передней стороне и задней стороне, соответственно. TSV 110 предпочтительно предоставляется в периферийной области. Кроме того, TSV 110 также может предоставляться в периферийной области микросхемы 113 формирования изображений и микросхемы 112 запоминающего устройства.

[0023] Фиг. 2 является схемой для пояснения пиксельной матрицы и единичной группы 131 микросхемы 113 формирования изображений. В частности, данные показывают строение микросхемы 113 формирования изображений, наблюдаемое с задней стороны. Матрица из двадцати миллионов пикселов или более размещается массивом в пиксельной области. В настоящем варианте осуществления, смежные четыре пиксела (четыре пиксела, 16 пикселов) формируют одну единичную группу 131. Линии сетки координат на чертеже показывают такой принцип, что смежные пикселы группируются с возможностью формировать единичную группу 131. Число пикселов, которые формируют единичную группу 131, не ограничено этим, и может составлять приблизительно 1000, например, тридцать два пиксела (шестьдесят четыре пиксела либо больше или меньше).

[0024] Как проиллюстрировано в частично укрупненном виде пиксельной области, единичная группа 131 включает в себя, в верхней левой, верхней правой, нижней левой и нижней правой частях, четыре так называемых байеровских матрицы, каждая из которых включает в себя четыре пиксела, включая пикселы Gb, Gr зеленого цвета, пиксел B синего цвета и пиксел R красного цвета. Пикселы зеленого цвета имеют зеленые светофильтры в качестве цветных светофильтров 102 и принимают свет в диапазоне длин волн зеленого цвета падающего света. Аналогично, пиксел синего цвета имеет синий светофильтр в качестве цветного светофильтра 102 и принимает свет в диапазоне длин волн синего цвета, и пиксел красного цвета имеет красный светофильтр в качестве цветного светофильтра 102 и принимает свет в диапазоне длин волн красного цвета.

[0025] В настоящем варианте осуществления, выбирается, по меньшей мере, одна единичная группа из множества единичных групп 131, и пикселы, включенные в каждую единичную группу, управляются согласно параметрам управления, которые отличаются от параметров управления для других единичных групп. Примеры параметров управления включают в себя частоту кадров, показатель прореживания, число суммированных строк или число суммированных столбцов, пиксельные сигналы которых суммируются, период или число накоплений электрических зарядов, число битов для оцифровки и т.п. Кроме того, параметры управления могут представлять собой параметры при обработке изображений, выполняемой после получения сигналов изображений из пиксела.

[0026] Фиг. 3 является схематическим видом, который соответствует единичной группе 131 микросхемы 113 формирования изображений. На чертеже прямоугольник, который указывается с помощью пунктирных линий, типично представляет схему, которая соответствует одному пикселу. Следует отметить, что, по меньшей мере, часть каждого транзистора, поясненного ниже, соответствует транзистору 105 на фиг. 1.

[0027] Как описано выше, единичная группа 131 формируется с 16 пикселами. 16 PD 104, которые соответствуют надлежащим пикселам, соединяются с соответствующими транзисторами 302 переноса, и затвор каждого транзистора 302 переноса соединяется с TX межсоединением 307, в которое подаются импульсы переноса. В настоящем варианте осуществления, TX межсоединение 307 соединяется совместно с 16 транзисторами 302 переноса.

[0028] Сток каждого транзистора 302 переноса соединяется с истоком соответствующего транзистора 303 сброса, а также так называемая плавающая диффузионная область FD между стоком транзистора 302 переноса и истоком транзистора 303 сброса соединяется с затвором усиливающего транзистора 304. Сток транзистора 303 сброса соединяется с Vdd межсоединением 310, в которое подается напряжение питания, и его затвор соединяется с межсоединением 306 сброса, в которое подаются импульсы сброса. В настоящем варианте осуществления, межсоединение 306 сброса соединяется совместно с 16 транзисторами 303 сброса.

[0029] Сток каждого усиливающего транзистора 304 соединяется с Vdd межсоединением 310, в которое подается напряжение питания. Кроме того, исток каждого усиливающего транзистора 304 соединяется со стоком соответствующего транзистора 305 выбора. Затвор каждого транзистора выбора соединяется с межсоединением 308 декодера, в которое подаются импульсы выбора. В настоящем варианте осуществления, межсоединение 308 декодера предоставляется независимо для каждого из 16 транзисторов 305 выбора. Затем, исток каждого транзистора выбора 305 соединяется с общим выходным межсоединением 309. Источник 311 тока нагрузки подает ток в выходное межсоединение 309. Иными словами, выходное межсоединение 309 для транзисторов 305 выбора формируется посредством истокового повторителя. Следует отметить, что источник 311 тока нагрузки может предоставляться на стороне микросхемы 113 формирования изображений или на стороне микросхемы 111 обработки сигналов.

[0030] Здесь, поясняется последовательность операций от начала накопления электрического заряда до вывода пикселов после завершения накопления. Когда импульсы сброса применяются к транзистору 303 сброса через межсоединение 306 сброса, и одновременно импульсы переноса применяются к транзистору 302 переноса через TX межсоединение 307, сбрасывается потенциал PD 104 и плавающей диффузионной области FD.

[0031] Когда применение импульсов переноса прекращается, PD 104 преобразует принимаемый падающий свет в электрические заряды, которые затем накапливаются. После этого, когда импульсы переноса применяются снова в состоянии, в котором импульсы сброса не применяются, накопленные электрические заряды переносятся в плавающую диффузионную область FD, и потенциал плавающей диффузионной области FD изменяется с потенциала сброса на потенциал сигнала после накопления электрического заряда. Затем, когда импульсы выбора применяются к транзистору 305 выбора через межсоединение 308 декодера, изменение в потенциале сигнала плавающей диффузионной области FD передается в выходное межсоединение 309 через усиливающий транзистор 304 и транзистор 305 выбора. В силу этого, пиксельные сигналы, соответствующие потенциалу сброса и потенциалу сигнала, выводятся из единичного пиксела в выходное межсоединение 309.

[0032] Как проиллюстрировано, в настоящем варианте осуществления, межсоединение 306 сброса и TX межсоединение 307 являются общими для 16 пикселов, которые формируют единичную группу 131. Иными словами, импульсы сброса и импульсы переноса, соответственно, применяются одновременно ко всем 16 пикселам.

Соответственно, все пикселы, которые формируют единичную группу 131, начинают накопление электрического заряда при одном и том же тактировании и завершают накопление электрического заряда при одном и том же тактировании. Тем не менее, следует отметить, что пиксельные сигналы, которые соответствуют накопленным электрическим зарядам, выводятся избирательно в выходное межсоединение 309 при последовательном применении импульсов выбора к соответствующим транзисторам 305 выбора. Кроме того, межсоединение 306 сброса, TX межсоединение 307 и выходное межсоединение 309 обеспечены отдельно для каждой единичной группы 131.

[0033] Посредством конфигурирования схемы на основе единичной группы 131 таким способом, период накопления электрического заряда может управляться для каждой единичной группы 131. Другими словами, смежным единичным группам 131 может инструктироваться выводить пиксельные сигналы в течение различных периодов накопления электрического заряда. Кроме того, посредством инструктирования одной единичной группе 131 повторять накопление электрического заряда несколько раз и выводить пиксельный сигнал каждый раз в момент, когда другой единичной группе 131 инструктируется выполнять накопление электрического заряда один раз, этим единичным группам 131 может инструктироваться выводить соответствующие кадры для движущегося изображения на различных частотах кадров.

[0034] Фиг. 4 является блок-схемой, которая иллюстрирует функциональную конфигурацию элемента 100 формирования изображений. Аналоговый мультиплексор 411 последовательно выбирает 16 PD 104, которые формируют единичную группу 131, и инструктирует вывод их соответствующих пиксельных сигналов в выходное межсоединение 309, предоставленное согласно единичной группе 131. Мультиплексор 411 формируется в микросхеме 113 формирования изображений вместе с PD 104.

[0035] Пиксельный сигнал, который выводится через мультиплексор 411, подвергается двойной коррелированной дискретизации (CDS) и аналого-цифровому (A/D) преобразованию посредством схемы 412 обработки сигналов, которая формируется в микросхеме 111 обработки сигналов и выполняет CDS и аналогово-цифровое преобразование. Подвергнутый аналого-цифровому преобразованию пиксельный сигнал передается в демультиплексор 413 и сохраняется в пиксельном запоминающем устройстве 414, которое соответствует надлежащему пикселу. Каждое пиксельное запоминающее устройство 414 имеет емкость, которая дает возможность сохранения пиксельных сигналов, которые соответствуют максимальному числу интегрирований, описанному ниже. Демультиплексор 413 и пиксельное запоминающее устройство 414 формируются в микросхеме 112 запоминающего устройства.

[0036] Арифметическая схема 415 обрабатывает пиксельный сигнал, сохраненный в пиксельном запоминающем устройстве 414, и передает его в модуль обработки изображений на следующем этапе. Арифметическая схема 415 может предоставляться в микросхеме 111 обработки сигналов или микросхеме 112 запоминающего устройства. Следует отметить, что хотя на чертеже проиллюстрированы соединения для одной единичной группы 131, соединения фактически существуют для каждой единичной группы 131 и работают параллельно. Тем не менее, следует отметить, что арифметическая схема 415 может не существовать для каждой единичной группы 131 и, например, одна арифметическая схема 415 может последовательно выполнять обработку посредством последовательного обращения к значениям пиксельных запоминающих устройств 414, которые соответствуют надлежащим единичным группам 131.

[0037] Как описано выше, выходное межсоединение 309 предоставляется согласно каждой из единичных групп 131. Поскольку элемент 100 формирования изображений формируется посредством расположения слоями микросхемы 113 формирования изображений, микросхемы 111 обработки сигналов и микросхемы 112 запоминающего устройства, выходное межсоединение 309 может маршрутизироваться без увеличения размера каждой микросхемы в направлении плоскости посредством использования межмикросхемных электрических соединений, которые используют столбиковые выводы 109 для межсоединения.

[0038] Фиг. 5 является блок-схемой, иллюстрирующей конфигурацию устройства формирования изображений согласно настоящему варианту осуществления. Устройство 500 формирования изображений включает в себя линзу 520 для формирования изображений в качестве оптической системы формирования изображений, и линза 520 для формирования изображений направляет световой поток объекта, который падает вдоль оптической оси OA, на элемент 100 формирования изображений. Линза 520 для формирования изображений может представлять собой сменную линзу, которая может присоединяться/отсоединяться к/от устройства 500 формирования изображений. Устройство 500 формирования изображений включает в себя, главным образом, элемент 100 формирования изображений, модуль 501 управления системой, модуль 502 возбуждения, фотометрический модуль 503, оперативное запоминающее устройство 504, модуль 505 записи и модуль 506 отображения.

[0039] Линза 520 для формирования изображений конфигурируется с множеством групп оптических линз и формирует изображение светового потока объекта из сцены около своей фокальной плоскости. Следует отметить, что, на фиг. 5, линза 520 для формирования изображений типично показывается с помощью одной виртуальной линзы, которая помещается около зрачка. Модуль 502 возбуждения представляет собой схему управления, которая выполняет управление накоплением электрического заряда, к примеру, управление тактированием и управление областями для элемента 100 формирования изображений согласно инструкциям из модуля 501 управления системой. В этом смысле, можно сказать, что модуль 502 возбуждения выполняет функции модуля управления элемента формирования изображений, который инструктирует элементу 100 формирования изображений выполнять накопление электрического заряда и выводить пиксельные сигналы.

[0040] Элемент 100 формирования изображений передает пиксельные сигналы в модуль 511 обработки изображений модуля 501 управления системой. Модуль 511 обработки изображений выполняет различные типы обработки изображений посредством использования оперативного запоминающего устройства 504 в качестве рабочего пространства и формирует данные изображений. Например, когда формируются данные изображений в JPEG-формате файла, процессы сжатия выполняются после того, как цветовые видеосигналы формируются из сигналов, получаемых из байеровских матриц. Сформированные данные изображений записываются в модуль 505 записи и преобразуются в сигналы для отображения и отображаются на модуле 506 отображения в течение предварительно установленного периода времени.

[0041] Фотометрический модуль 503 определяет распределение яркости сцены до последовательности формирования изображений для формирования данных изображений. Фотометрический модуль 503 включает в себя AE-датчик, например, приблизительно из одного миллиона пикселов. Вычислительный модуль 512 модуля 501 управления системой вычисляет яркость соответствующих областей в сцене после приема вывода фотометрического модуля 503. Вычислительный модуль 512 определяет скорость срабатывания затвора, значение раскрытия диафрагмы и ISO-скорость согласно вычисленному распределению яркости. Элемент 100 формирования изображений может выполнять вторую функцию