Устройство связи, устройство демодуляции, устройство восстановления несущей, устройство компенсации фазовой ошибки, способ компенсации фазовой ошибки и запоминающий носитель, на котором сохранена программа компенсации фазовой ошибки

Иллюстрации

Показать всеИзобретение относится к системам связи и может быть использовано как устройство компенсации фазовой ошибки устройства восстановления несущей для демодулятора, используемого в системах связи с квадратурной амплитудной модуляцией. Технический результат – увеличение пропускной способности и повышение качества передачи данных путем уменьшения частоты появления ошибочных битов в неблагоприятном шумовом окружении, преимущественно обусловленном фазовыми шумами или тепловыми шумами. Устройство компенсации фазовой ошибки содержит первый и второй фильтры, которые формируют значения разности фаз и значение оценки фазовой ошибки соответственно в прямой и обратной последовательностях принятых символов, средство сложения фазовых ошибок, которое формирует значение оценки фазовой ошибки на основе значений оценки фазовых ошибок и одного из значений разности фаз и средство компенсации фазовой ошибки в принятых символах на основе оценки фазовой ошибки, полученной в средстве сложения. 6 н. и 4 з.п. ф-лы, 20 ил.

Реферат

[Область техники]

[0001]

Настоящее изобретение относится к устройству связи, устройству демодуляции, устройству восстановления несущей, устройству компенсации фазовой ошибки, способу управления для устройства компенсации фазовой ошибки и к запоминающему носителю, на котором сохранена управляющая программа для устройства компенсации фазовой ошибки.

[Предшествующий уровень техники]

[0002]

В цифровой связи в качестве способа модуляции и демодуляции для выполнения эффективной передачи данных известен способ квадратурной амплитудной модуляции (QAM), в котором информация о фазе и информация об амплитуде используются для идентификации данных. В последние годы в качестве потребности увеличения пропускной способности в системе связи существовала потребность повышения уровня модуляции. Однако имеется проблема в том, что повышение уровня модуляции может увеличить вероятность ошибки передачи, обусловленной шумом, и снизить устойчивость к шуму. В частности, фазовый шум, преимущественно вызванный опорным генератором (LO; гетеродин) в устройстве передачи и в устройстве приема, может увеличить неопределенность информации о фазе и может значительно ухудшить частоту появления ошибочных битов (BER). В связи с вышеизложенным для выполнения передачи данных с повышенной надежностью по способу многоуровневой QAM, в котором количество сигнальных точек равно, например, 256 или больше, необходимо с высокой точностью оценивать фазовую ошибку, обусловленную фазовым шумом, и компенсировать эту фазовую ошибку. Одновременно необходимо повысить устойчивость к ошибке, вызванной другими факторами, например тепловым шумом.

[0003]

В вышеупомянутой области техники известно устройство демодуляции, в котором фазовая ошибка компенсируется фазовой автоподстройкой частоты, и устройство восстановления символов QAM для вывода битовой последовательности, отражающей информацию правдоподобия, и декодер с исправлением ошибок для ввода информации правдоподобия и выполнения процесса исправления ошибок предоставляются на последующем этапе фазовой автоподстройки частоты, чтобы реализовать повышение устойчивости к ошибкам. PTL 1 описывает пример устройства восстановления символов QAM.

[0004]

Однако может быть невозможно получить достаточно улучшенную частоту появления ошибочных битов в зависимости от величины фазового шума, включенного в сигнал основной полосы для вывода из детектора, или вследствие ухудшения точности обнаружения фазы, возникающего в результате теплового шума или т. п. В связи с вышеизложенным известна методика для повышения точности компенсации фазовой ошибки путем адаптивного регулирования полосы пропускания контурного фильтра в фазовой автоподстройке частоты. PTL 2, PTL 3 и PTL 4 раскрывают вышеупомянутую методику. Однако устойчивость к ошибкам может все еще быть недостаточной.

[0005]

Кроме того, известен способ демодуляции, в котором для повышения точности компенсации фазовой ошибки используется сглаживающая фазовая автоподстройка частоты (S-PLL), которая является усовершенствованной фазовой автоподстройкой частоты. Например, NPL 1 и NPL 2 раскрывают принцип компенсации фазового шума путем усреднения, как описано выше.

[Список источников]

[Патентная литература]

[0006]

[PTL 1] Повторная публикация международной публикации PCT № W02011/068119

[PTL 2] Выложенная публикация патента Японии № 2000-101666

[PTL 3] Перевод на японский язык публикации международной заявки PCT № 2003-531523

[PTL 4] Выложенная публикация патента Японии № 2011-101177

[Непатентная литература]

[0007]

[NPL 1] J. Yang, B. Geller, C. Herzet, J. M. Brossier, "Smoothing PLLs for QAM Dynamical Phase Estimation", IEEE ICC 2009 Proceedings, 2009/6/14

[NPL 2] J. Yang, B. Geller, "Near Optimal Low Complexity Smoothing Loops for Dynamical Phase Estimation-Application to BPSK Modulated Signal", IEEE Transactions on Signal Processing, 2009/9/1

[Сущность изобретения]

[Техническая проблема]

[0008]

Однако в методике, описанной в вышеупомянутой литературе, ограничен эффект компенсации фазового шума путем фазовой автоподстройки частоты. В частности, когда уровень фазового шума, включенного в сигнал основной полосы для вывода из детектора, высок по сравнению с количеством уровней сигнала по способу QAM, невозможно получить достаточно улучшенную частоту появления ошибочных битов, и сложно выполнять передачу данных большого объема и высокого качества. Кроме того, та же проблема, что описана выше, применима к сглаживающей фазовой автоподстройке частоты. В частности, когда отношение сигнал-шум (SNR) большое, невозможно ожидать улучшение по сравнению с фазовой автоподстройкой частоты. Поэтому невозможно получить достаточную частоту появления ошибочных битов, и сложно выполнять передачу данных большого объема и высокого качества.

[0009]

Цель настоящего изобретения - предоставить методику для решения вышеупомянутых проблем.

[Решение проблемы]

[0010]

Для достижения описанной выше цели устройство компенсации фазовой ошибки содержит:

первый фильтр обнаружения фазовой ошибки, который формирует первое значение разности фаз и первое значение оценки фазовой ошибки на основе принятых символов в прямой последовательности;

второй фильтр обнаружения фазовой ошибки, который формирует второе значение разности фаз и второе значение оценки фазовой ошибки на основе принятых символов в обратной последовательности;

средство сложения фазовых ошибок, которое формирует третье значение оценки фазовой ошибки на основе первого значения оценки фазовой ошибки и второго значения оценки фазовой ошибки и одного из первого значения разности фаз и второго значения разности фаз; и

средство компенсации фазовой ошибки, которое компенсирует фазовую ошибку в принятых символах в соответствии с третьим значением оценки фазовой ошибки.

[0011]

Для достижения описанной выше цели устройство восстановления несущей содержит:

устройство компенсации фазовой ошибки по любому из п. п. 1-5;

средство восстановления символов, которое восстанавливает принятые символы, фазовая ошибка которых компенсируется устройством компенсации фазовой ошибки; и

средство декодирования с исправлением ошибок, которое исправляет ошибку, включенную в принятые символы, фазовая ошибка которых компенсируется на основе выходного сигнала средства восстановления символов, и выводит демодулированные данные.

[0012]

Для достижения описанной выше цели устройство демодуляции содержит:

устройство восстановления несущей;

опорный генератор, который выводит опорный сигнал фиксированной частоты;

детектор, который ортогонально детектирует входной сигнал промежуточной частоты и формирует сигнал основной полосы Ich и сигнал основной полосы Qch; и

аналого-цифровой преобразователь, который преобразует сформированный сигнал основной полосы в цифровой сигнал и вводит цифровой сигнал в устройство восстановления несущей в качестве принятых символов.

[0013]

Для достижения описанной выше цели устройство связи содержит:

по меньшей мере устройство демодуляции;

схему приема, которая выбирает радиоволну с предварительно определенной полосой частот из радиоволн, принимаемых антенной, чтобы преобразовать выбранную радиоволну в сигнал промежуточной частоты, и вводит преобразованный сигнал в устройство демодуляции; и

средство декодирования принятых данных, которое декодирует демодулированные данные, введенные устройством демодуляции, и формирует принятые данные.

[0014]

Для достижения описанной выше цели способ компенсации фазовой ошибки содержит:

формирование последовательности значений φ(1), φ(2), …, φ(M) разности фаз (где M - положительное целое число) между последовательностью принятых символов и последовательностью опорных символов;

последовательное вычисление первых значений θ+(1), θ+(2), …, θ+(M), θ+(M+1) оценки фазовой ошибки, обусловленных фазовым шумом, включенным в последовательность значений разности фаз, на основе последовательности значений разности фаз;

последовательное вычисление вторых значений θ-(M), θ-(M-1), …, θ-(1) оценки фазовой ошибки на основе последовательности значений φ(M), φ(M-1), …, φ(1) разности фаз путем установки θ+(M+1) в качестве начального значения;

вычисление третьих значений θ±(1), θ±(2), …, θ±(M) оценки фазовой ошибки путем линейного вычисления первых значений θ+(1), θ+(2), …, θ+(M) оценки фазовой ошибки, вторых значений θ-(1), θ-(2), …, θ-(M) оценки фазовой ошибки и значений φ(1), φ(2), …, φ(M) разности фаз;

последовательное вычисление первых значений оценки фазовой ошибки, вторых значений оценки фазовой ошибки и третьих значений оценки фазовой ошибки, включенных в значения φ(kM+1), φ(kM+2), …, φ((k+1)M) разности фаз касательно положительного целого k, с помощью процессов вычисления; и

компенсацию фазовой ошибки путем вычитания третьих значений θ±(kM+1), θ±(kM+2), …, θ±((k+1)M) оценки фазовой ошибки из значений φ(kM+1), φ(kM+2), …, φ((k+1)M) разности фаз.

[0015]

Для достижения описанной выше цели на запоминающий носитель сохраняется программа компенсации фазовой ошибки, которая предписывает компьютеру исполнять процессы:

формирования последовательности значений θ(1), θ(2), …, θ(M) разности фаз (где M - положительное целое число) между последовательностью принятых символов и последовательностью опорных символов;

последовательного вычисления первых значений θ+(1), θ+(2), …, θ+(M), θ+(M+1) оценки фазовой ошибки, обусловленных фазовым шумом, включенным в последовательность значений разности фаз, на основе последовательности значений разности фаз;

последовательного вычисления вторых значений θ-(M), θ-(M-1), …, θ-(1) оценки фазовой ошибки на основе последовательности значений φ(M), φ(M-1), …, φ(1) разности фаз путем установки θ+(M+1) в качестве начального значения;

вычисления третьих значений θ±(1), θ±(2), …, θ±(M) оценки фазовой ошибки путем линейного вычисления первых значений θ+(1), θ+(2), …, θ+(M) оценки фазовой ошибки, вторых значений θ-(1), θ-(2), …, θ-(M) оценки фазовой ошибки и значений φ(1), φ(2), …, φ(M) разности фаз;

последовательного вычисления первых значений оценки фазовой ошибки, вторых значений оценки фазовой ошибки и третьих значений оценки фазовой ошибки, включенных в значения φ(kM+1), φ(kM+2), …, φ((k+1)M) разности фаз касательно положительного целого k, с помощью процессов вычисления; и

компенсации фазовой ошибки путем вычитания третьих значений θ±(kM+1), θ±(kM+2), …, θ±((k+1)M) оценки фазовой ошибки из значений φ(kM+1), φ(kM+2), …, φ((k+1)M) разности фаз.

[Полезные результаты изобретения]

[0016]

В соответствии с настоящим изобретением можно выполнять передачу данных большого объема и высокого качества с улучшенной частотой появления ошибочных битов даже в неблагоприятном шумовом окружении, преимущественно обусловленном фазовым шумом или тепловым шумом.

[Краткое описание чертежей]

[0017]

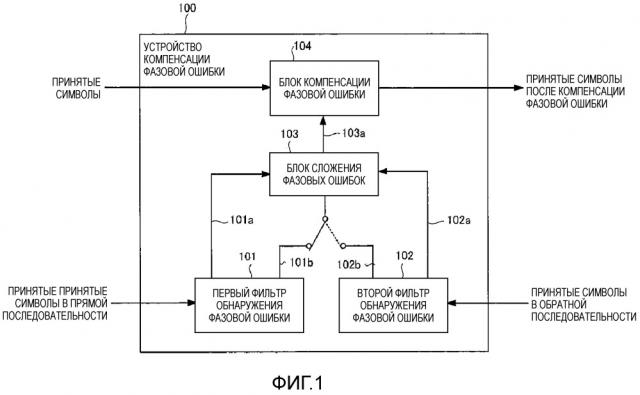

Фиг. 1 - блок-схема, иллюстрирующая конфигурацию устройства компенсации фазовой ошибки в первом примерном варианте осуществления настоящего изобретения.

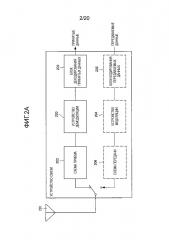

Фиг. 2A - блок-схема, иллюстрирующая конфигурацию устройства связи, включающего в себя устройство компенсации фазовой ошибки во втором примерном варианте осуществления настоящего изобретения.

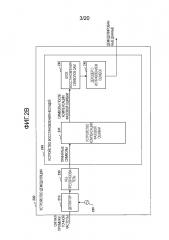

Фиг. 2B - блок-схема, иллюстрирующая конфигурацию устройства демодуляции, включающего в себя устройство компенсации фазовой ошибки во втором примерном варианте осуществления настоящего изобретения.

Фиг. 3 - блок-схема, иллюстрирующая конфигурацию устройства компенсации фазовой ошибки во втором примерном варианте осуществления настоящего изобретения.

Фиг. 4A - блок-схема, иллюстрирующая конфигурацию устройства компенсации фазовой ошибки в качестве базовой методики.

Фиг. 4B - блок-схема, иллюстрирующая конфигурацию устройства компенсации фазовой ошибки в качестве базовой методики.

Фиг. 5 - блок-схема, иллюстрирующая конфигурацию фильтра обнаружения фазовой ошибки во втором примерном варианте осуществления настоящего изобретения.

Фиг. 6 - блок-схема, иллюстрирующая конфигурацию блока сложения фазовых ошибок во втором примерном варианте осуществления настоящего изобретения.

Фиг. 7A - блок-схема, иллюстрирующая конфигурацию блока формирования параметров во втором примерном варианте осуществления настоящего изобретения.

Фиг. 7B - схема, иллюстрирующая конфигурацию таблицы для вычисления коэффициентов во втором примерном варианте осуществления настоящего изобретения.

Фиг. 8 - схема, иллюстрирующая пример спектра фазового шума у опорного генератора для формирования параметров во втором примерном варианте осуществления настоящего изобретения.

Фиг. 9 - блок-схема алгоритма, иллюстрирующая процедуру обработки в способе компенсации фазового шума во втором примерном варианте осуществления настоящего изобретения.

Фиг. 10 - графики, иллюстрирующие связь между среднеквадратической ошибкой и отношением несущей к шуму, относящуюся к фазовой ошибке, когда выполняется передача QPSK и когда выполняется передача 256QAM с использованием способа компенсации фазовой ошибки во втором примерном варианте осуществления настоящего изобретения по сравнению с традиционным способом.

Фиг. 11 - блок-схема, иллюстрирующая конфигурацию устройства компенсации фазовой ошибки в третьем примерном варианте осуществления настоящего изобретения.

Фиг. 12 - блок-схема, иллюстрирующая конфигурацию блока сложения фазовых ошибок в третьем примерном варианте осуществления настоящего изобретения.

Фиг. 13 - блок-схема, иллюстрирующая конфигурацию устройства демодуляции, включающего в себя устройство компенсации фазовой ошибки в четвертом примерном варианте осуществления настоящего изобретения.

Фиг. 14 - блок-схема, иллюстрирующая конфигурацию устройства компенсации фазовой ошибки в четвертом примерном варианте осуществления настоящего изобретения.

Фиг. 15 - блок-схема, иллюстрирующая конфигурацию фильтра обнаружения фазовой ошибки в четвертом примерном варианте осуществления настоящего изобретения.

Фиг. 16 - блок-схема, иллюстрирующая конфигурацию устройства компенсации фазовой ошибки в пятом примерном варианте осуществления настоящего изобретения.

Фиг. 17 - блок-схема, иллюстрирующая конфигурацию устройства демодуляции в шестом примерном варианте осуществления настоящего изобретения.

[Описание вариантов осуществления]

[0018]

Ниже подробно описываются примерные варианты осуществления настоящего изобретения со ссылкой на чертежи. Отметим, что описанные в нижеследующих примерных вариантах осуществления составляющие элементы являются всего лишь примерными элементами, и технический объем настоящего изобретения не ограничивается только этими элементами.

[0019]

[Первый примерный вариант осуществления]

Устройство 100 компенсации фазовой ошибки в качестве первого примерного варианта осуществления настоящего изобретения описывается с использованием фиг. 1. Устройство 100 компенсации фазовой ошибки является устройством для компенсации фазового шума, сформированного в опорном генераторе, или теплового шума.

[0020]

Как проиллюстрировано на фиг. 1, устройство 100 компенсации фазовой ошибки включает в себя первый фильтр 101 обнаружения фазовой ошибки, второй фильтр 102 обнаружения фазовой ошибки, блок 103 сложения фазовых ошибок и блок 104 компенсации фазовой ошибки. Первый фильтр 101 обнаружения фазовой ошибки формирует первое значение 101b разности фаз и первое значение 101a оценки фазовой ошибки на основе принятых символов в прямой последовательности. Второй фильтр 102 обнаружения фазовой ошибки формирует второе значение 102b разности фаз и второе значение 102a оценки фазовой ошибки на основе принятых символов в обратной последовательности. Третье значение 103a оценки фазовой ошибки формируется на основе первого значения 101a оценки фазовой ошибки и второго значения 102a оценки фазовой ошибки и одного из первого значения 101b разности фаз и второго значения 102b разности фаз. Блок 104 компенсации фазовой ошибки компенсирует фазовую ошибку в принятых символах в соответствии с третьим значением 103a оценки фазовой ошибки.

[0021]

В соответствии с примерным вариантом осуществления фазовая ошибка компенсируется путем объединения значения оценки фазовой ошибки и значения разности фаз, сформированных на основе принятых символов в прямой последовательности и в обратной последовательности. Поэтому вышеупомянутая конфигурация позволяет выполнять передачу данных большого объема и высокого качества с улучшенной частотой появления ошибочных битов даже в неблагоприятном шумовом окружении, преимущественно обусловленном фазовым шумом или тепловым шумом.

[0022]

[Второй примерный вариант осуществления]

Далее описывается устройство компенсации фазовой ошибки во втором примерном варианте осуществления настоящего изобретения. Устройство компенсации фазовой ошибки в примерном варианте осуществления компенсирует фазовую ошибку путем объединения значения оценки фазовой ошибки и значения разности фаз, сформированных на основе принятых символов в прямой последовательности и в обратной последовательности. Кроме того, в примерном варианте осуществления приводится описание касательно устройства восстановления несущей, включающего в себя устройство компенсации фазовой ошибки, устройства демодуляции, включающего в себя устройство восстановления несущей, и устройства связи, включающего в себя устройство демодуляции.

[0023]

В примерном варианте осуществления используется способ модуляции, использующий информацию о фазе для идентификации данных. В примерном варианте осуществления в качестве примера способа модуляции описывается способ QAM. Можно применять примерный вариант осуществления, поскольку способ модуляции является способом модуляции, использующим информацию о фазе для идентификации данных. Кроме того, в примерном варианте осуществления в качестве способа обнаружения для способа демодуляции используется способ квазисинхронного обнаружения, в котором обнаружение выполняется на основе периодического сигнала с фиксированной частотой, который должен формироваться самой схемой демодуляции, а фазовая ошибка вычитается после обнаружения. Этот способ обнаружения выгоден, потому что не нужно формировать сигнал, полностью синхронный с несущей. В примерном варианте осуществления предоставляется устройство компенсации фазовой ошибки для компенсации фазовой ошибки, обусловленной фазовым шумом, по способу квазисинхронного обнаружения. Отметим, что описание упрощается касательно всей конфигурации устройства демодуляции по способу квазисинхронного обнаружения. Ниже преимущественно описывается раздел, относящийся к оценке фазовой ошибки, которая является ключевой особенностью примерного варианта осуществления.

[0024]

В способе QAM в качестве способа модуляции и демодуляции, когда количество сигнальных точек равно 2m (где m - положительное целое число), битовая последовательность для передачи на стороне передачи разделяется по m битов, и каждый m-ый бит отображается в одну из 2m сигнальных точек. Отображенные сигнальные точки можно выразить в виде комплексных чисел, которые называются переданными символами. Сигнал основной полосы, обнаруженный на приемной стороне и впоследствии преобразованный в цифровой сигнал, является принятыми символами, ассоциированными с переданными символами. Каждый из сигнала основной полосы Ich и сигнала основной полосы Qch можно выразить в виде комплексных чисел, ассоциированных с действительной частью и мнимой частью. В дальнейшем вышеупомянутые комплексные числа называются принятыми символами. Принятые символы служат в качестве входного сигнала в устройство компенсации фазовой ошибки в примерном варианте осуществления.

[0025]

<<Конфигурация устройства связи>>

Фиг. 2A - блок-схема, иллюстрирующая конфигурацию устройства связи, включающего в себя устройство 241 компенсации фазовой ошибки в примерном варианте осуществления. Устройство связи в примерном варианте осуществления можно использовать для предоставления транзитной линии, обязательной для услуг мобильной телефонии, услуг цифровой фиксированной связи или т. п. В частности, устройство связи в примерном варианте осуществления можно использовать в качестве высококачественной цифровой линии связи с большой пропускной способностью для соединения между базовыми станциями для предоставления услуг мобильной телефонии. Отметим, что конфигурация устройства связи не ограничивается конфигурацией, проиллюстрированной на фиг. 2A.

[0026]

Устройство связи в примерном варианте осуществления в качестве принимающей системы включает в себя схему 202 приема, устройство 200 демодуляции и блок 203 декодирования принятых данных. Схема 202 приема выбирает радиоволну с предварительно определенной полосой частот из радиоволн, принятых антенной 201, для преобразования в сигнал промежуточной частоты и выводит сигнал в устройство 200 демодуляции в примерном варианте осуществления. Блок 203 декодирования принятых данных декодирует демодулированные данные для вывода устройством 200 демодуляции и формирует принятые данные. Кроме того, устройство связи в примерном варианте осуществления в качестве системы передачи может включать в себя блок 205 кодирования передаваемых данных, устройство 204 модуляции и схему 206 передачи. Блок 205 кодирования передаваемых данных кодирует передаваемые данные. Устройство 204 модуляции модулирует кодированные передаваемые данные в соответствии со способом демодуляции для устройства 200 демодуляции и формирует сигнал промежуточной частоты. Схема 206 передачи формирует радиоволну с предварительно определенной полосой частот для передачи на основе сигнала промежуточной частоты и передает радиоволну из антенны 201.

[0027]

<<Конфигурация и работа устройства демодуляции>>

Фиг. 2B - блок-схема, иллюстрирующая конфигурацию устройства 200 демодуляции, включающего в себя устройство 241 компенсации фазовой ошибки в примерном варианте осуществления.

[0028]

Устройство 200 демодуляции является устройством для демодуляции сигнала данных, который модулируется и передается по способу QAM. Устройство 200 демодуляции снабжается опорным генератором 220, детектором 210, аналого-цифровым преобразователем 230 (в дальнейшем называемым А/Ц-преобразователем) и устройством 240 восстановления несущей.

[0029]

Опорный генератор 220 вводит опорный сигнал фиксированной частоты в детектор 210. Детектор 210 ортогонально детектирует входной сигнал промежуточной частоты (IF) и формирует сигнал основной полосы с такой же фазовой компонентой (Ich) и сигнал основной полосы с ортогональной компонентой (Qch). Сформированные сигналы основной полосы преобразуются в цифровые сигналы А/Ц-преобразователем 230 и вводятся в устройство 240 восстановления несущей в качестве принятых символов.

[0030]

Устройство 240 восстановления несущей снабжается устройством 241 компенсации фазовой ошибки в примерном варианте осуществления, блоком 242 восстановления символов QAM и декодером 243 с исправлением ошибок. Блок 242 восстановления символов QAM принимает принятые символы, фазовая ошибка которых компенсируется устройством 241 компенсации фазовой ошибки, и формирует входные данные в декодер 243 с исправлением ошибок, который предоставляется на последующем этапе блока 242 восстановления символов QAM. Декодер 243 с исправлением ошибок выполняет процесс для исправления битовой ошибки, включенной в принятые символы, на основе данных, введенных из блока 242 восстановления символов QAM. Данные после процесса исправления ошибок служат в качестве демодулированных данных, которые являются выходным сигналом устройства 200 демодуляции. В этом случае, когда количество раз выполнения компенсации фазовой ошибки устройством 241 компенсации фазовой ошибки достигает предварительно определенного определенного количества раз, или когда декодер 243 с исправлением ошибок определяет, что нет ошибки, выходной сигнал декодера 243 с исправлением ошибок выводится в виде демодулированных данных из устройства 200 демодуляции. В противном случае устройство 241 компенсации фазовой ошибки повторно компенсирует фазовую ошибку в принятых символах для повышения точности компенсации.

[0031]

В вышеупомянутой конфигурации может быть так, что устройство 240 восстановления несущей временно сохраняет введенные принятые символы в буфере и компенсирует фазовую ошибку в принятых символах, хранимых в буфере, используя множество раз устройство 241 компенсации фазовой ошибки.

[0032]

<<Устройство компенсации фазовой ошибки>>

Далее описывается конфигурация устройства 241 компенсации фазовой ошибки в примерном варианте осуществления. Базовая методика, относящаяся к конфигурации устройства компенсации фазовой ошибки, описывается для прояснения признаков устройства 241 компенсации фазовой ошибки.

[0033]

<<Конфигурация устройства компенсации фазовой ошибки в качестве базовой методики>>

Фиг. 4A - блок-схема, иллюстрирующая конфигурацию устройства 241A компенсации фазовой ошибки в качестве базовой методики. Путем замены устройства 241 компенсации фазовой ошибки, проиллюстрированного на фиг. 2B, устройством 241A компенсации фазовой ошибки, проиллюстрированным на фиг. 4A, конфигурируется устройство демодуляции в качестве базовой методики.

[0034]

Устройство 241A компенсации фазовой ошибки, проиллюстрированное на фиг. 4A, снабжается фазовой автоподстройкой частоты (PLL), составленной умножителем 411 матрицы вращения, блоком 412 обнаружения фазы, контурным фильтром 413, блоком 414 суммирования с накоплением и блоком 415 преобразования данных, которые соединяются в контур.

[0035]

Умножитель 411 матрицы вращения вращает фазу принятых символов, ассоциированных с каждым из сигнала основной полосы Ich и сигнала основной полосы Qch, которые оцифрованы А/Ц-преобразователем 230, в соответствии с выходной информацией блока 415 преобразования данных, чтобы компенсировать фазовую ошибку. Выходной сигнал умножителя 411 матрицы вращения вводится в блок 412 обнаружения фазы.

[0036]

Блок 412 обнаружения фазы обнаруживает фазовую ошибку, оставшуюся в принятых символах, и вводит обнаруженную фазовую ошибку в контурный фильтр 413. Контурный фильтр 413 удаляет ненужную высокочастотную составляющую, включенную в фазовую ошибку, и вводит фазовую ошибку после удаления высокочастотной составляющей в блок 414 суммирования с накоплением. Блок 414 суммирования с накоплением формирует информацию о фазовой ошибке для назначения величины чередования фаз в умножителе 411 матрицы вращения на основе входного сигнала от контурного фильтра 413 и вводит сформированную информацию о фазовой ошибке в блок 415 преобразования данных. Блок 415 преобразования данных преобразует информацию о фазовой ошибке, введенную блоком 414 суммирования с накоплением, в данные синуса и данные косинуса, ассоциированные с введенной информацией о фазовой ошибке, и вводит преобразованные данные в умножитель 411 матрицы вращения.

[0037]

Как описано выше, можно реализовать устойчивое состояние с фазовой синхронизацией благодаря работе фазовой автоподстройки частоты, составленной умножителем 411 матрицы вращения, блоком 412 обнаружения фазы, контурным фильтром 413, блоком 414 суммирования с накоплением и блоком 415 преобразования данных, которые соединяются в контур, посредством этого компенсируя фазовую ошибку.

[0038]

Отметим, что принятые символы, фазовая ошибка которых компенсируется умножителем 411 матрицы вращения, также вводятся в блок 242 восстановления символов QAM в устройстве 240 восстановления несущей, а также в блок 412 обнаружения фазы.

[0039]

Как описано выше, устройство 241A компенсации фазовой ошибки, проиллюстрированное на фиг. 4A, выполняет компенсацию фазовой ошибки путем фазовой автоподстройки частоты и реализует повышение устойчивости к ошибкам с помощью процесса исправления ошибок, выполняемого на последующем этапе. Однако может быть сложно получить достаточно улучшенную частоту появления ошибочных битов в зависимости от величины фазового шума, включенного в сигнал основной полосы для вывода из детектора 210, или вследствие ухудшения точности блока 412 обнаружения фазы, обусловленного тепловым шумом или т. п.

[0040]

Фиг. 4B - блок-схема, иллюстрирующая конфигурацию устройства 241B компенсации фазовой ошибки в качестве базовой методики. Путем замены устройства 241 компенсации фазовой ошибки, проиллюстрированного на фиг. 2B, устройством 241B компенсации фазовой ошибки, проиллюстрированным на фиг. 4B, конфигурируется устройство демодуляции в качестве базовой методики. Устройство 241B компенсации фазовой ошибки, проиллюстрированное на фиг. 4B, применяет способ демодуляции, в котором сглаживающая фазовая автоподстройка частоты (S-PLL), являющаяся усовершенствованной фазовой автоподстройкой частоты, используется для повышения точности компенсации фазовой ошибки.

[0041]

Устройство 241B компенсации фазовой ошибки, применяющее сглаживающую фазовую автоподстройку частоты, составлено буфером 421, двумя фазовыми автоподстройками 422 и 423 частоты и блоком 424 усреднения. Буфер 421 временно сохраняет входные данные в устройство 241B компенсации фазовой ошибки и вводит один из двух типов последовательностей данных, то есть последовательность данных в порядке ввода и последовательность данных, чей порядок противоположен порядку ввода, в одну из фазовых автоподстроек 422 и 423 частоты и вводит другой из двух типов последовательностей данных в другую из фазовых автоподстроек 422 и 423 частоты. Каждая из фазовых автоподстроек 422 и 423 частоты обрабатывает входные данные и вводит результат обработки в блок 424 усреднения. Блок 424 усреднения вычисляет среднее двух данных, которые обрабатываются в разных порядках, и выводит результат вычисления.

[0042]

Однако вышеупомянутая сглаживающая фазовая автоподстройка частоты может содержать проблему в том, что точность компенсации фазовой ошибки для теплового шума становится практически равной точности, полученной с помощью обычной фазовой автоподстройки частоты, когда относящееся к тепловому шуму SNR большое, и не наблюдается улучшения, присущего повышенному объему вычисления.

[0043]

<<Конфигурация устройства компенсации фазовой ошибки в примерном варианте осуществления>>

Фиг. 3 - блок-схема, иллюстрирующая конфигурацию устройства 241 компенсации фазовой ошибки в примерном варианте осуществления. Устройство 241 компенсации фазовой ошибки в примерном варианте осуществления принимает принятые символы, оценивает фазовую ошибку, обусловленную фазовым шумом опорного генератора, и выводит принятые символы, фазовая ошибка которых компенсируется.

[0044]

Проиллюстрированное на фиг. 3 устройство 241 компенсации фазовой ошибки снабжается фильтром 301 обнаружения фазовой ошибки для принятых символов в прямой последовательности, фильтром 302 обнаружения фазовой ошибки для принятых символов в обратной последовательности, буферами 303 и 304 FILO и блоком 300 сложения фазовых ошибок. Кроме того, устройство 241 компенсации фазовой ошибки снабжается блоком 306 преобразования данных, умножителем 305 матрицы вращения, буфером 307 FILO и блоком 308 формирования параметров.

[0045]

Фильтр 301 обнаружения фазовой ошибки принимает принятые символы в прямой последовательности и выводит разность между фазой принятых символов в прямой последовательности и фазой оценочных переданных символов, сформированных внутри устройства 241 компенсации фазовой ошибки, и оценочное значение фазовой ошибки, сформированной в фазе принятых символов, обусловленной фазовым шумом. Фильтр 302 обнаружения фазовой ошибки принимает принятые символы в обратной последовательности и выводит разность между фазой принятых символов в обратной последовательности и фазой оценочных переданных символов, сформированных внутри устройства 241 компенсации фазовой ошибки, и оценочное значение фазовой ошибки, сформированной в фазе принятых символов, обусловленной фазовым шумом.

[0046]

Каждый из буферов 303 и 304 FILO является временным запоминающим устройством типа "первым пришел - последним обслужен", которое сохраняет принятые символы и выходную последовательность данных из фильтра 301 обнаружения фазовой ошибки предварительно определенное фиксированное количество раз и выводит принятые символы и выходную последовательность данных в порядке, обратном порядку ввода. Кроме того, буфер 307 FILO является временным запоминающим устройством типа "первым пришел - последним обслужен", которое преобразует принятые символы в обратной последовательности, фазовая ошибка которых компенсируется, в принятые символы в прямой последовательности. Отметим, что можно подключить запоминающее устройство предварительно определенной емкости вместо буфера 307 FILO, чтобы управлять адресами записи и адресами чтения.

[0047]

Блок 300 сложения фазовых ошибок выводит оценочное значение фазовой ошибки, сформированной в фазе принятых символов, обусловленной фазовым шумом, на основе входного сигнала от фильтров 301 и 302 обнаружения фазовой ошибки. Значение 304a оценки фазовой ошибки, чья последовательность обращена относительно значения 301a оценки фазовой ошибки из фильтра 301 обнаружения фазовой ошибки с помощью буфера 304 FILO, и значение 302a оценки фазовой ошибки и значение 302b разности фаз из фильтра 302 обнаружения фазовой ошибки вводятся в проиллюстрированное на фиг. 3 устройство 241 компенсации фазовой ошибки.

[0048]

Блок 306 преобразования данных принимает значение 300a оценки фазовой ошибки, которое является выходными данными из блока 300 сложения фазовых ошибок, и выводит данные фазовой компенсации, составленные значением синуса и значением косинуса входного значения. Умножитель 305 матрицы вращения принимает принятые символы и значение синуса и значение косинуса, которые являются выходным сигналом блока 306 преобразования данных, умножает матрицу вращения, в качестве компонентов включающую в себя значение синуса и значение косинуса, на принятые символы для вращения фазы и выводит результат умножения через буфер 307 FILO.

[0049]

Блок 308 формирования параметров формирует коэффициенты K1 - K5, которые используются в одном из процесса фильтров 301 и 302 обнаружения фазовой ошибки и процесса блока 300 сложения фазовых ошибок, на основе параметра фазового шума в опорном генераторе 220 и отношения сигнал-шум.

[0050]

(Работа устройства компенсации фазовой ошибки)

Далее описывается работа устройства 241 компенсации фазовой ошибки, проиллюстрированного на фиг. 3. Устройство 241 компенсации фазовой ошибки принимает принятые символы, компенсирует фазовую ошибку, включающую в себя фазу принятых символов, и выводит принятые символы после компенсации фазовой ошибки. Принятыми символами, введенными в устройство 241 компенсации фазовой ошибки, являются r(1), r(2), …, r(M) (где M - положительное целое число). Когда предполагается, что переданными символами, ассоциированными с принятыми символами, являются s(1), s(2), …, s(M), фазовым шумом, вызванным генератором, является θ(1), θ(2), …, θ(M), и шумом, обусловленным тепловым шумом, является w(1), w(2), …, w(M), принятые символы могут выражаться Уравнением (1).

[0051]

[Математическое выражение 1]

[0052]

Здесь e - постоянная Непера, а j - мнимая единица.

[0053]

Тепловой шум является белым шумом, чей спектр равномерен. Однако спектр фазового шума не равномерный. В качестве примера описывается случай, в котором спектр фазового шума имеет форму, которая проиллюстрирована на фиг. 8.

[0054]

Символы для опорной фазы, которые являются дополнительным входным сигналом в устройство 241 компенсации фазовой ошибки, проиллюстрированное на фиг. 3, указываются с помощью a(1), a(2), …, a(M). Когда переданные символы понятны заранее, предполагается, что символы для опорной фазы совпадают с переданными символами. Когда переданные символы не понятны, и когда можно использовать оценочные переданные символы после исправлени