Схема управления светодиодной подсветкой и жидкокристаллическое устройство отображения

Иллюстрации

Показать всеЗаявлены схема управления светодиодной подсветкой и жидкокристаллическое устройство отображения с перенастройкой управляющей частоты в соответствии с величиной рабочего тока. Технический результат заключается в сокращении энергопотребления и повышении управляемости схем управления такими устройствами. Схема включает буферный каскад для преобразования входного напряжения в выходное напряжение для линейки светодиодов; модуль контроля тока, соединенный с отрицательным выводом линейки светодиодов и регулирующий рабочий ток линейки светодиодов; чип драйвера, подающий на буферный каскад и модуль контроля тока соответственно первый и второй меандры; модуль детектирования тока, детектирующий рабочий ток линейки светодиодов для генерации детектирующего сигнала; модуль контрольного сигнала для приема детектирующего сигнала для генерации контрольного сигнала; и модуль регулировки частоты для приема контрольный сигнала с целью генерации сопротивления. Модуль регулировки частоты соединяется с чипом драйвера, и чип драйвера регулирует управляющую частоту схема управления в соответствии с сопротивлением. Также обеспечивается жидкокристаллическое устройство отображения, использующее такую схему управления. 2 н. и 18 з.п. ф-лы, 7 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

[0001] Настоящее изобретение относится к схеме управления светодиодной подсветкой, и в частности к схеме управления светодиодной подсветкой, которая может перестраивать управляющую частоту в соответствии с величиной рабочего тока, и жидкокристаллическому устройству отображения, в котором используется такая схема управления светодиодной подсветкой.

УРОВЕНЬ ТЕХНИКИ

[0002] С развитием технологий постоянно развиваются и технологии подсветки жидкокристаллических устройств отображения (ЖК-дисплеях). Источником подсветки в традиционных ЖК-дисплеях обычно является флюоресцентная лампа с холодным катодом (Cold Cathode Fluorescent Lamp, CCFL). Но поскольку CCFL-лампа в качестве источника подсветки обладает такими недостатками, как недостаточно качественное цветовоспроизведение, низкая светоотдача, высокое напряжение возникновения разряда, слабые характеристики разряда в низкотемпературной области и длительное время нагрева до стабильной люминесценции, в настоящее время предложена технология подсветки с использованием светодиодов в качестве источника.

[0003] На Фиг. 1 представлена принципиальная схема обычной управляющей схемы светодиодной подсветки устройства отображения на жидких кристаллах. Как показано на Фиг. 1, управляющая схема светодиодного источника подсветки включает буферный каскад, чип драйвера и линейку светодиодов. Буферный каскад включает индуктивность L, выпрямительный диод D1, первый полевой транзистор (FET) Q1, конденсатор С и первый резистор R1. На вывод индуктивности L подается постоянный ток (DC) напряжением Vin, другой вывод индуктивности L соединен с положительным выводом выпрямительного диода D1, а также со стоком первого FET Q1, затвор первого FET Q1 управляется первым меандром PWM1 подающимся от чипа драйвера, исток первого FET Q1 заземлен через первый резистор R1, отрицательный вывод выпрямительного диода D1 подает выходного напряжение Vout на линейку светодиодов, и отрицательный вывод выпрямительного диода D1 далее заземлен через конденсатор С. Отрицательный вывод линейки светодиодов соединен со вторым FET Q2. В частности, сток второго FET Q2 соединен с отрицательным выводом линейки светодиодов, исток второго FET Q2 заземлен через третий резистор R3, и затвор второго FET Q2 управляется вторым меандром PWM2 драйвером чипа. Меняя скважность второго меандра PWM2, можно увеличить или уменьшить рабочий ток линейки светодиодов. В управляющей схеме чип драйвера далее соединен со вторым резистором R2 для определения управляющей частоты Fs управляющей схемы.

[0004] В вышеописанной схеме управления управляющая частота фиксирована и вычисляется по формуле , где γ - внутренняя константа драйвера чипа. Выходная мощность Р управляющей схемы , где L это значение индуктивности L, Ip - пиковое значение тока, протекающего через индуктивность L. Когда рабочий ток линейки светодиодов уменьшается за счет снижения скважности второго меандра PWM2, выходная мощность управляющей схемы снижается, и соответственно может снизиться управляющая частота Fs. Однако, как описано выше, поскольку управляющая частота Fs управляющей схемы фиксирована, и энергопотребление каждого из индуктивности L, выпрямительного диода D1 и первого FET Q1 в буферном каскаде прямо пропорционально управляющей частоте Fs, в ситуации уменьшения скважности второго меандра PWM2 управляющая частота Fs должна соответственно снизиться, но она не снижается в действительности, что ухудшает управляемость схемы управления.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0005] С целью преодоления недостатков существующего уровня техники настоящим изобретением предусматривается схема управления светодиодной подсветкой, которая может перестраивать управляющую частоту в соответствии с величиной рабочего тока, и соответственно уменьшать энергопотребление и увеличивать управляемость схемы управления.

[0006] Для достижения вышеозначенной цели настоящее изобретение предлагает следующие решения.

[0007] В частности, схема управления светодиодной подсветкой включает: буферный каскад для преобразования входного напряжения в выходное напряжение для линейки светодиодов; модуль контроля тока, электрически соединенный с отрицательным выводом линейки светодиодов и для регулировки рабочего тока линейки светодиодов; чип драйвера для подачи на буферный каскад первого меандра, чтобы буферный каскад осуществлял соответствующую функцию, и подачи на модуль контроля тока второго меандра, для выполнения модулем контроля тока функции контроля тока; модуль детектирования тока для детектирования рабочего тока линейки светодиодов и генерации детектирующего сигнала в соответствии с детектированным рабочим током; модуль контрольного сигнала для получения детектирующего сигнала, сгенерированного модулем детектирования тока и генерирующего контрольный сигнал в соответствии с детектирующим сигналом; и модуль регулировки частоты для получения контрольного сигнала, генерированного модулем контрольного сигнала и генерации сопротивления в соответствии с контрольным сигналом. Модуль регулировки частоты кроме того электрически соединен с чипом драйвера, и чип драйвера регулирует управляющую частоту схемы управления светодиодной подсветкой в соответствии с сопротивлением.

[0008] В одном из вариантов осуществления настоящего изобретения, модуль детектирования тока включает оптопару. Вводы оптопары электрически соединены в контур с линейкой светодиодов, и вывод оптопары генерирует сигнал детектирования напряжения.

[0009] В одном из вариантов осуществления настоящего изобретения, оптопара включает светодиод и фотодиод. Положительный вывод светодиода электрически соединен с выводом буферного каскада, а отрицательный вывод светодиода электрически соединен с положительным выводом линейки светодиодов. Положительный вывод фотодиода электрически соединен с первым рабочим напряжением, и отрицательный вывод фотодиода электрически соединен с землей через четвертый резистор. Отрицательный вывод фотодиода генерирует сигнал детектирования напряжения.

[0010] В одном из вариантов осуществления настоящего изобретения, модуль контрольного сигнала включает первый компаратор и второй компаратор. Инвертирующий вход первого компаратора электрически соединен для приема первого опорного напряжения, неинвертирующий вход второй компаратор электрически соединен для приема второго опорного напряжения, неинвертирующий вход первого компаратора и инвертирующий вход второго компаратора электрически соединены для приема детектирующего сигнала, выходящего из модуля детектирования тока, и контрольные сигналы, генерированные выводами первого компаратора и второго компаратора раздельно вводятся в модуль регулировки частоты. Детектирующий сигнал является сигналом детектирования напряжения, и первое опорное напряжение превышает второе опорное напряжение.

[0011] В одном из вариантов осуществления настоящего изобретения, модуль регулировки частоты включает множество контуров, сформированных электрически соединенными резисторами и переключателями. Контрольный сигнал, генерированный модулем контрольного сигнала, переключает состояния «вкл/выкл» переключателей, чтобы таким образом избирательно включать различные контуры с различными сопротивлениями для электрической связи с чипом драйвера.

[0012] В одном из вариантов осуществления настоящего изобретения, переключателями являются полевые транзисторы или триоды.

[0013] В одном из вариантов осуществления настоящего изобретения, модуль регулировки частоты включает пятый резистор, первый вывод пятый резистор электрически соединен с чипом драйвера, и второй вывод пятого резистора заземлен через шестой резистор. Первый вывод пятого резистора далее электрически соединен с выводом седьмого резистора, другой вывод седьмого резистора электрически соединен со стоком третьего полевого транзистора, исток третьего полевого транзистора электрически соединен с землей, и затвор третьего полевого транзистора электрически соединен для приема контрольного сигнала, выводимого модулем контрольного сигнала. Второй вывод пятого резистора далее электрически соединен со стоком четвертого полевого транзистора, исток четвертого полевого транзистора электрически соединен с землей, и затвор четвертого полевого транзистора электрически соединен со вторым рабочим напряжением через восьмой резистор. Затвор четвертого полевого транзистора далее электрически соединен со стоком пятого полевого транзистора, исток пятого полевого транзистора электрически соединен с землей, и затвор пятого полевого транзистора электрически соединен для приема контрольного сигнала, выводимого модулем контрольного сигнала. Каждый из контрольных сигналов, выводимых модулем контрольного сигнала, является сигналом логического высокого уровня или логического низкого уровня, что вынуждает каждый из полевых транзисторов с третьего по пятый включать открываться или закрываться, и таким образом модуль регулировки частоты генерирует различные сопротивления для электрической связи с чипом драйвера.

[0014] В одном из вариантов осуществления настоящего изобретения, модуль детектирования тока включает оптопару. Оптопара включает светодиод и фотодиод. Положительный вывод светодиода электрически соединен с выводом буферного каскада, отрицательный вывод светодиода электрически соединен с положительным выводом линейки светодиодов, положительный вывод фотодиода электрически соединен с первым рабочее напряжением, отрицательный вывод фотодиода электрически соединен с землей через четвертый резистор, и отрицательный вывод фотодиода кроме того выполнен с возможностью генерации сигнала детектирования напряжения. Модуль контрольного сигнала включает первый компаратор и второй компаратор. Инвертирующий вход первого компаратора электрически соединен для приема первого опорного напряжения, неинвертирующий вход второго компаратора электрически соединен для приема второго опорного напряжения, неинвертирующий вход первого компаратора и инвертирующий вход второго компаратора электрически соединены для приема сигнала детектирования напряжения, выводимого модулем детектирования тока, контрольные сигналы, генерированные выводами первого компаратора и второго компаратора раздельно вводятся в модуль регулировки частоты. Первое опорное напряжение больше, чем второе опорное напряжение. Модуль регулировки частоты включает пятый резистор, первый вывод пятого резистора электрически соединен с чипом драйвера, и второй вывод пятого резистора электрически соединен с землей через шестой резистор. Первый вывод пятого резистора кроме того электрически соединен с выводом седьмого резистора, другой вывод седьмого резистора электрически соединен со стоком третьего полевого транзистора, исток третьего полевого транзистора электрически соединен с землей, и затвор третьего полевого транзистора электрически соединен с выводом первого компаратора. Второй вывод пятого резистора кроме того электрически соединен со стоком четвертого полевого транзистора, исток четвертого полевого транзистора электрически соединен с землей, и затвор четвертого полевого транзистора электрически соединен с вторым рабочим напряжением через восьмой резистор. Затвор четвертого полевого транзистора кроме того электрически соединен со стоком пятого полевого транзистора, исток пятого полевого транзистора электрически соединен с землей, и затвор пятого полевого транзистора электрически соединен с выводом второго компаратора.

[0015] В одном из вариантов осуществления настоящего изобретения, модуль контроля тока включает второй полевой транзистор и третий резистор. Сток второго полевого транзистора электрически соединен с отрицательным выводом линейки светодиодов, исток второго полевого транзистора электрически соединен с землей через третий резистор, затвор второго полевого транзистора электрически соединен с чипом драйвера и управляется вторым меандром, подающимся чипом драйвера, таким образом с изменением скважности второго меандра, рабочий ток линейки светодиодов возрастает или уменьшается.

[0016] В еще одном аспекте, жидкокристаллическое устройство отображения в соответствии с вариантом осуществления настоящего изобретения включает жидкокристаллическую панель (ЖК-панель) и модуль подсветки, расположенные напротив друг друга. Модуль подсветки обеспечивает источник света для дисплея ЖК-панели для отображения изображений. Модуль подсветки использует светодиодный источник подсветки. В светодиодном источнике подсветки задействована описанная выше схема управления светодиодной подсветкой.

[0017] Резюмируя схему управления подсветкой в соответствии с настоящим изобретением, посредством детектирования рабочего тока линейки светодиодов, в соответствии с изменением детектированного рабочего тока, модуль регулировки частоты избирательно включает контуры с различными сопротивлениями для электрической связи с чипом драйвера, таким образом могут быть получены различные управляющие частоты. То есть, когда скважность меандра для управления рабочим током линейки светодиодов уменьшается, выходная мощность схемы управления снижается, и соответственно снижается управляющая частота. В результате снижается мощность, потребляемая схемой управления, и возрастает ее управляемость.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0018] Вышеописанные варианты осуществления изобретения будут более понятны специалисту в области техники после рассмотрения последующего детального описания и сопровождающих чертежей.

[0019] На ФИГ. 1 представлена принципиальная схема обычной схемы управления светодиодным источником подсветки жидкокристаллического устройства отображения.

[0020] На ФИГ. 2 схематически представлена структура жидкокристаллического устройства отображения в соответствии с вариантом осуществления настоящего изобретения.

[0021] На ФИГ. 3 представлена схема связи модулей схема управления светодиодной подсветкой в соответствии с to вариантом осуществления настоящего изобретения.

[0022] На ФИГ. 4 показана принципиальная схема модуля детектирования тока в соответствии с to вариантом осуществления настоящего изобретения.

[0023] На ФИГ. 5 показана принципиальная схема модуля контрольного сигнала в соответствии с to вариантом осуществления настоящего изобретения.

[0024] На ФИГ. 6 представлена принципиальная схема модуля регулировки частоты в соответствии с to вариантом осуществления настоящего изобретения.

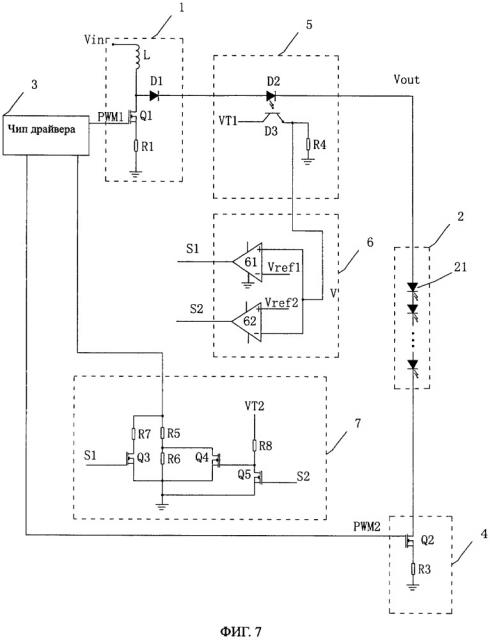

[0025] На ФИГ. 7 представлена принципиальная схема управления светодиодной подсветкой в соответствии с to вариантом осуществления настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

[0026] Далее настоящее изобретение будет раскрыто более подробно со ссылками на варианты его осуществления. Следует отметить, что последующее описание вариантов осуществления изобретения приведено исключительно в иллюстративных и описательных целях. Оно не предназначено быть исчерпывающим или быть ограниченным именно и только в соответствии с раскрытыми формами.

[0027] Со ссылкой на ФИГ. 2, предусмотрена ЖК-панель 200 и модуль подсветки 100 расположены напротив друг друга в соответствии с to вариантом осуществления настоящего изобретения. Модуль подсветки 100 обеспечивает источник света дисплея для ЖК-панели 200, таким образом ЖК-панель 200 воспроизводит изображение. В модуле подсветки 100 применяется светодиодный источник подсветки.

[0028] Со ссылкой на фигуры с 3 по 7 представлена схема управления светодиодного источника подсветки. На ФИГ. 3 показана схема соединения модулей схемы управления. Как показано на ФИГ. 3, схема управления включает: буферный каскад 1, чип драйвера 3, модуль контроля тока 4, модуль детектирования тока 5, модуль контрольного сигнала 6 и модуль регулировки частоты 7. Буферный каскад 1 выполнен с возможностью (то есть сконструирован и расположен) для преобразования входного напряжение Vin в желаемое выходное напряжение Vout и затем подачи выходного напряжения Vout на линейку светодиодов 2 в качестве напряжения питания. Модуль контроля тока 4 электрически соединен с отрицательным выводом линейки светодиодов 2 и для подстройки рабочего тока линейки светодиодов 2. Чип драйвера 3 выполнен с возможностью подачи на буферный каскад 1 первого меандра PWM1 для осуществления буферным каскадом 1 функцию преобразования напряжения, и кроме того выполнен с возможностью подачи на модуль контроля тока 4 второго меандра PWM2 для осуществления модулем контроля тока 4 функции контроля тока. Модуль детектирования тока 5 выполнен с возможностью детектирования рабочего тока линейки светодиодов 2 и генерирует детектирующий сигнал в соответствии с величиной рабочего тока. Модуль контрольного сигнала 6 принимает детектирующий сигнал, генерированный модулем детектирования тока 5, и генерирует контрольный сигнал в соответствии с детектирующим сигналом. Модуль регулировки частоты 7 получает контрольный сигнал, генерированный модулем контрольного сигнала 6, и генерирует сопротивление в соответствии с контрольным сигналом. Модуль регулировки частоты 7 кроме того электрически соединен с чипом драйвера 3. Чип драйвера 3 регулирует управляющую частоту схемы управления подсветкой в соответствии с сопротивлением, обеспечиваемым модулем регулировки частоты 7.

[0029] Со ссылкой на ФИГ. 7, буферный каскад 1 включает индуктивность L, выпрямительный диод D1, первый полевой транзистор (FET) Q1 и первый резистор R1. Вывод индуктивности L принимает постоянный ток DC напряжением Vin, а другой вывод индуктивности L электрически соединен с положительным выводом выпрямительного диода D1, как и сток первого FET Q1. Затвор первого FET Q1 управляется первым меандром PWM1, обеспечиваемым чипом драйвера 3, и исток первого FET Q1 заземлен через первый резистор R1. Отрицательный вывод выпрямительного диода D1 подает выходное напряжение Vout на линейку светодиодов 2.

[0030] Далее со ссылкой на ФИГ. 7, модуль контроля тока 4 включает второй FET Q2 и третий резистор R3. Сток второго FET Q2 электрически соединен с отрицательным выводом линейки светодиодов 2, исток второго FET Q2 заземлен через третий резистор R3, и затвор второго FET Q2 электрически соединен с чипом драйвера 3 и управляется вторым меандром PWM2, подаваемым чипом драйвера 3. Путем изменения скважности второго меандра PWM2, рабочий ток линейки светодиодов 2 может возрастать или уменьшаться.

[0031] В проиллюстрированном ФИГ. 7 примере показана только одна линейка светодиодов 2, которая включает множество светодиодов 21, электрически соединенных последовательно. В соответствии с настоящим изобретением, это могут быть и множество соединенных параллельно линеек светодоиодов 2, электрически соединенных с выводом буферного каскада 1, и отрицательные выводы соединенных параллельно линеек светодиодов соответственно электрически соединены с модулем контроля тока 4.

[0032] В проиллюстрированном варианте модуль детектирования тока 5 включает оптопару. Вводы оптопары электрически соединены в контур линейки светодиодов 2, и вывод оптопары генерирует сигнал детектирования напряжения. В частности, как показано на ФИГ. 4, оптопара включает светодиод D2 и фотодиод D3. Положительный вывод светодиода D2 электрически соединен с выводом Vout буферного каскада 1, и отрицательный вывод светодиода D2 электрически соединен с положительным выводом линейки светодиодов 2. Положительный вывод фотодиода D3 электрически соединен с первым рабочим напряжением VT1, для примера VT1=12V, и отрицательный вывод фотодиода D3 заземлен через четвертый резистор R4. Сигнал детектирования напряжения V генерируется на отрицательном выводе фотодиода D3. Более того, в оптопаре, если ток на вводах равен I1 (т.е. рабочий ток линейки светодиодов 2), и ток на выводе равен I2, они удовлетворяют уравнению I1=β*I2, где β - константа и определяется характеристикой преобразования оптопары. Когда рабочий ток линейки светодиодов 2 меняется, то есть, ток I1 на вводах меняется, ток I2 на выводе меняется соответствующим образом, и сигнал детектирования напряжения V, генерируемый на отрицательном выводе фотодиода D3, также соответственно меняется.

[0033] В проиллюстрированном примере, как показано на ФИГ. 5, модуль контрольного сигнала 6 включает первый компаратор 61 и второй компаратор 62. An Инвертирующий вход первого компаратора 61 принимает первое опорное напряжение Vref1, неинвертирующий вход второго компаратора 62 принимает второе опорное напряжение Vref2, неинвертирующий вход первого компаратора 61 и инвертирующий вход второго компаратора 62 принимают сигнал детектирования напряжения V, выводимый модулем детектирования тока 5. Контрольные сигналы S1, S2, соответственно генерируемые выводами первого компаратора 61 и второго компаратора 62, вводятся в модуль регулировки частоты 7. Первое опорное напряжение Vref1 больше, чем второе опорное напряжение Vref2.

[0034] Модуль регулировки частоты 7 может включать множество контуров, образованных множеством резисторов и множеством переключателей, электрически соединенных желаемым образом. Контрольные сигналы S1, S2 генерированные модулем контрольного сигнала 6, управляют состоянием «вкл/выкл» переключателей, чтобы избирательно включать различные контуры для связи с чипом драйвера 3. Здесь различные контуры обладают различными сопротивлениями. Переключатели - это полевые транзисторы или триоды. Для примера, как показано на ФИГ. 6, модуль регулировки частоты 7 включает пятый резистор R5, шестой резистор R6, седьмой резистор R7, восьмой резистор R8, третий FET Q3, четвертый FET Q4 и пятый FET Q5. Первый вывод пятого резистора R5 электрически соединен с чипом драйвера 3, второй вывод пятого резистора R5 заземлен через шестой резистор R6. Первый вывод пятого резистора R5 кроме того электрически соединен с выводом седьмого резистора R7, и другой вывод седьмого резистора R7 электрически соединен со стоком третьего FET Q3. Исток третьего FET Q3 электрически соединен с землей, и затвор третьего FET Q3 электрически соединен с выводом первого компаратора 61 для приема контрольного сигнала S1. Второй вывод пятого резистора R5 кроме того электрически соединен со стоком четвертого FET Q4, исток четвертого FET Q4 заземлен, и затвор четвертого FET Q4 электрически соединен со вторым рабочим напряжением VT2 через восьмой резистор R8, для примера VT2=5V. Затвор четвертого FET Q4 кроме того электрически соединен со стоком пятого FET Q5, исток пятого FET Q5 электрически соединен с землей, и затвор пятого FET Q5 электрически соединен с выводом второго компаратора 62 для приема контрольного сигнала S2.

[0035] Далее будет подробно описана работа схемы управления светодиодной подсветкой, проиллюстрированной на ФИГ. 7.

[0036] (а) Когда скважность второго меандра PWM2 максимальна, рабочий ток линейки светодиодов 2 максимален, сигнал детектирования напряжения V, выводимый модулем детектирования тока 5, имеет максимальное значение, в то же время V>Vref1>Vref2. Контрольные сигналы S1, S2, выводимые модулем контрольного сигнала 6, соответственно являются логически высоким уровнем и логически низким уровнем. В модуле регулировки частоты 7 третий FET Q3 и четвертый FET Q4 открыты, пока пятый FET Q5 закрыт, и в контурах модуля регулировки частоты 7 пятый резистор R5 и седьмой резистор R7 соединены параллельно с чипом драйвера 3. В это время управляющая частота: , что соответствует максимуму управляющей частоты.

[0037] (b) Когда скважность второго меандра PWM2 уменьшается, рабочий ток линейки светодиодов 2 соответственно уменьшается, и когда сигнал детектирования напряжения V, выводимый модулем детектирования тока 5, снижается до значения: Vref1>V>Vref2, контрольные сигналы S1, S2, выводимые модулем контрольного сигнала 6, оба являются логически низкими уровнями. В модуле регулировки частоты 7 четвертый FET Q4 открыт, а третий PET Q3 и пятый FET Q5 закрыты. В контурах модуля регулировки частоты 7 только пятый резистор R5 электрически связывается с чипом драйвера 3. В это время управляющая частота , что соответствует меньшей управляющей частоте.

[0038] (с) Когда скважность второго меандра PWM2 минимальна, рабочий ток линейки светодиодов 2 минимален, и сигнал детектирования напряжения V выводимый модулем детектирования тока 5, также минимален. В это время Vref1>Vref2>V. Контрольные сигналы S1, S2, выводимые модулем контрольного сигнала 6, соответственно являются логически низким уровнем и логически высоким уровнем. В модуле регулировки частоты 7 третий FET Q3 и четвертый FET Q4 закрыты, а пятый FET Q5 открыт.В контурах модуля регулировки частоты 7 пятый резистор R5 и шестой резистор R6 последовательно электрически соединены с чипом драйвера 3. В это время управляющая частота: , что соответствует минимуму управляющей частоты.

[0039] Резюмируя, для схема управления подсветкой в соответствии с настоящим изобретением, путем детектирования рабочего тока линейки светодиодов, в соответствии с изменением детектированного рабочего тока, модуль регулировки частоты избирательно включает контуры с различными сопротивлениями для связи с чипом драйвера, таким образом могут быть получены разные управляющие частоты. То есть, когда скважность меандра управления рабочим током линейки светодиодов уменьшается, выходная мощность схемы управления снижается, управляющая частота соответственна уменьшается. В результате энергопотребление схемы управления снижается, а управляемость возрастает.

[0040] Следует понимать, что в этом описании относительная терминология, такая как «первый» и «второй», предназначена только для отличения объекта или действия от другого объекта или действия, и не обязательно требуется или подразумевается, что эти объекты или действия действительно взаимосвязаны таким образом или в таком порядке. Кроме того, такая терминология как «включает», «содержит» и подобные вариации здесь подразумевают не исключающее включении, так что процесс, способ, предмет или аппарат, включающие последовательность составляющих, не только включают все перечисленное, но также включает и составляющие, которые не были явно перечислены, или составляющие, являющиеся неотъемлемыми компонентами процесса, способа, предмета или аппарата. В отсутствии более строгих условий составляющее, ограниченное фразеологией «включает один» не исключает существования дополнительного (-ых) идентичного(-ых) составляющего(-их) процесса, способа, предмета или аппарата, включающего указанную составляющую.

[0041] Хотя изобретение было описано в терминах вариантов осуществления, представляющихся в настоящее время наиболее практичными и предпочитаемыми, следует понимать, что изобретение не ограничивается раскрытыми примерами. Напротив, оно покрывает все различные модификации и аналогичные компоновки, включаемые в сущность и объем прилагаемой формулы изобретения, соответствующей наиболее широкой интерпретации для охвата всех таких модификаций и аналогичных структур.

1. Схема управления светодиодной подсветкой, включающая:

буферный каскад, выполненный с возможностью преобразования входного напряжения в выходное напряжение для линейки светодиодов;

модуль контроля тока, электрически соединенный с отрицательным выводом линейки светодиодов и выполненный с возможностью регулировать рабочий ток линейки светодиодов;

чип драйвера, выполненный с возможностью подачи на буферный каскад первого меандра, чтобы буферный каскад осуществлял преобразование напряжения, и далее подачи на модуль контроля тока второго меандра для осуществления модулем контроля тока функции контроля тока;

модуль детектирования тока, выполненный с возможностью детектирования рабочего тока линейки светодиодов и генерирования детектирующего сигнала в соответствии с детектированным рабочим током;

модуль контрольного сигнала, выполненный с возможностью приема детектирующего сигнала, генерированного модулем детектирования тока, и генерирования контрольного сигнала в соответствии детектирующим сигналом;

модуль регулировки частоты, выполненный с возможностью приема контрольного сигнала, генерированного модулем контрольного сигнала, и генерирования сопротивления в соответствии с контрольным сигналом и далее электрически соединенным с чипом драйвера, обеспечивая тем самым регулирование чипом драйвера управляющей частоты схемы управления светодиодной подсветкой в соответствии с генерированным сопротивлением.

2. Схема по п. 1, отличающаяся тем, что модуль детектирования тока включает оптопару, вводы оптопары электрически соединены в контур с линейкой светодиодов, и вывод оптопары выполнен с возможностью генерации сигнала детектирования напряжения.

3. Схема по п. 2, отличающаяся тем, что оптопара включает светоизлучающий диод и фотодиод; положительный вывод светодиода электрически соединен с выводом буферного каскада, и отрицательный вывод светодиода электрически соединен с положительным выводом линейки светодиодов; положительный вывод фотодиода электрически соединен с первым рабочим напряжением, и отрицательный вывод фотодиода заземлен через четвертый резистор; отрицательный вывод фотодиода выполнен с возможностью генерации сигнала детектирования напряжения.

4. Схема по п. 1, отличающаяся тем, что модуль контрольного сигнала включает первый компаратор и второй компаратор; инвертирующий вход первого компаратора электрически соединен с первым опорным напряжением, неинвертирующий вход второго компаратора электрически соединен со вторым опорным напряжением, неинвертирующий вход первого компаратора и инвертирующий вход второго компаратора электрически соединены с приемом детектирующего сигнала, выводимого модулем детектирования тока, контрольные сигналы, генерированные выводами первого и второго компаратора, введены в модуль регулировки частоты;

сигналом детектирования является сигнал детектирования напряжения, и первое опорное напряжение превышает второе опорное напряжение.

5. Схема по п. 1, отличающаяся тем, что модуль регулировки частоты включает множество контуров, сформированных электрически соединенными множеством резисторов и множеством переключателей; контрольный сигнал, генерированный модулем контрольного сигнала, управляет переключением состояний «вкл/выкл» множества переключателей, тем самым избирательно включая различные контуры с различными сопротивлениями для электрической связи с чипом драйвера.

6. Схема по п. 5, отличающаяся тем, что множеством переключателей являются полевые транзисторы или триоды.

7. Схема по п. 5, отличающаяся тем, что модуль регулировки частоты включает пятый резистор, первый вывод пятого резистора электрически соединен с чипом драйвера, и второй вывод пятого резистора заземлен через шестой резистор; и первый вывод пятого резистора электрически соединен с выводом седьмого резистора, другой вывод седьмого резистора электрически соединен со стоком третьего полевого транзистора, исток третьего полевого транзистора заземлен, и затвор третьего полевого транзистора электрически соединен с выводом первого компаратора; второй вывод пятого резистора, кроме того, электрически соединен со стоком четвертого полевого транзистора, исток четвертого полевого транзистора электрически соединен с землей, и затвор четвертого полевого транзистора электрически соединен со вторым рабочим напряжением через восьмой резистор; затвор четвертого полевого транзистора, кроме того, электрически соединен со стоком пятого полевого транзистора, исток пятого полевого транзистора заземлен, и затвор пятого полевого транзистора электрически соединен с другим контрольным сигналом, выводимым модулем контрольного сигнала;

каждый из контрольных сигналов, выводимых модулем контрольного сигнала, является логически высоким уровнем или логически низким уровнем, обеспечивая каждому из транзисторов с третьего по пятый открываться или закрываться, с обеспечением модулю регулировки частоты возможности генерировать различные сопротивления для электрической связи с чипом драйвера.

8. Схема по п. 1, отличающаяся тем, что модуль детектирования тока включает оптопару, оптопара включает светодиод и фотодиод, положительный вывод светодиода электрически соединен с выводом буферного каскада, отрицательный вывод светодиода электрически соединен с положительным выводом линейки светодиодов, положительный вывод фотодиода электрически соединен с первым рабочим напряжением, отрицательный вывод фотодиода заземлен через четвертый резистор, и отрицательный вывод фотодиода выполнен с возможностью генерации сигнала детектирования напряжения;

модуль контрольного сигнала включает первый компаратор и второй компаратор, инвертирующий вход первого компаратора электрически соединен для приема первого опорного напряжения, неинвертирующий вход второго компаратора электрически соединен для приема второго опорного напряжения, неинвертирующий вход первого компаратора и инвертирующий вход второго компаратора электрически соединены для приема сигнала детектирования напряжения, выводимого модулем детектирования тока, контрольные сигналы, генерированные выводам первого компаратора и второго компаратора, раздельно введены в модуль регулировки частоты, первое опорное напряжение превышает второе опорное напряжение;

модуль регулировки частоты включает пятый резистор, первый вывод пятого резистора электрически соединен с чипом драйвера, и второй вывод пятого резистора заземлен через шестой резистор; и первый вывод пятого резистора электрически соединен с выводом седьмого резистора, другой вывод седьмого резистора электрически соединен со стоком третьего полевого транзистора, исток третьего полевого транзистора заземлен, и затвор третьего полевого транзистора электрически соединен с выводом первого компаратора; второй вывод пятого резистора, кроме того, электрически соединен со стоком четвертого полевого транзистора, исток четвертого полевого транзистора электрически соединен с землей, и затвор четвертого полевого транзистора электрически соединен со вторым рабочим напряжением через восьмой резистор; затвор четвертого полевого транзистора, кроме того, электрически соединен со стоком пятого полевого транзистора, исток пятого полевого транзистора заземлен, и затвор пятого полевого транзистора электрически соединен с выводом второго компаратора.

9. Схема по п. 1, отличающаяся тем, что модуль контроля тока включает второй полевой транзистор и третий резистор; сток второго полевого транзистора электрически соединен с отрицательным выводом линейки светодиодов, исток второго полевого транзистора электрически заземлен через третий резистор, затвор второго полевого транзистора электрически соединен с чипом драйвера и управляется вторым меандром, подаваемым чипом драйвера, таким образом, с изменением скважности второго меандра рабочий ток линейки светодиодов возрастает или уменьшается.

10. Схема по п. 8, отличающаяся тем, что модуль контроля тока включает второй полевой транзистор и третий резистор; сток второго полевого транзистора электрически соединен с отрицательным выводом линейки светодиодов, исток второго полевого транзистора заземлен через третий резистор, затвор второго полевого транзистора электрически соединен с чипом драйвера и управляется вторым меандром, подаваемым чипом драйвера, таким образом, с изменением скважности второго меандра рабочий ток линейки светодиодов возрастает или уменьшается.

11. Жидкокристаллическое устройство отображения, включающее жидкокристаллическую панель и модуль подсветки, расположенные друг напротив друга, модуль подсветки выполнен с обеспечением источника света дисплея жидкокристаллической панели для осуществления жидкокристаллической панелью отображения изображения, модуль подсветки выполнен с возможностью использования светодиодного источник подсветки, схема управления светодиодным источником подсветки вклю