Управляемый мажоритарный элемент "три из пяти"

Иллюстрации

Показать всеИзобретение относится к автоматике и вычислительной технике и может быть использовано при разработке высоконадежных устройств и систем, применяющих мажоритарное резервирование. Технический результат заключается в расширении арсенала средств. В управляемый мажоритарный элемент «три из пяти», содержащий пятивходовый мажоритарный элемент (МЭ), состоящий из двухвходовых элементов И и ИЛИ, и схему контроля МЭ, состоящую из одного пятивходового элемента НЕ-И, одного трехвходового элемента И и одного двухвходового элемента ИЛИ, дополнительно введена схема блокировки. Схема блокировки состоит из дешифратора, пяти четырехвходовых элементов И и пяти двухвходовых элементов И, причем входы четырехвходовых элементов И соединены с выходами дешифратора, каждые два входа двухвходовых элементов И схемы блокировки соединены с одним из входных информационных сигналов и одним из выходов четырехвходовых элементов И, а выходы двухвходовых элементов И схемы блокировки соединены с МЭ. 1 ил., 2 табл.

Реферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке высоконадежных устройств и систем, применяющих мажоритарное резервирование, например, для достоверной передачи данных в исполнительные устройства автоматики по нескольким каналам связи.

Известен мажоритарный элемент «три из пяти», содержащий десять трехвходовых элементов И и элемент ИЛИ, причем входы устройства подключены к входам элементов И, выходы которых соединены с входами элемента ИЛИ, выход которого является выходом устройства (Доманицкий С.М. Построение надежных логических устройств. - М.: Энергия, 1971, с. 74, рис. 3-3а).

Недостатками этого мажоритарного элемента является сложность устройства, выражающаяся в большом числе связей, а также недостаточные функциональные возможности, так как он не позволяет определить в случае неисправности все ли сигналы на входе мажоритарного элемента являются исправными и отсутствует схема определения неисправного канала.

В качестве наиболее близкого аналога может быть принят пятивходовый мажоритарный элемент «три из пяти» (полезная модель №81018 от 06.10.2008 г.), содержащий двенадцать элементов И, шесть элементов ИЛИ. При поступлении на вход 1,2,…,5 логических сигналов с помощью элементов ИЛИ и элементов И выполняется операция мажорирования. С помощью элементов И, инверторов НЕ, элементов И фиксируется неисправность резервируемых объектов, выходные сигналы которых обрабатываются данным мажоритарным элементом [1].

При поступлении на три, четыре и на пять входов мажоритарного элемента сигналов «1» на его рабочем выходе появляется сигнал «1», то есть он выполняет функцию мажорирования «три из пяти». На контрольном выходе мажоритарного элемента сигнал «1» появится только в том случае, если выходные сигналы всех пяти входов совпадают, что свидетельствует об исправности всех входных сигналов.

Недостаток данного устройства заключается в том, что возникновение отказа в канале приводит к возникновению сигнала контроля, информирующего о наличии неисправности входного/входных сигналов, но схема контроля не позволяет вычислить какой из каналов является неисправным.

Основной задачей предлагаемого изобретения является повышение функционала схемы контроля, а именно определение неисправного канала с помощью дополнительных управляющих воздействий и организация возможности введения «имитации» неисправности для отладки реакции схемы при разработке.

Сущность изобретения заключается в том, что в пятивходовый мажоритарный элемент (МЭ), состоящий из двухвходовых элементов И и ИЛИ, причем выход первого двухвходового элемента И соединен с входом пятого двухвходового элемента И, выход первого двухвходового элемента ИЛИ соединен с входом шестого двухвходового элемента И, выход второго двухвходового элемента ИЛИ соединен с входом пятого двухвходового элемента И, выходы второго двухвходового элемента И соединены с четвертыми двухвходовыми элементами ИЛИ и И, выход третьего двухвходового элемента ИЛИ соединен с входами вторых двухвходовых элементов ИЛИ и И, выход третьего двухвходового элемента И соединен с входами четвертых двухвходовых элементов ИЛИ и И, выход четвертого двухвходового элемента ИЛИ соединен с входом шестого двухвходового элемента И, выходы четвертого, пятого и шестого двухвходовых элементов И соединены с трехвходовым элементом ИЛИ, дополнительно введена схема блокировки, состоящая из дешифратора, пяти четырехвходовых элементов И и пяти двухвходовых элементов И, причем каждые два входа двухвходовых элементов И схемы блокировки соединены с одним из входных информационных сигналов и одним из выходов четырехвходовых элементов И, а выходы двухвходовых элементов И схемы блокировки соединены с МЭ таким образом, что первый и второй двухвходовые элементы И схемы блокировки соединены с первыми двухвходовыми элементами ИЛИ и И МЭ, третий двухвходовый элемент И схемы блокировки соединен с входами вторых двухвходовых элементов ИЛИ и И МЭ, а четвертый и пятый двухвходовые элементы И схемы блокировки соединены с третьими двухвходовыми элементами ИЛИ и И МЭ, входы четырехвходовых элементов И соединены с выходами дешифратора так, что первый четырехвходовый элемент И соединен с седьмым, восьмым, девятым и десятым выходами дешифратора, второй четырехвходовый элемент И соединен с четвертым, пятым, шестым и десятым выходами дешифратора, третий четырехвходовый элемент И соединен со вторым, третьим, четвертым и восьмым выходами дешифратора, четвертый четырехвходовый элемент И соединен с первым, третьим, шестым и девятым выходами дешифратора, пятый четырехвходовый элемент И соединен с первым, вторым, пятым и седьмым выходами дешифратора. Изобретение включает в себя схему контроля МЭ, состоящую из одного пятивходового элемента НЕ-И, входы которого соединены с выходами каждого из пяти двухвходовых элементов И схемы блокировки, одного трехвходового элемента И, входы которого соединены с выходом третьего двухвходового элемента И схемы блокировки и выходами первого двухвходового элемента И и второго двухвходового элемента И МЭ, и одного двухвходового элемента ИЛИ, входы которого соединены с выходами пятивходового элемента НЕ-И и трехвходового элемента И.

На фигуре приведена схема предлагаемого устройства, где:

1 - четырехвходовый DC дешифратор;

2-6 - первый, второй, третий, четвертый и пятый четырехвходовые элементы И схемы блокировки;

7-11 - первый, второй, третий, четвертый и пятый двухвходовые элементы И схемы блокировки;

12, 14, 18, 21 - первый, второй, третий, четвертый двухвходовые элементы ИЛИ МЭ;

13, 15, 19, 22, 23, 24 - первый, второй, третий, четвертый, пятый и шестой двухвходовые элементы И МЭ;

16 - пятивходовый элемент НЕ-И схемы контроля;

17 - трехвходовый элемент И схемы контроля;

20 - двухвходовый элемент ИЛИ схемы контроля;

25 - трехвходовый элемент ИЛИ МЭ;

ВХ1, ВХ2, ВХ3, ВХ4, ВХ5 - входы МЭ;

ВЫХ1 - выход мажоритарного элемента;

К1 - контрольный выход;

БЛ1, БЛ2, БЛ3, БЛ4 - входы схемы блокировки.

Устройство содержит: схему блокировки, состоящую из четырехвходового дешифратора DC1, пяти четырехвходовых элементов И (И1…И6) и пяти двухвходовых элементов И (И7…И11); пятивходовый МЭ, который состоит из четырех двухвходовых элементов ИЛИ (ИЛИ12, ИЛИ14, ИЛИ18, ИЛИ21), шести двухвходовых элементов И (И13, И15, И19, И22, И23, И24) и трехвходового элемента ИЛИ25; схему контроля, которая состоит из одного пятивходового элемента НЕ-И16, одного трехвходового элемента И17 и одного двухвходового элемента ИЛИ20.

Первый вход ВХ1 соединен с входом первого двухвходового элемента И7 схемы блокировки, второй вход которого соединен с выходом первого четырехвходового элемента И2, второй вход ВХ2 соединен с входом второго двухвходового элемента И8 схемы блокировки, второй вход которого соединен с выходом второго четырехвходового элемента И3, третий вход ВХ3 соединен с входом третьего двухвходового элемента И9 схемы блокировки, второй вход которого соединен с выходом третьего четырехвходового элемента И4, четвертый вход ВХ4 соединен с входом четвертого двухвходового элемента И10 схемы блокировки, второй вход которого соединен с выходом четвертого четырехвходового элемента И5, пятый вход ВХ5 соединен с входом пятого двухвходового элемента И11 схемы блокировки, второй вход которого соединен с выходом пятого четырехвходового элемента И6.

Первый выход элемента DC1 соединен с входом четвертого и пятого четырехвходовых элементов И5 и И6, второй выход элемента DC1 соединен с входом третьего и пятого четырехвходовых элементов И4 и И6, третий выход элемента DC1 соединен с входом третьего и четвертого четырехвходовых элементов И4 и И5, четвертый выход элемента DC1 соединен с входом второго и третьего четырехвходовых элементов И3 и И4, пятый выход элемента DC1 соединен с входом второго и пятого четырехвходовых элементов И3 и И6, шестой выход элемента DC1 соединен с входом второго и четвертого четырехвходовых элементов И3 и И5, седьмой выход элемента DC1 соединен с входом первого и пятого четырехвходовых элементов И2 и И6, восьмой выход элемента DC1 соединен с входом первого и третьего четырехвходовых элементов И2 и И4, девятый выход элемента DC1 соединен с входом первого и четвертого четырехвходовых элементов И2 и И5, десятый выход элемента DC1 соединен с входом первого и второго четырехвходовых элементов И2 и И3.

Выходы первого и второго двухвходовых элементов И7, И8 схемы блокировки соединены с входами первых двухвходовых элементов ИЛИ 12, И13 МЭ и входом пятивходового элемента НЕ-И16. Выходы третьего двухвходового элемента И9 схемы блокировки соединены с входом пятивходового элемента НЕ-И16, входом трехвходового элемена И17 и входами вторых двухвходовых элементов ИЛИ18 и И19 МЭ. Выходы четвертого и пятого двухвходовых элементов И10 и И11 схемы блокировки соединены с входами третьих двухвходовых элементов ИЛИ 14, И15 МЭ и входом пятивходового элемента НЕ-И16. Выход первого двухвходового элемента ИЛИ12 МЭ соединен с входом шестого двухвходового элемента И24 МЭ. Выходы первого двухвходового элемента И13 МЭ соединены с входами трехвходового элемента И17 и пятого двухвходового элемента И23 МЭ. Выходы третьего двухвходового элемента ИЛИИ МЭ соединены с входом второго двухвходового элемента ИЛИ18 и входом второго двухвходового элемента И19 МЭ. Выходы второго двухвходового элемента И15 МЭ соединены с входом трехвходового элемента И17 и входами четвертых двухвходовых элементов ИЛИ21 и И22 МЭ. Выход второго двухвходового элемента ИЛИ18 МЭ соединен с входом пятого двухвходового элемента И23 МЭ. Выходы второго двухвходового элемента И19 МЭ соединены с входами четвертых двухвходовых элементов ИЛИ21 и И22 МЭ. Выход четвертого двухвходового элемента ИЛИ21 МЭ соединен с входом шестого двухвходового элемента И24 МЭ. Выходы четвертого, пятого и шестого двухвходовых элементов И22, И23 и И24 МЭ соединены с входами трехвходового элемента ИЛИ25. Выходы пятивходового элемента НЕ-И16 и трехвходового элемента И17 соединены с входами двухвходового элемента ИЛИ20.

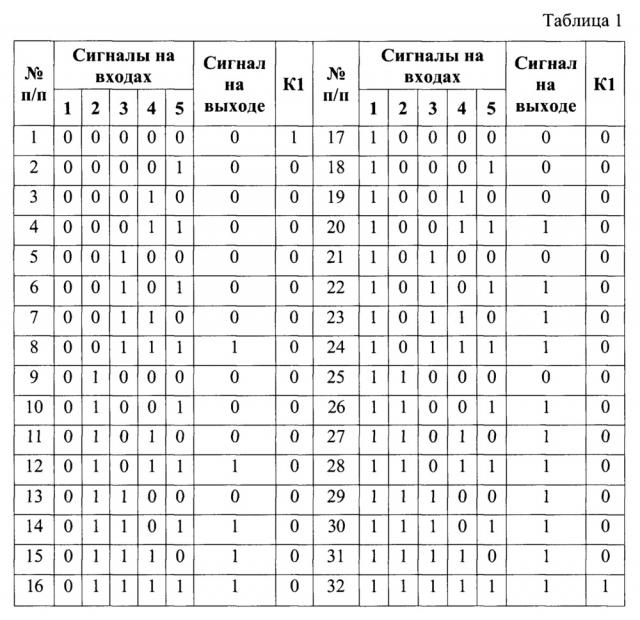

Мажоритарный элемент работает следующим образом. Работа мажоритарного элемента «три из пяти» с контролем и блокировкой иллюстрируется таблицей 1, в которой показаны состояния его выхода в зависимости от сигналов «0» или «1» на его входах.

При поступлении на входы 1-5 логических сигналов от резервируемых объектов, с помощью элементов ИЛИ12, ИЛИ14, ИЛИ18, ИЛИ21, ИЛИ25 и элементов И13, И15, И19, И22, И23, И24 выполняется операция мажорирования «три из пяти» - при совпадении сигналов как на трех входах мажоритарного элемента, «четыре из пяти» - при совпадении сигналов на четырех входах, и «пять из пяти» - при совпадении сигналов на всех его входах. С помощью элементов НЕ-И16, И17 и ИЛИ20 фиксируется неисправность резервируемых объектов, если хотя бы на одном из пяти входов мажоритарного элемента существует сигнал логического «0» или «1», отличный от других входных сигналов.

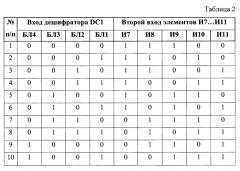

С помощью дешифратора DC1 и элементов И2, И3, И4, И5, И6 выявляется неисправный канал.

Работа схемы блокировки иллюстрируется таблицей 2, в которой показаны состояния его входов БЛ1, БЛ2, БЛ3, БЛ4 в зависимости от необходимости определения неисправного канала. Путем перебора комбинаций входных сигналов DC1 согласно таблице 2 выявляется конкретный неисправный канал мажоритарного элемента и их количество.

Рассмотрим работу мажоритарного элемента «три из пяти» с контролем неисправности при поступлении на входы 1-5, например, комбинации 01010 с двумя неисправными входами 2 и 4. В этом случае на выходах элементов ИЛИ 12, ИЛИ 14, ИЛИ 18, будут присутствовать сигналы «1», на выходах элементов И13, И15, И19, ИЛИ21 - сигнал «0», следовательно, на выходах элементов И22, И23, И24 и на рабочем выходе ИЛИ25 устройства будет сформирован сигнал «0». На контрольном выходе К1 будет сформирован сигнал «0», что будет свидетельствовать о наличии неисправности. При подаче комбинации сигналов 0101 на вход DC1 на второй и четвертый вход мажоритарного элемента принудительно будут введены сигналы «0», которые приведут к появлению на выходе мажоритарного элемента ВЫХ1 сигнала «0» и на выходе К1 сигнала «1», что будет свидетельствовать о неисправности второго и четвертого канала на входе мажоритарного элемента.

Таким образом, благодаря новой схеме мажоритарного элемента «три из пяти» существенно повысилась функциональность мажоритарного элемента, позволяющая определить неисправные каналы.

Управляемый мажоритарный элемент «три из пяти» может включать не один, а несколько мажоритарных элементов с объединенной схемой блокировки входных сигналов.

Технический результат - увеличение функциональных возможностей мажоритарного элемента «три из пяти» достигается путем контроля совпадения входных сигналов, введением схемы блокировки для определения неисправного канала, компактностью схемы за счет объединения схемы блокировки для двух и более мажоритарных элементов и отсутствием избыточности логических элементов путем применения их оптимизированных аналогов.

Источники информации

1. Доманицкий С.М. Построение надежных логических устройств. - М.: Энергия, 1971, с. 74, рис. 3-3а.

2. Патент на полезную модель RU 81018 от 06.10.2008 г. «Мажоритарный элемент «три из пяти».

Управляемый мажоритарный элемент «три из пяти»

Управляемый мажоритарный элемент «три из пяти», содержащий пятивходовый мажоритарный элемент (МЭ), состоящий из двухвходовых элементов И и ИЛИ, причем выход первого двухвходового элемента И соединен с входом пятого двухвходового элемента И, выход первого двухвходового элемента ИЛИ соединен с входом шестого двухвходового элемента И, выходы второго двухвходового элемента И соединены с входами четвертых двухвходовых элементов ИЛИ и И, выход второго двухвходового элемента ИЛИ соединен с входом пятого двухвходового элемента И, выходы третьего двухвходового элемента ИЛИ соединены с входами вторых двухвходовых элементов ИЛИ и И, выходы третьего двухвходового элемента И соединены с входами четвертых двухвходовых элементов ИЛИ и И, выход четвертого двухвходового элемента ИЛИ соединен с шестым двухвходовым элементом И, выходы четвертого, пятого и шестого двухвходовых элементов И соединены с трехвходовым элементом ИЛИ, и схему контроля МЭ, отличающийся тем, что дополнительно введена схема блокировки, состоящая из дешифратора, пяти четырехвходовых элементов И и пяти двухвходовых элементов И, причем каждые два входа двухвходовых элементов И схемы блокировки соединены с одним из входных информационных сигналов и одним из выходов четырехвходовых элементов И, а выходы двухвходовых элементов И схемы блокировки соединены с МЭ таким образом, что выходы первого и второго двухвходовых элементов И схемы блокировки соединены с входами первых двухвходовых элементов ИЛИ и И МЭ, выходы третьего двухвходового элемента И схемы блокировки соединены с входами вторых двухвходовых элементов ИЛИ и И МЭ, а выходы четвертого и пятого двухвходовых элементов И схемы блокировки соединены с входами третьих двухвходовых элементов ИЛИ и И МЭ, входы четырехвходовых элементов И соединены с выходами дешифратора так, что первый четырехвходовый элемент И соединен с седьмым, восьмым, девятым и десятым выходами дешифратора, второй четырехвходовый элемент И соединен с четвертым, пятым, шестым и десятым выходами дешифратора, третий четырехвходовый элемент И соединен со вторым, третьим, четвертым и восьмым выходами дешифратора, четвертый четырехвходовый элемент И соединен с первым, третьим, шестым и девятым выходами дешифратора, пятый четырехвходовый элемент И соединен с первым, вторым, пятым и седьмым выходами дешифратора, схема контроля МЭ состоит из одного пятивходового элемента НЕ-И, входы которого соединены с выходами каждого из двухвходовых элементов И схемы блокировки, одного трехвходового элемента И, входы которого соединены с выходом третьего двухвходового элемента И схемы блокировки, выходами первого и второго двухвходовых элементов И МЭ, и одного двухвходового элемента ИЛИ, входы которого соединены с выходами пятивходового элемента НЕ-И и трехвходового элемента И.