Устройство обработки данных и способ обработки данных

Иллюстрации

Показать всеГруппа изобретений относится к области обработки данных и может быть использована для кодирования/декодирования с использованием LDPC-кода. Техническим результатом является повышение устойчивости LDPC-кода к возникновению ошибок. LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую битам информации, и часть матрицы четности, соответствующую битам четности. Часть информационной матрицы представлена таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую позиции элементов 1 части информационной матрицы каждые 360 столбцов. 12 н. и 60 з.п. ф-лы, 130 ил.

Реферат

Область техники

Настоящее изобретение относится к устройству обработки данных и способу обработки данных и, например, в частности, относится к устройству обработки данных и способу обработки данных, который может обеспечить LDPC-код, превосходный по характеристикам частоты появления ошибок.

Уровень техники

LDPC (код с низкой плотностью проверок на четность) код имеет значительные возможности коррекции ошибок, и в последнее время широко применяется в системе передачи, которая включает в себя спутниковое цифровое вещание, такое как DVB (Цифровое телевизионное вещание)-S.2 используемое в Европе (например, см. непатентный документ 1). Кроме того, был протестирован LDPC-код при использовании наземного цифрового вещания следующего поколения, такого как DVB-T.2.

Из недавнего исследования, известно, что производительность вблизи предела Шеннона получают из LDPC-кода, когда длина кода увеличивается, подобно турбо коду. В связи с тем, что LDPC-код имеет свойство, которое заключается в том, что кратчайшее расстояние пропорционально длине кода, то LDPC-код имеет отличные характеристики вероятности искажения блока, будучи старшим, и так называемый, наблюдаемый феномен минимального уровня ошибок при декодировании турбо кода, будучи редко генерируемым, как их характеристики.

Далее будет конкретно описан LDPC-код. LDPC-код является линейным кодом и отсутствует необходимость для LDPC-кода быть двоичным кодом. Тем не менее, в этом случае предполагается, что LDPC-код является двоичным кодом.

Максимальная характеристика LDPC-кода представляет собой разряженную матрицу контроля четности, определяющая LDPC-код. В этом случае, разреженная матрица является матрицей, в которой количество «1» элементов матрицы очень мало (матрица, в которой большинство элементов равны 0).

Фиг. 1 иллюстрирует пример матрицы H контроля четности LDPC-кода.

В матрице H контроля четности на фиг. 1, вес каждого столбца (вес столбца) (число "1") становится равным "3" и вес каждой строки (вес строки) становится равным "6".

При кодировании с использованием LDPC-кода (LDPC-кодирование), например, генераторная матрица G генерируется на основании матрицы H контроля четности и генераторная матрица G умножается на двоичные биты информации, так что генерируется кодовое слово (LDPC-код).

В частности, устройство кодирования, которое выполняет LDPC-кодирование, сначала вычисляет генераторную матрицу G, в которой реализуется выражение GHT=0, между транспонированной матрицей HT матрицы Η проверки четности и генераторной матрицей G. В этом случае, когда генераторная матрица G является К×N матрицей, устройство кодирования умножает генераторную матрицу G на битовую строку (вектор u) информационных битов, включающие в себя К биты, и генерирует кодовое слово с (=uG), включающее в себя N битов. Кодовое слово (LDPC-код), которое генерируется устройством кодирования, принимается на приемной стороне посредством заранее определенного коммуникационного тракта.

LDPC-код может быть декодирован с помощью алгоритма называемого вероятностным декодированием, предложенным Галлагером, то есть алгоритм передачи сообщений, используя распространение степени уверенности в так называемом графе Таннера, включающей в себя переменный узел (также называемый как узел сообщений) и узел проверки. Здесь и далее, переменный узел и узел проверки соответственно называются просто узлами.

Фиг. 2 иллюстрирует последовательность декодирования LDPC-кода.

Далее реальное значение (LLR приема), которое получается путем представления вероятности "0" значения i битового кода LDPC-кода (одно кодовое слово), принятое на приемной стороне посредством логарифмического отношения правдоподобия, соответственно упоминается как приемное значение u0i. Кроме того, сообщение, вырабатываемое узлом проверки, упоминается как uj, и сообщение, вырабатываемое переменным узлом, называют vi.

Во-первых, при декодировании LDPC-кода, как показано на фиг. 2, на этапе S11 принимается LDPC-код, сообщение uj (сообщение узла проверки) инициализируется на "0", и переменная k, принимая целое число в качестве счетчика повторений обработки, инициализируется на "0", и процесс обработки переходит к этапу S12. На этапе S12 сообщение vi (сообщение переменного узла) рассчитывается посредством выполнения операции (операция переменного узла), представленное выражением (1), на основании приемного значения u0i, полученного путем приема LDPC-кода, и сообщение uj рассчитывается посредством выполнения операции (операция узла проверки), представленное выражением (2), на основании сообщения vi.

[Математика. 1]

[Математика. 2]

Здесь dv и dc в выражении (1) и выражении (2) соответственно являются параметрами, которые могут быть выбраны произвольно, и иллюстрирует число "1" в продольном направлении (колонка) и в поперечном направлении (строка) матрицы Н контроля четности. Например, в случае LDPC-кода ((3, 6) LDPC-кода) по отношению к матрице Н контроля четности с весом 3 столбца и весом 6 строк, как показано на фиг. 1, устанавливаются dv=3 и dc=6.

В операции переменного узла выражения (1) и операции узла проверки выражения (2), так как сообщение поступает на вход от границы (линия соединения переменного узла и узла проверки) для вывода сообщения, не является целевой операцией, рабочий диапазон становится равным от 1 до dv - 1 или от 1 до dc - 1. Операция узла проверки выражения (2) выполняется фактически посредством ранее составленной таблицы функции R (v1, v2), представленной выражением (3), определяется одним выходом по отношению к двум входам v1 и v2, и используя таблицу последовательно (рекурсивно), как представлено выражением (4).

[Математика. 3]

[Математика. 4]

На этапе S12 переменная k получает приращение на "1" и процесс обработки переходит на этап S13. На этапе S13 определяется, превышает ли переменная k на количество раз С заданное количество повторений декодирования. Когда определено на этапе S13, что переменная k не превышает С, то процесс обработки возвращается на этап S12, и тот же процесс обработки повторяется.

Когда определено на этапе S13, что переменная k превышает С, то процесс обработки переходит к этапу S14, сообщение vi, которое соответствует результату декодирования, который представляет собой окончательное выходное значение, рассчитывается посредством выполнения операции, представленная выражением (5), и выводится, и на этом процесс декодирования LDPC-кода заканчивается.

[Математика. 5]

В этом случае операция по выражению (5) выполняется с помощью сообщений uj из всех границ с переменным узлом, отличная от операции переменного узла выражения (1).

Фиг. 3 иллюстрирует пример матрицы Н контроля четности (3, 6) LDPC-кода (скорость 1/2 кодирования и кодовая длина 12).

В матрице Н контроля четности на фиг. 3, вес столба установлен на 3 и вес строки установлен на 6, аналогично показанной на фиг. 1.

Фиг. 4 иллюстрирует граф Таннера матрицы Н контроля четности на фиг. 3.

На фиг. 4, узел проверка представлен "+" (плюс) и переменный узел представлен «=» (равно). Узел проверки и переменный узел соответствуют строке и столбцу матрицы Н контроля четности. Линия, которая соединяет узел проверки и переменный узел, является границей и соответствует "1" элементов матрицы контроля четности.

То есть, когда элемент j-й строки и i-го столбца матрицы контроля четности равен 1, на фиг. 4, то i-й переменный узел (узел "=") с верхней стороны и j-й узел проверки (узел "+") с верхней стороны, соединены гранью. Грань показывает, что битовый код, соответствующий переменному узлу, имеет условие ограничения, соответствующее узлу проверки.

В алгоритме сумма-произведение, который является способом декодирования LDPC-кода, операция переменного узел и узла проверки периодически выполняются.

Фиг. 5 иллюстрирует операцию переменного узла, который выполняется с помощью переменного узла.

В переменном узле сообщение vi, которое соответствует грани для расчета, вычисляется посредством операции переменного узла в выражении (1), используя сообщения u1 и u2 из оставшихся граней, соединенных с переменным узлом, и приемное значение u0i. Сообщения, которые соответствуют другим граням, также рассчитываются тем же способом.

Фиг. 6 иллюстрирует операцию узла проверка, которая выполняется с помощью узла проверки.

В этом случае, операция узла проверки выражения (2) может быть переписана посредством выражения (6), используя соотношение выражения а×b=exp{ln(|а|)+ln(|b|)}×sign(а)×sign(b). Тем не менее, sign(х) является 1 в случае x≥0 и является -1 в случае x<0.

[Математика. 6]

При x≥0, если функция φ(х) определяется как выражение φ(х)=ln(tanh(x/2)), то выполняется выражение φ-1(x)=2tanh-1 (е-x). По этой причине, выражение (6) может быть изменено на выражение (7).

[Математика. 7]

В узле проверки, операция узла проверки выражения (2) выполняется в соответствии с выражением (7).

То есть, в узле проверки, как показано на фиг. 6, сообщение uj, которое соответствует границе для расчета, вычисляется с помощью операции узла проверки выражения (7), используя сообщения v1, v2, v3, v4 и v5 из остальных граней, соединенных с узлом проверки. Сообщения, которые соответствуют другим граням, также рассчитываются тем же способом.

Функция φ(x) выражения (7) может быть представлена в виде φ(x)=ln((ex+1)/(ex-1)) и φ(x)=φ-1(x) выполняется при x>0. Когда функции φ(x) и φ-1(x) установлены на аппаратном оборудовании, функции φ(x) и φ-1(x) могут быть установлены с помощью LUT (просмотровой таблицы). Тем не менее, обе функции φ(x) и φ-1(x) становятся теми же LUT.

Перечень ссылок

Непатентный документ

Непатентный документ 1: DVB-S.2: ETSI EN 302307 V1.2.1 (2009-08)

Раскрытие изобретения

Технические задачи, решаемые с помощью изобретения

DVB стандарт, такой как DVB-S.2, DVB-T.2 и DVB-C.2, которые используют LDPC-код, рассматривает LDPC-код в качестве символа (отображает в символической форме) ортогональной модуляции (цифровой модуляции), такой как QPSK (квадратурная фазовая манипуляция), и символ отображается на сигнальной точке и передается.

Кстати, в последние годы возникла потребность в эффективной передаче, например, данных с большой емкостью, таких как, так называемое 4k изображение, с разрешением по ширине и длине 3840×2160 пикселей изображения четырехкратной полной высокой четкости и 3D (размерность) изображения.

Тем не менее, если приоритет отдан эффективной передаче данных, то частота появления ошибок увеличивается.

С другой стороны, есть случай, когда необходимо осуществить передачу данных с. низким значением частоты появления ошибок, даже если эффективность передачи данных в некоторой степени снижается.

Предполагается, что передача данных с различными значениями эффективности будет востребована в будущем, но, в соответствии с LDPC-кодом, например, путем подготовки множества LDPC-кодов различных скоростей кодирования, можно выполнить передачу данных с различными значениями эффективности.

Таким образом, для передачи данных, желательно, адаптировать скорости кодирования LDPC-кодов, для которых легко могут быть установлены несколько увеличенных значений скоростей кодирования (например, число, равное или больше требуемой для передачи данных).

Дополнительно, даже в случае, когда используется LDPC-код любой скорости кодирования, желательно, чтобы величина сопротивления возникновению ошибки была высокой (сильной), то есть, величина частоты появления ошибок имела превосходное значение.

Настоящее изобретение сделано с учетом такой ситуации и может обеспечить LDPC-код с превосходным значением частоты появления ошибок.

Решения технической задачи

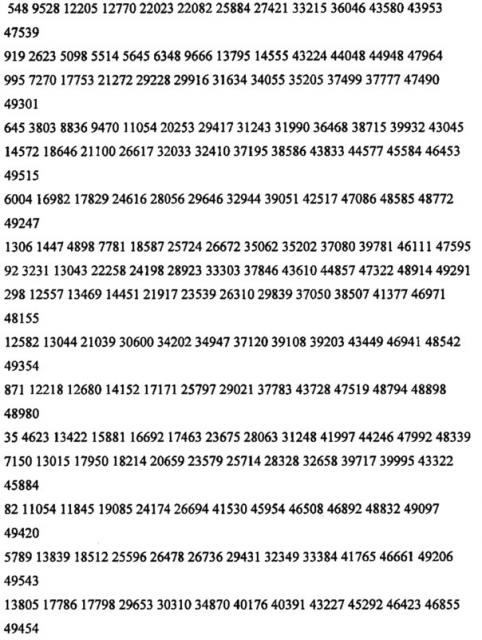

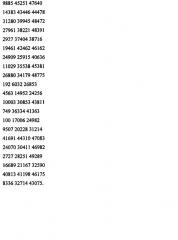

Первое устройство обработки или способ обработки данных в соответствии с настоящим изобретением включает в себя блок кодирования или этап кодирования для кодирования битов информации в LDPC-коде с кодовой длиной 64800 битов и скоростью кодирования 7/30, на основании матрицы контроля четности LDPC (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Второе устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 7/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Третье устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок кодирования или этап кодирования для кодирования бита информации LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 8/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Четвертое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 8/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Пятое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок кодирования или этап кодирования для кодирования бита информации LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 9/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Шестое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 9/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Седьмое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя этап кодирования для кодирования бита информации LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 10/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Восьмое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 10/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую информационному биту, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Девятое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 11/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Десятое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 11/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

В соответствии с настоящим изобретением, бит информации кодируется в LDPC-коде с кодовой длинной 64800 битов и скоростями кодирования 7/30, 8/30, 9/30, 10/30 или 11/30 на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность).

В соответствии с настоящим изобретением LDPC-код с кодовой длиной 64800 битов и скоростями кодирования 7/30, 8/30, 9/30, 10/30 или 11/30 декодируется на основании матрицы контроля четности LDPC-кода (кода с низкой плотностью проверок на четность).

LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую информационному биту, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах.

Таблица начальных значений матрицы контроля четности со скоростью кодирования 7/30 выражается следующим образом

Таблица начальных значений матрицы контроля четности со скоростью кодирования 8/30 выражается следующим образом

Таблица начальных значений матрицы контроля четности со скоростью кодирования 9/30 выражается следующим образом

Таблица начальных значений матрицы контроля четности со скоростью кодирования 10/30 выражается следующим образом

Таблица начальных значений матрицы контроля четности со скоростью кодирования 11/30 выражается следующим образом

Устройство обработки данных может быть независимым устройством и может быть внутренним блоком, образуя одно устройство.

Полезные результаты изобретения

В соответствии с настоящим изобретением можно обеспечить LDPC-код с превосходным значением частоты появления ошибок.

Краткое описание чертежей

Фиг. 1 является иллюстрацией матрицы Н контроля четности LDPC-кода.

Фиг. 2 представляет собой блок-схему алгоритма, иллюстрирующую последовательность декодирования LDPC-кода.

Фиг. 3 является иллюстрацией примера матрицы контроля четности LDPC-кода.

Фиг. 4 является иллюстрацией графа Таннера матрицы контроля четности.

Фиг. 5 является иллюстрацией переменного узла.

Фиг. 6 является иллюстрацией узла проверки.

Фиг. 7 является иллюстрацией примера конфигурации варианта осуществления системы передачи, к которой применяется настоящее изобретение.

Фиг. 8 является блок-схемой, иллюстрирующей пример конфигурации передающего устройства 11.

Фиг. 9 показывает блок-схему, иллюстрирующую пример конфигурации битового перемежителя 116.

Фиг. 10 является иллюстрацией матрицы контроля четности.

Фиг. 11 является иллюстрацией матрицы контроля четности.

Фиг. 12 является иллюстрацией матрицы контроля четности LDPC-кода, определенного в стандарте DVB-S.2.

Фиг. 13 является иллюстрацией матрицы контроля четности LDPC-кода, определенного в стандарте DVB-S.2.

Фиг. 14 является иллюстрацией расположения 16QAM сигнальных точек.

Фиг. 15 является иллюстрацией расположения 64QAM сигнальных точек.

Фиг. 16 является иллюстрацией расположения 64QAM сигнальных точек.

Фиг. 17 является иллюстрацией расположения 64QAM сигнальных точек.

Фиг. 18 является иллюстрацией расположения сигнальных точек, как определено в стандарте DVB-S.2.

Фиг. 19 является иллюстрацией расположения сигнальных точек, как определено в стандарте DVB-S.2.

Фиг. 20 является иллюстрацией расположения сигнальных точек, как определено в стандарте DVB-S.2.

Фиг. 21 является иллюстрацией расположения сигнальных точек, как определено в стандарте DVB-S.2.

Фиг. 22 является иллюстрацией процесса обработки демультиплексора 25.

Фиг. 23 является иллюстрацией процесса обработки демультиплексора 25.

Фиг. 24 является иллюстрацией графа Таннера для декодирования LDPC-кода.

Фиг. 25 является иллюстрацией матрицы Нт четности, которая приобретает ступенчатую структуру, и графа Таннера, соответствующего матрице Нт четности.

Фиг. 26 является иллюстрацией матрицы Нт четности матрицы H контроля четности, соответствующего LDPC-кода, после перемежения битов четности.

Фиг. 27 является иллюстрацией преобразованной матрицы контроля четности.

Фиг. 28 является иллюстрацией процесса обработки скручивания столбцов перемежителем 24.

Фиг. 29 является иллюстрацией нумерации колонки памяти 31, что необходимо для скручивания столбцов перемежителем и адреса позиции начала записи.

Фиг. 30 является иллюстрацией нумерации столбцов памяти 31, что необходимо для скручивания столбцов перемежителем и адреса позиции начала записи.

Фиг. 31 является блок-схемой алгоритма, иллюстрирующей процесс обработки, выполняемым битовым перемежителем 116 и QAM кодером 117.

Фиг. 32 является иллюстрацией модели канала связи, принятой посредством моделирования.

Фиг. 33 является иллюстрацией отношения частоты возникновения ошибок, полученной путем моделирования, и доплеровской частоты fd флаттера.

Фиг. 34 является иллюстрацией отношения частоты возникновения ошибок, полученной путем моделирования, и доплеровской частоты fd флаттера.

Фиг. 35 является блок-схемой, иллюстрирующей пример конфигурации LDPC-кодера 115.

Фиг. 36 является блок-схемой алгоритма, иллюстрирующей процесс обработки LDPC-кодера 115.

Фиг. 37 является иллюстрацией примера таблицы начальных значений матрицы проверки четности, в которой скорость кодирования равна 1/4 и кодовая длина составляет 16200.

Фиг. 38 является иллюстрацией способа вычисления матрицы H контроля четности таблицы начальных значений матрицы контроля четности.

Фиг. 39 является иллюстрацией характеристики BER/FER LDPC-кода, чья кодовая длина определяется в стандарте DVB-S.2 и равна 64800 бит.

Фиг. 40 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 2/30 и кодовая длина равна 64800.

Фиг. 41 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 3/30 и кодовая длина равна 64800.

Фиг. 42 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 4/30 и кодовая длина составляет 64800.

Фиг. 43 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 5/30 и кодовая длина составляет 64800.

Фиг. 44 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 6/30 и кодовая длина составляет 64800.

Фиг. 45 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 7/30 и кодовая длина составляет 64800.

Фиг. 46 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 8/30 и кодовая длина составляет 64800.

Фиг. 47 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 8/30 и кодовая длина составляет 64800.

Фиг. 48 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 9/30 и кодовая длина составляет 64800.

Фиг. 49 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 9/30 и кодовая длина составляет 64800.

Фит.50 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 10/30 и кодовая длина составляет 64800.

Фиг. 51 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 10/30 и кодовая длина составляет 64800.

Фиг. 52 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 11/30 и кодовая длина составляет 64800.

Фиг. 53 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 11/30 и кодовая длина составляет 64800.

Фиг. 54 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 12/30 и кодовая длина составляет 64800.

Фиг. 55 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 12/30 и кодовая длина составляет 64800.

Фиг. 56 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 13/30 и кодовая длина составляет 64800.

Фиг. 57 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 13/30 и кодовая длина составляет 64800.

Фиг. 58 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 14/30 и кодовая длина составляет 64800.

Фиг. 59 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 14/30 и кодовая длина составляет 64800.

Фиг. 60 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 15/30 и кодовая длина составляет 64800.

Фиг. 61 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 15/30 и кодовая длина составляет 64800.

Фиг. 62 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 16/30 и кодовая длина составляет 64800.

Фиг. 63 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 16/30 и кодовая длина составляет 64800.

Фиг. 64 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 16/30 и кодовая длина составляет 64800.

Фиг. 65 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 17/30 и кодовая длина составляет 64800.

Фиг. 66 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 17/30 и кодовая длина составляет 64800.

Фиг. 67 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 17/30 и кодовая длина составляет 64800.

Фиг. 68 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 18/30 и кодовая длина составляет 64800.

Фиг. 69 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 18/30 и кодовая длина составляет 64800.

Фиг. 70 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 18/30 и кодовая длина составляет 64800.

Фиг. 71 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 19/30 и кодовая длина составляет 64800.

Фиг. 72 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 19/30 и кодовая длина составляет 64800.

Фиг.73 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирова