Устройство обработки данных и способ обработки данных

Иллюстрации

Показать всеИзобретение относится к технике связи и предназначено для обработки данных. Технический результат – обеспечение хорошего качества связи при передаче данных с использованием LDPC-кода. Для этого в устройстве передачи при перестановке с целью сопоставления бита LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, с битом символа, соответствующим любой из 8 сигнальных точек, определенных 8-позиционной PSK, когда 3 бита кода, которые сохранены в трех блоках памяти емкостью 16200/3 битов и которые побитно считаны из блоков памяти, сопоставляют одному символу, бит b0, бит b1 и бит b2 переставляют соответственно с битами y0, y1 и y2. Возвращают к исходной позицию переставленного бита кода, полученного из данных, переданных из устройства передачи. 4 н.п. ф-лы, 79 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение касается устройства обработки данных и способа обработки данных и, например, в частности касается устройства обработки данных и способа обработки данных, которые способны обеспечить хорошее качество связи при передаче данных с использованием LDPC кода.

Уровень техники

LDPC-код (Код с малой плотностью проверок на четность) обладает высокой способностью исправления ошибок и в последние годы широко применяется в системах передачи, в том числе в системах цифрового спутникового вещания, таких как используемая в Европе система DVB-S.2 (цифровое телевидение) (смотри, например, непатентный документ 1). Кроме того, исследована возможность применения LDPC-кода в наземном цифровом вещании следующего поколения, таком как DVB-T.2.

В последних исследованиях показано, что LDPC-код показывает характеристики, близкие к границе Шеннона при увеличении длины кода аналогично турбо-коду. Так как для LDPC-кода кратчайшее расстояние пропорционально длине кода, то этот код отличается превосходной вероятностной характеристикой исправления блоков ошибок и редко имеет место так называемый эффект замедления падения вероятности ошибки, который наблюдается при декодировании турбо-кода.

Список цитируемой литературы

Литература, не относящаяся к патентам

Непатентный документ 1: DVB-S.2: ETSIEN 302 307 V1.2.1 (2009-08)

Раскрытие изобретения

Техническая задача

В стандартах DVB, таких как DVB-S.2, DVB-T.2 и DVB-C.2, в которых используют LDPC-код, LDPC-код является символом (преобразован в символ) ортогональной модуляции (цифровой модуляции), такой как QPSK (квадратурная фазовая манипуляция) и символ преобразуют в сигнальную точку ортогональной модуляции и передают.

При передаче данных с использованием LDPC-кода, такой как описанный выше стандарт DVB-S.2, обязательно обеспечивают хорошее качество связи.

С учетом указанных обстоятельств, в соответствии с вариантом осуществления настоящего изобретения, желательно обеспечить хорошее качество связи при передаче данных с использованием LDPC-кода.

Решение задачи

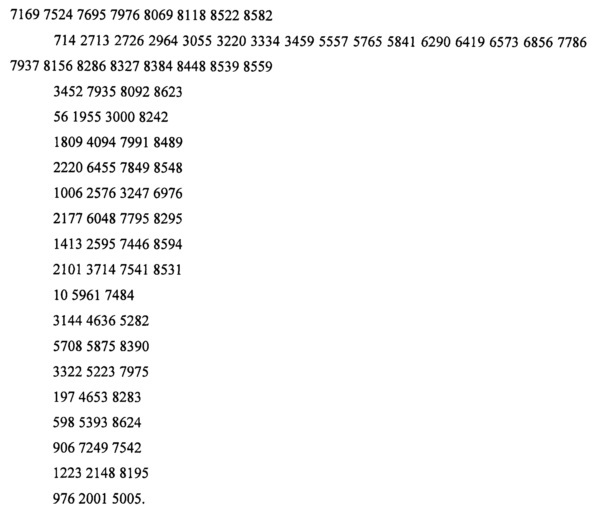

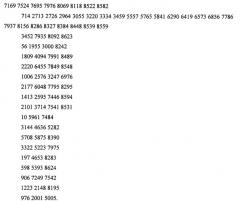

Первое устройство обработки данных или способ обработки данных по настоящему изобретению представляет собой устройство обработки данных или способ обработки данных, которые включают в себя следующее: блок/этап обратной перестановки для осуществления обработки обратной перестановки, для возвращения исходной позиции переставленного бита кода, полученного из данных, переданных от устройства передачи; и блок/этап декодирования для декодирования LDPC-кода, полученного при обработке обратной перестановки, при этом устройство передачи содержит блок кодирования, выполненный с возможностью осуществления LDPC кодирования на основе проверочной матрицы четности LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, и блок перестановки, выполненный с возможностью перестановки бита LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, с битом символа, соответствующим любой из 8 сигнальных точек, определенных 8-позиционной PSK. Когда 3 бита из битов кода, сохранены в трех блоках памятей емкостью 16200/3 битов и считываются побитно из блоков памятей, выделяются одному символу, (#i+1)-й бит от самого старшего бита из 3 битов из битов кода устанавливается в бит b#i, (#i+1)-й бит от самого старшего бита из 3 битов из битов символа одного символа устанавливается в бит y#i, а блок перестановки выполнен с возможностью перестановки: бита b0 и бита y1, бита b1 и бита y0, и бита b2 и бита y2. LDPC-код содержит информационный бит и бит четности. Проверочная матрица четности содержит часть информационной матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Часть информационной матрицы показана таблицей исходных значений для проверочной матрицы. Таблица исходных значений для проверочной матрицы четности является таблицей, показывающей позиции элементов, равных 1, части информационной матрицы для каждых 360 столбцов и имеет вид:

В первом устройстве обработки данных и способе обработки данных по настоящему изобретению осуществляют обработку обратной перестановки для возвращения исходной позиции переставленного бита кода, полученного из данных, переданных устройством передачи; и декодирование LDPC кода полученного посредством указанной обработки обратной перестановки. Устройство передачи содержит блок кодирования, выполненный с возможностью осуществления LDPC кодирования на основе проверочной матрицы четности LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, блок перестановки, выполненный с возможностью перестановки бита LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, с битом символа, соответствующим любой из 8 сигнальных точек, определенных 8-позиционной PSK. Когда 3 бита из битов кода, сохранены в трех блоках памятей емкостью 16200/3 битов и считываются побитно из блоков памятей, выделяются одному символу, (#i+1)-й бит от самого старшего бита из 3 битов из битов кода устанавливаются в бит b#i, (#i+1)-й бит от самого старшего бита из 3 битов из битов символа одного символа устанавливается в бит y#i, а блок перестановки выполнен с возможностью перестановки: бита b0 и бита y1, бита b1 и бита y0, и бита b2 и бита y2. LDPC-код содержит информационный бит и бит четности. Проверочная матрица четности содержит часть информационной матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Часть информационной матрицы показана таблицей исходных значений для проверочной матрицы. Таблица исходных значений для проверочной матрицы четности является таблицей, показывающей позиции элементов, равных 1, части информационной матрицы для каждых 360 столбцов и имеет вид:

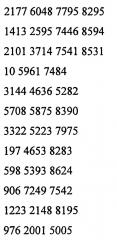

Второе устройство обработки данных или способ обработки данных по настоящему изобретению представляет собой устройство обработки данных или способ обработки данных, которые включают в себя следующее: блок/этап обратной перестановки для осуществления обработки обратной перестановки, для возвращения исходной позиции переставленного бита кода, полученного из данных, переданных от устройства передачи; и блок/этап декодирования для декодирования LDPC-кода, полученного при обработке обратной перестановки, при этом устройство передачи содержит блок кодирования, выполненный с возможностью осуществления LDPC кодирования на основе проверочной матрицы четности LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, и блок перестановки, выполненный с возможностью перестановки бита LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, с битом символа, соответствующим любой из 16 сигнальных точек, определенных 16-позиционной APSK. Когда 4 бита кода, которые сохранены в четырех блоках памятей емкостью 16200/4 битов и которые побитно считаны из блоков памятей, сопоставляют одному символу, (#i+1)-й бит от самого старшего бита из 4 битов кода обозначают через бит b#i, (#i+1)-й бит от самого старшего бита из 4 битов символа одного символа обозначают через бит y#i, и в блоке перестановки сопоставляют бит b0 и бит y2, бит b1 и бит y1, бит b2 и бит y0 и бит b3 и бит y3. LDPC-код содержит информационный бит и бит четности. Проверочная матрица четности содержит часть информационной матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Часть информационной матрицы показана таблицей исходных значений для проверочной матрицы. Таблица исходных значений для проверочной матрицы четности является таблицей, показывающей позиции элементов, равных 1, части информационной матрицы для каждых 360 столбцов и имеет вид:

Во втором устройстве обработки данных и способе обработки данных по настоящему изобретению осуществляют обработку обратной перестановки для возвращения исходной позиции переставленного бита кода, полученного из данных, переданных устройством передачи; и декодирование LDPC кода полученного посредством указанной обработки обратной перестановки. Устройство передачи содержит блок кодирования, выполненный с возможностью осуществления LDPC кодирования на основе проверочной матрицы четности LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, блок перестановки, выполненный с возможностью перестановки бита LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, с битом символа, соответствующим любой из 16 сигнальных точек, определенных 16-позиционной APSK. Когда 4 бита кода, которые сохранены в четырех блоках памятей емкостью 16200/4 битов и которые побитно считаны из блоков памятей, сопоставляют одному символу, (#i+1)-й бит от самого старшего бита из 4 битов кода обозначают через бит b#i, (#i+1)-й бит от самого старшего бита из 4 битов символа одного символа обозначают через бит y#i, и в блоке перестановки сопоставляют бит b0 и бит y2, бит b1 и бит y1, бит b2 и бит y0 и бит b3 и бит y3. LDPC-код содержит информационный бит и бит четности. Проверочная матрица четности содержит часть информационной матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Часть информационной матрицы показана таблицей исходных значений для проверочной матрицы. Таблица исходных значений для проверочной матрицы четности является таблицей, показывающей позиции элементов, равных 1, части информационной матрицы для каждых 360 столбцов и имеет вид:

Устройство обработки данных может являться независимым устройством и может являться внутренним блоком, входящим в состав одного устройства.

Полезные свойства изобретения

В соответствии с вариантом осуществления настоящего изобретения возможно обеспечить хорошее качество связи при передаче данных с использованием LDPC-кода.

Полезные свойства, описанные в настоящем документе, являются только примерами и полезные свойства некоторого варианта осуществления настоящего изобретения не ограничены полезными свойствами, описанными в настоящем документе, и могут существовать другие полезные свойства.

Краткое описание чертежей

Фиг. 1 - вид, показывающий проверочную матрицу Н LDPC-кода;

фиг. 2 - вид, показывающий блок-схему, иллюстрирующую последовательность декодирования LDPC-кода;

фиг. 3 - вид, показывающий пример проверочной матрицы LDPC-кода;

фиг. 4 - вид, показывающий граф Таннера проверочной матрицы;

фиг. 5 - вид, показывающий переменную вершину;

фиг. 6 - вид, показывающий проверочную вершину;

фиг. 7 - вид, показывающий пример конфигурации варианта осуществления системы передачи, в которой применено настоящее изобретение;

фиг. 8 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства 11 передачи;

фиг. 9 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства 116 перемежения битов;

фиг. 10 - вид, показывающий проверочную матрицу;

фиг. 11 - вид, показывающий матрицу контроля четности;

фиг. 12 - вид, показывающий проверочную матрицу LDPC-кода, определенного в стандарте DVB-S.2;

фиг. 13 - вид, показывающий проверочную матрицу LDPC-кода, определенного в стандарте DVB-S.2;

фиг. 14 - вид, показывающий расположение сигнальных точек 16-позиционной QAM;

фиг. 15 - вид, показывающий расположение сигнальных точек 64-позиционной QAM;

фиг. 16 - вид, показывающий расположение сигнальных точек 64-позиционной QAM;

фиг. 17 - вид, показывающий расположение сигнальных точек 64-позиционной QAM;

фиг. 18 - вид, показывающий расположение сигнальных точек, определенное в стандарте DVB-S.2;

фиг. 19 - вид, показывающий расположение сигнальных точек, определенное в стандарте DVB-S.2;

фиг. 20 - вид, показывающий расположение сигнальных точек, определенное в стандарте DVB-S.2;

фиг. 21 - вид, показывающий расположение сигнальных точек, определенное в стандарте DVB-S.2;

фиг. 22 - вид, показывающий обработку, осуществляемую в устройстве 25 демультиплексирования;

фиг. 23 - вид, показывающий обработку, осуществляемую в устройстве 25 демультиплексирования;

фиг. 24 - вид, показывающий граф Таннера для декодирования LDPC-кода;

фиг. 25 - вид, показывающий матрицу HT контроля четности, имеющую ступенчатую структуру, и граф Таннера, соответствующий матрице HT контроля четности;

фиг. 26 - вид, показывающий матрицу HT контроля четности проверочной матрицы H, которая соответствует LDPC-коду после перемежения битов контроля четности;

фиг. 27 - вид, показывающий преобразованную проверочную матрицу;

фиг. 28 - вид, показывающий обработку, осуществляемую в устройстве 24 прокручивания

столбцов;

фиг. 29 - вид, показывающий количество столбцов в памяти 31, необходимое для прокручивания столбцов и адрес позиции начала записи;

фиг. 30 - вид, показывающий количество столбцов в памяти 31, необходимое для прокручивания столбцов и адрес позиции начала записи;

фиг. 31 - вид, показывающий блок-схему, иллюстрирующую процесс обработки, осуществляемый в устройстве 116 перемежения битов и устройстве 117 преобразования;

фиг. 32 - вид, показывающий модель канала связи, которая применялась для моделирования;

фиг. 33 - вид, показывающий взаимосвязь частоты появления ошибки, которая получена при моделировании, и доплеровской частоты fd дрожания;

фиг. 34 - вид, показывающий взаимосвязь частоты появления ошибки, которая получена при моделировании, и доплеровской частоты fd дрожания;

фиг. 35 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства 115 LDPC кодирования;

фиг. 36 - вид, иллюстрирующий блок-схему, показывающую процесс обработки, осуществляемый в устройстве 115 LDPC кодирования;

фиг. 37 - вид, показывающий пример таблицы исходных значений для проверочной матрицы кода со скоростью кодирования, равной 1/4, и длиной кода, равной 16200;

фиг. 38 - вид, иллюстрирующий способ вычисления проверочной матрицы H по таблице исходных значений для проверочной матрицы;

фиг. 39 - вид, показывающий пример таблицы исходных значений для проверочной матрицы 16К кода для Sx с r=7/15;

фиг. 40 - вид, показывающий пример таблицы исходных значений для проверочной матрицы 16К кода для Sx с r=8/15;

фиг. 41 - вид, показывающий пример графа Таннера такого сочетания с последовательностью степеней, в которой вес столбца равен 3, а вес строки равен 6;

фиг. 42 - вид, показывающий пример графа Таннера сочетания многореберного типа;

фиг. 43 - вид, показывающий минимальную длину цикла и порог эффективности проверочной матрицы 16К кода для Sx;

фиг. 44 - вид, показывающий проверочную матрицу 16К кода для Sx;

фиг. 45 - вид, показывающий проверочную матрицу 16К кода для Sx;

фиг. 46 - вид, показывающий процесс перестановки в соответствии с настоящим способом;

фиг. 47 - вид, показывающий процесс перестановки в соответствии с настоящим способом;

фиг. 48 - вид, показывающий первый пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 8-позиционная PSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 49 - вид, показывающий второй пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 8-позиционная PSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 50 - вид, показывающий результат моделирования при измерении BER/FER в ходе моделирования;

фиг. 51 - вид, показывающий результат моделирования при измерении BER/FER в ходе моделирования;

фиг. 52 - вид, показывающий структурную схему, иллюстрирующую модель системы передачи, используемой при моделировании;

фиг. 53 - вид, показывающий первый пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 54 - вид, показывающий второй пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 55 - вид, показывающий третий пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 56 - вид, показывающий четвертый пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 57 - вид, показывающий пятый пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 58 - вид, показывающий шестой пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 59 - вид, показывающий седьмой пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 60 - вид, показывающий восьмой пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 61 - вид, показывающий результат моделирования при измерении BER/FER в ходе моделирования;

фиг. 62 - вид, показывающий результат моделирования при измерении BER/FER в ходе моделирования;

фиг. 63 - вид, показывающий пример расположения сигнальных точек 16-позиционной APSK и отношение γрадиусов, когда 16-позиционную APSK используют в качестве способа модуляции.

фиг. 64 - вид, показывающий пример расположения сигнальных точек 16-позиционной APSK и отношение γрадиусов, когда 16-позиционную APSK используют в качестве способа модуляции.

фиг. 65 - вид, показывающий структурную схему примера конфигурации устройства 12 приема с фиг. 7;

фиг. 66 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства 165 обращения перемежения битов;

фиг. 67 - вид, показывающий блок-схему, иллюстрирующую процесс обработки, осуществляемый в устройстве 164 обратного преобразования, устройстве 165 обратного перемежения битов и устройстве 166 LDPC декодирования;

фиг. 68 - вид, показывающий пример проверочной матрицы LDPC-кода;

фиг. 69 - вид, показывающий матрицу (проверочная матрица), полученную путем применения замены строк и замены столбцов к проверочной матрице;

фиг. 70 - вид, показывающий проверочную матрицу, разделенную на блоки из матриц размера 5×5;

фиг. 71 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства декодирования, в котором осуществляют совместно Р преобразований вершины;

фиг. 72 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства 166 LDPC декодирования;

фиг. 73 - вид, показывающий обработку, осуществляемую устройством 54 мультиплексирования, входящим в состав устройства 165 обращения перемежения битов;

фиг. 74 - вид, показывающий обработку, осуществляемую устройством 55 обращения прокручивания столбцов;

фиг. 75 - вид, иллюстрирующий структурную схему, показывающую другой пример конфигурации устройства 165 обращения перемежения битов;

фиг. 76 показана структурная схема, иллюстрирующая первый пример конфигурации системы приема, которая может быть применена в устройстве 12 приема,

фиг. 77 - вид, иллюстрирующий структурную схему, показывающую второй пример конфигурации системы приема, которая может быть применена в устройстве 12 приема;

фиг. 78 - вид, иллюстрирующую структурную схему, показывающую третий пример конфигурации системы приема, которая может быть применена в устройстве 12 приема;

фиг. 79 - вид, показывающий структурную схему, иллюстрирующую пример конфигурации варианта осуществления компьютера, в котором применено настоящее изобретение.

Осуществление изобретения

Далее перед описанием вариантов осуществления настоящего изобретения будет описан LDPC-код.

LDPC-код

LDPC-код является линейным кодом и LDPC-код не обязательно является двоичным кодом. Тем не менее, в рассматриваемом случае предполагаем, что LDPC-код является двоичным кодом.

Наиболее значительное свойство LDPC-кода заключается в том, что проверочная матрица, определяющая LDPC-код, является разряженной. В рассматриваемом случае под разряженной матрицей понимается матрица, в которой очень мало количество элементов, равных «1» (практически все элементы матрицы равны 0).

На фиг. 1 показан пример проверочной матрицы Н LDPC-кода.

В проверочной матрице Н с фиг. 1 вес каждого столбца (вес столбца) (количество элементов, равных «1») равен «3», а вес каждой строки (вес строки) равен «6».

При осуществлении кодирования, например, с помощью LDPC-кода (LDPC кодирование) на основе проверочной матрицы Н получают порождающую матрицу G и для получения кодового слова (LDPC-кода) эту порождающую матрицу G умножают на двоичные информационные биты.

В частности, в устройстве кодирования, осуществляющем LDPC кодирование, сначала вычисляют порождающую матрицу G, которая удовлетворяет равенству GHT=0 для транспонированной матрицы HT проверочной матрицы Н и порождающей матрицы G. В этом случае порождающая матрица G является K×N матрицей, в устройстве кодирования умножают порождающую матрицу G на строку битов (вектор u), которая состоит из K информационных бит, в результате чего получают кодовое слово с (=uG), состоящее из N бит. Кодовое слово (LDPC-код), полученное в устройстве кодирования, передают по заранее заданному каналу связи и получают на приемной стороне.

LDPC-код можно декодировать с помощью алгоритма, называемого вероятностным декодированием и предложенного Галлагером (Gallager), то есть алгоритма передачи сообщений с использованием распространения надежности на, так называемом, графе Таннера, который содержит переменную вершину (также называемую вершиной сообщения) и проверочную вершину. Здесь и далее и переменную вершину, и проверочную вершину будем называть просто вершиной.

На фиг. 2 показана процедура декодирования LDPC-кода.

Здесь и далее действительное число (принятое LLR), полученное представлением правдоподобия «0» значения i-го бита LDPC-кода (одно кодовое слово), полученного на приемной стороне, в виде логарифма отношения правдоподобия, называют принятым значением u0i. Кроме того, сообщение, выходящее из проверочной вершины, обозначаем через uj, а сообщение, выходящее из переменной вершины, обозначаем через vi.

При декодировании LDPC-кода сначала, как показано на фиг. 2, на этапе S11 принимают LDPC-код и сообщению (сообщению проверочной вершины) uj присваивают значение «0», а переменной k, которая является целым числом и представляет собой счетчик повторений процесса обработки, присваивают значение «0», после чего обработка переходит на этап S12. На этапе S12 сообщение (сообщение переменной вершины) vi вычисляют путем осуществления преобразования (преобразование переменной вершины), представленного в равенстве (1), что делают на основе принятого значения u0i, полученного при приеме LDPC-кода, и сообщение uj вычисляют путем осуществления преобразования (преобразование проверочной вершины), представленного в равенстве (2), что делают на основе сообщения vi.

Здесь dv и dc в равенстве (1) и равенстве (2) являются соответственно параметрами, которые могут быть выбраны произвольным образом и которые представляют собой количество «1» в продольном направлении (направлении столбцов) и поперечном направлении (направлении строк) проверочной матрицы Н. Например, в случае LDPC-кода ((3, 6) LDPC-кода) с проверочной матрицей Н, в которой вес столбца равен 3, а вес строки равен 6, как показано на фиг. 1, устанавливают dv=3 и dc=6.

В преобразовании переменной вершины из равенства (1) и преобразовании проверочной вершины из равенства (2), так как сообщение, поступившее на вход по ребру (линии, соединяющей переменную и проверочную вершины) с целью подачи на выход сообщения, не является целью преобразования, результат преобразования находится в диапазоне от 1 до dv-1 или от 1 до dc-1. Преобразование проверочной вершины из равенства (2) фактически осуществляют путем предварительной подготовки таблицы значений функции R (v1, v2), которая представлена в равенстве (3) и результатом которой является одно число, полученное по двум входам v1 и v2 и последующим последовательным (рекурсивным) использованием таблицы в соответствии с равенством (4).

На этапе S12 значение переменной k увеличивается на «1» и обработка переходит на этап S13. На этапе S13 определяют, превосходит ли значение переменной k заранее заданное количество С повторений декодирования. Если на этапе S13 определяют, что значение переменной k не превосходит С, то обработка возвращается на этап S12 и повторяют аналогичный процесс.

Когда на этапе S13 определяют, что значение переменной k превосходит С, то обработка переходит на этап S14, и сообщение vi, которое соответствует результату декодирования, подаваемому на выход, вычисляют путем выполнения преобразования, представленного равенством (5), указанное сообщение подают на выход и заканчивают процесс декодирования LDPC-кода.

В рассматриваемом случае, преобразование из равенства (5) выполняют с использованием сообщений uj от всех ребер, соединенных с переменной вершиной, и указанное преобразование отлично от преобразования переменной вершины из равенства (1).

На фиг. 3 показан пример проверочной матрицы Н (3, 6) LDPC-кода (скорость кодирования равна 1/2, а длина кода равна 12).

В проверочной матрице Н с фиг. 3 вес столбца равен 3, а вес строки равен 6 аналогично фиг. 1.

На фиг. 4 показан граф Таннера проверочной матрицы Н с фиг. 3.

На фиг. 4 проверочные вершины обозначены «+» (плюс), а переменные вершины обозначены «=» (равно). Проверочная и переменная вершины соответствуют строке и столбцу проверочной матрицы Н соответственно. Линия, которая соединяет проверочную вершину с переменной вершиной является ребром и соответствует «1» из элементов проверочной матрицы.

То есть, когда элемент j-й строки и i-го столбца проверочной матрицы равен 1, на фиг. 4, i-я сверху переменная вершина (вершина «=») и j-я сверху проверочная вершина (вершина «+») соединены ребром. Ребро показывает, что на бит кода, соответствующий переменной вершине, наложено ограничение, соответствующее проверочной вершине.

В алгоритме суммы произведений, который представляет собой способ декодирования LDPC-кода, преобразование переменной вершины и преобразование проверочной вершины выполняются неоднократно.

На фиг. 5 показано преобразование переменной вершины, которое осуществляют в переменной вершине.

В переменной вершине сообщение vi соответствующее ребру для вычислений, вычисляют в ходе преобразования переменной вершины, которое соответствует равенству (1) и которое использует сообщения u1 и u2 из оставшихся ребер, соединенных с переменной вершиной, и использует принятое значение u0i. Сообщения, которые соответствуют другим ребрам, также вычисляют с помощью того же способа.

На фиг. 6 показано преобразование проверочной вершины, которое осуществляют в проверочной вершине.

В этом случае преобразование проверочной вершины, которое соответствует равенству (2), может быть переписано с помощью равенства (6) с использованием равенства . Тем не менее, sign(x) равен 1 в случае x≥0 и равен -1 в случае x<0.

При x≥0, если функция φ(x) определена с помощью равенства , то справедливо равенство . По этой причине равенство (6) может быть заменено равенством (7).

В проверочной вершине преобразование проверочной вершины, соответствующее равенству (2), осуществляют в соответствии с равенством (7).

То есть в проверочной вершине, как показано на фиг. 6, сообщение uj, соответствующее ребру для вычислений, вычисляют в ходе преобразования проверочной вершины, которое соответствует равенству (7) и которое использует сообщения v1, v2, v3, v4 и v5 из оставшихся ребер, соединенных с проверочной вершиной. Сообщения, которые соответствуют другим ребрам, также вычисляют с помощью того же способа.

Функция φ(x) из равенства (7) может быть представлена следующим образом и справедливо при x>0. Когда функции φ(x) и реализованы аппаратно, функции φ(x) и могут быть реализованы с использованием LUT (Таблица соответствия). Тем не менее, обе функции φ(x) и становятся одной и той же LUT.

Пример конфигурации системы передачи, в которой применено настоящее изобретение

На фиг. 7 показан пример конфигурации варианта осуществления системы передачи (под системой понимается логическое объединение множества устройств и устройство любой конфигурации может быть расположено или может не быть расположено в одном и том же корпусе), в которой применено настоящее изобретение.

На фиг. 7, система передачи содержит устройство 11 передачи и устройство 12 приема.

Например, устройство 11 передачи передает (транслирует) (перемещает) программу телевизионного вещания и так далее. То есть, например, в устройстве 11 передачи кодируют целевые данные, которые являются целью передачи, такие как изображения, звуковые данные, как программу, с помощью LDPC-кода и, например, передают полученные данные, например, по каналу 13 связи, такому как спутниковая схема, поверхностные волны и кабель (проводная схема).

В устройстве 12 приема принимают LDPC-код, переданный устройством 11 передачи по каналу 13 связи, декодируют LDPC-код с целью получения целевых данных и подают на выход целевые данные.

В этом случае известно, что LDPC-код, использованный системой передачи с фиг. 7, показывает очень высокую эффективность в канале связи с AWGN (аддитивным белым гауссовским шумом).

Тем не менее, в канале 13 связи могут быть выработаны пакетные ошибки или стирание информации. Особенно в случае, когда канал 13 связи является поверхностной волной, например, в системе OFDM (ортогональное частотное разделение каналов) мощность конкретного символа может стать равной 0 (стирание) в соответствии с задержкой эха (каналы, отличные от главного) в многоканальной среде, в которой отношение сигнала к шуму равно 0 дБ (мощность шума = эха равна мощности сигнала = главный канал).

При дрожании (канал связи, в котором задержка равна нулю и добавляется эхо с доплеровской частотой), когда отношение сигнала к шуму равно 0 дБ, мощность всего OFDM символа в конкретный момент времени может стать равной 0 (стирание) из-за доплеровской частоты.

Кроме того, пакетные ошибки могут иметь место из-за ситуации с проводной линией от блока приема (не показан на чертежах) на стороне устройства 12 приема, например, когда антенна принимает сигнал от устройства 11 передачи, до устройства 12 приема, или в ситуации нестабильности подачи электроэнергии в устройство 12 приема.

Между тем, при декодировании LDPC-кода, в переменной вершине, соответствующей столбцу проверочной матрицы Н, и биту LDPC-кода, как показано выше на фиг. 5, осуществляют преобразование переменной вершины, соответствующее равенству (1) с добавлением (принятого значения u0i) бита LDPC-кода. По этой причине, если в битах кода, используемых для преобразования переменной вершины, происходит ошибка, то ухудшается точность вычисленного сообщения.

При декодировании LDPC-кода, в проверочной вершине преобразование проверочной вершины, соответствующее равенству (7), осуществляют с использованием сообщения, вычисленного в переменной вершине, соединенной с проверочной вершиной. По этой причине, если увеличивается количество проверочных вершин, для которых одновременно происходят ошибки (в том числе стирания) во множестве соединенных переменных вершин (соответствующие биты LDPC-кода), то уменьшается эффективность декодирования.

То есть, если в двух или нескольких переменных вершинах из переменных вершин, соединенных с проверочной вершиной, одновременно происходит стирание, то проверочная вершина возвращает сообщение, для которого вероятность того, что значение равно 0, и вероятность того, что значение равно 1, равны для всех переменных вершин. В этом случае проверочная вершина, которая возвращает сообщение с равными вероятностями, не вносит вклада в процесс декодирования (один набор из преобразования переменной вершины и преобразования проверочной вершины). В результате необходимо увеличить количество повторений процесса декодирования, эффективность декодирования уменьшается и увеличивается потребление электроэнергии устройством 12 приема, которое осуществляет декодирования LDPC-кода.

Следовательно, в системе передачи с фиг. 7 может быть улучшена устойчивость к пакетной ошибке или стиранию при одновременном поддержании эффективности в канале связи с AWGN (AWGN канал).

Пример конфигурации устройства 11 передачи

На фиг. 8 показана структурная схема примера конфигурации устройства 11 передачи с фиг. 7.

В устройстве 11 передачи один или несколько входных потоков, соответствующих целевым данным, подают в устройство 111 адаптации режима/мультиплексирования.

В устройстве 111 адаптации режима/мультиплексирования осуществляют выбор режима и, при необходимости, такие процессы, как мультиплексирование одного или нескольких поданных входных потоков, и подают полученные в результате данные в подстроечный конденсатор 112.

В подстроечном конденсаторе 112 осуществляют необходимое дополнение нулями (вставка пустот) данных, поданных из устройства 111 адаптации режима/мультиплексирования, и подают полученные в результате данные в устройство 113 ВВ скремблирования.

В устройстве 113 ВВ скремблирования осуществляют скремблирование основной полосы (ВВ скремблирование) данных, поданных из подстроечного конденсатора 112, и подают полученные в результате данные в устройство 114 ВСН кодирования.

В устройстве 114 ВСН кодирования осуществляют ВСН кодирование данных, поданных из устройства 113 ВВ скремблирования, и подают полученные в результате данные как целевые данные LDPC, являющиеся целью LDPC кодирования, в устройство 115 LDPC кодирования.

В устройстве 115 LDPC кодирования осуществляют LDPC кодирование в соответствии с проверочной матрицей, в которой матрица контроля четности, являющаяся частью, соответствующей биту четности LDPC-кода, обладает ступенчатой структурой для целевых данных LDPC, поданных из устройства 114 ВСН кодирования, и подают на выход LDPC-код, в котором целевыми данными LDPC являются информационные биты.

То есть в устройстве 115 LDPC кодирования осуществляют LDPC кодирование с целью кодирования целевых данных LDPC с использованием LDPC-кода, такого как LDPC-код (соответствующий проверочной матрице), определенный в заранее заданном стандарте DVB-S.2, DVB-T.2, DVB-C.2 или подобном, и как результат подают на выход полученный заранее