Устройство обработки данных и способ обработки данных

Иллюстрации

Показать всеИзобретение относится к технике связи и может быть использовано для обработки данных. Технический результат – обеспечение хорошего качества связи при передаче данных, используя код LDPC. Для этого бит кода для кода LDPC, в котором длина кода составляет 16200 битов и скорость кодирования составляет 8/15, обменивают с символьным битом символа, соответствующего любой из 8 точек сигнала, определенных 8PSK. Когда 3 бита битов кода, сохраненных в трех модулях хранения, имеющих емкость хранения 16200/3 битов, и считываемых поразрядно из модулей хранения, выделяют для одного символа, (#i+1)-й бит от старшего значащего бита из 3 битов из битов кода устанавливают в бит b#i, (#i+1)-й бит от старшего значащего бита из 3 битов символьных битов одного символа устанавливают в бит y#i и бит b0 обменивают на бит y1, бит b1 обменивают на бит у0 и бит b2 обменивают на бит у2. 4 н. и 2 з.п. ф-лы, 79 ил.

Реферат

Область техники, к которой относится изобретение

Настоящая технология относится к устройству обработки данных и способу обработки данных, и, например, в частности, относится к устройству обработки данных и способу обработки данных, которые позволяют обеспечить хорошее качество связи при передаче данных, используя код LDPC.

Уровень техники

Код LDPC (проверка на четность низкой плотности) обладает высокими возможностями коррекции ошибок и в настоящее время был широко принят для систем передачи, включающих в себя спутниковую цифровую широковещательную передачу данных, такую как DVB (цифровая широковещательная передача видеоданных) -S.2, используемую в Европе (например, см. Непатентную литературу 1). Кроме того, выполняется проверка использования кода LDPC для наземной цифровой широковещательной передачи данных следующего поколения, такой как DVB-T.2.

Исходя из последних исследований, известно, что рабочие характеристики, близкие к пределу Шеннона, получают с помощью кода LDPC при увеличении длины кода, аналогично турбокоду. Поскольку код LDPC обладает таким свойством, что кратчайшее расстояние пропорционально длине кода, код LDPC обладает преимуществами исключительной характеристики вероятности ошибки блока, и для него характерно, так называемое, явление минимального уровня ошибки, наблюдаемое в характеристиках декодирования редко генерируемого турбокода.

Список литературы

Непатентная литература

Непатентная литература 1: DVB-S.2: ETSI EN 302 307 V1.2.1 (2009-08)

Раскрытие изобретения

Техническая задача

В стандарте DVB, таком как DVB-S.2, DVB-T.2 и DVB-C.2, в котором используется код LDPC, из кода LDPC формируют символ (символизируют) ортогональной модуляции (цифровой модуляции), такой как QPSK (квадратурная фазовая модуляция), и этот символ отображают на точку сигнала ортогональной модуляции и передают.

При передаче данных, используя код LDPC, такой как DVB-S.2, описанный выше, необходимо обеспечить хорошее качество связи.

Учитывая такие обстоятельства, в соответствии с вариантом осуществления настоящей технологии, желательно обеспечить хорошее качество связи при передаче данных, используя код LDPC.

Решение задачи

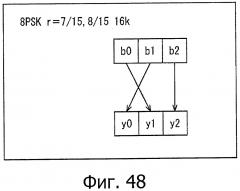

Первое устройство обработки данных или способ обработки данных в соответствии с настоящей технологией представляет собой устройство обработки данных или способ обработки данных, включающий в себя: модуль/этап кодирования для выполнения кодирования LDPC на основе матрицы проверки на четность кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15; и модуль/этап взаимного обмена для обмена битом кода для кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, с символьным битом символа, соответствующего любой из 8 точек сигнала, определенных 8PSK. Когда 3 бита битов кода, сохраненных в трех модулях сохранения, имеющих емкость сохранения 16200/3 битов, и считываемых поразрядно из модулей сохранения, выделяют для одного символа, (#i+1)-ый бит от старшего значащего бита из 3 битов из битов кода устанавливают в бит b#i, (#i+1)-ый бит от старшего значащего бита из 3 битов символьных битов одного символа устанавливают в бит y#i, и модуль/этап взаимного обмена выполняет обмен бита b0 на бит y1, бита b1 на бит y0 и бита b2 на бит y2. Код LDPC включает в себя информационный бит и бит четности. Матрица проверки на четность включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Информационная часть матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, представляющую положения элементов 1 из информационной части матрицы для каждых 360 столбцов, и выражена следующим образом

32 384 430 591 1976 1296 1976 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1976 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1976 1461 1976 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464.

В первом устройстве обработки данных и способе обработки данных в соответствии с настоящей технологией, кодирование LDPC выполняют на основе матрицы проверки на четность кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, и бит кода для кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, обменивают с символьным битом символа, соответствующего любой из 8 точек сигнала, определенных 8PSK. При взаимном обмене, когда 3 бита битов кода, сохраненных в трех модулях сохранения, имеющих емкость сохранения 16200/3 битов, и считываемых поразрядно из модулей сохранения, выделяют для одного символа, (#i+1)-ый бит от старшего значащего бита из 3 битов из битов кода устанавливают в бит b#i, (#i+1)-ый бит от старшего значащего бита из 3 битов символьных битов одного символа устанавливают в бит y#i, бит b0 обменивают на бит y1, бит b1 обменивают на бит y0, и бит b2 обменивают на бит у2. Код LDPC включает в себя информационный бит и бит четности. Матрица проверки на четность включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Информационная часть матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, представляющую положения элементов 1 из информационной части матрицы для каждых 360 столбцов, и выражена следующим образом

32 384 430 591 1976 1296 1976 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1976 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1976 1461 1976 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208

7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464.

Второе устройство обработки данных или способ обработки данных в соответствии с настоящей технологией представляет собой устройство обработки данных или способ обработки данных, включающий в себя: модуль/этап кодирования для выполнения кодирования LDPC на основе матрицы проверки на четность кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15; и модуль/этап взаимного обмена для обмена битом кода для кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, с символьным битом символа, соответствующего любой из 16 точек сигнала, определенных 16APSK. Когда 4 бита битов кода, сохраненных в четырех модулях сохранения, имеющих емкость сохранения 16200/4 битов, и считываемых поразрядно из модулей сохранения, выделяют для одного символа, (#i+1)-ый бит от старшего значащего бита из 4 битов из битов кода устанавливают в бит b#i, (#i+1)-ый бит от старшего значащего бита из 4 битов символьных битов одного символа устанавливают в бит y#i, и модуль/этап взаимного обмена выполняет обмен бита b0 на бит у2, бита b1 на бит y1, бита b2 на бит y0 и бита b3 на бит у3. Код LDPC включает в себя информационный бит и бит четности. Матрица проверки на четность включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Информационная часть матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, представляющую положения элементов 1 из информационной части матрицы для каждых 360 столбцов, и выражена следующим образом

32 384 430 591 1976 1296 1976 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1976 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1976 1461 1976 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464.

Во втором устройстве обработки данных и способе обработки данных в соответствии с настоящей технологией, кодирование LDPC выполняют на основе матрицы проверки на четность кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, и бит кода для кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, обменивают с символьным битом символа, соответствующего любой из 16 точек сигнала, определенных 16APSK. При взаимном обмене, когда 4 бита битов кода, сохраненных в четырех модулях сохранения, имеющих емкость сохранения 16200/4 битов, и считываемых поразрядно из модулей сохранения, выделяют для одного символа, (#i+1)-ый бит от старшего значащего бита из 4 битов из битов кода устанавливают в бит b#i, (#i+1)-ый бит от старшего значащего бита из 4 битов символьных битов одного символа устанавливают в бит y#i, бит b0 обменивают на бит у2, бит b1 обменивают на бит y1, бит b2 обменивают на бит y0, и бит b3 обменивают на бит у3. Код LDPC включает в себя информационный бит и бит четности. Матрица проверки на четность включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Информационная часть матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, представляющую положения элементов 1 из информационной части матрицы для каждых 360 столбцов, и выражена следующим образом

32 384 430 591 1976 1296 1976 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1976 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1976 1461 1976 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464.

Устройство обработки данных может представлять собой независимое устройство и может представлять собой внутренний блок, составляющий одно устройство.

Полезные эффекты изобретения

В соответствии с вариантом осуществления настоящей технологии, можно обеспечить хорошее качество связи при передаче данных, используя код LDPC.

Предпочтительные эффекты, представленные в настоящем описании, являются просто примером, и полезные эффекты варианта осуществления настоящей технологии не ограничены предпочтительными эффектами, представленными в настоящем описании, и могут присутствовать дополнительные полезные эффекты.

Краткое описание чертежей

На фиг. 1 представлена иллюстрация матрицы H проверки на четность кода LDPC.

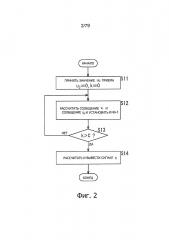

На фиг. 2 показана блок-схема последовательности операций, поясняющая последовательность декодирования кода LDPC.

На фиг. 3 представлена иллюстрация примера матрицы проверки на четность кода LDPC.

На фиг. 4 представлена иллюстрация графа Таннера матрицы проверки на четность. На фиг. 5 представлена иллюстрация переменного узла. На фиг. 6 представлена иллюстрация узла управления.

На фиг. 7 представлена иллюстрация примера конфигурации варианта осуществления системы передачи, в которой применяется настоящее изобретение.

На фиг. 8 показана блок-схема, поясняющая пример конфигурации устройства 11 передачи.

На фиг. 9 показана блок-схема, поясняющая пример конфигурации перемежителя 116 битов.

На фиг. 10 представлена иллюстрация матрицы проверки на четность.

На фиг. 11 представлена иллюстрация матрицы четности.

На фиг. 12 представлена иллюстрация матрицы проверки на четность кода LDPC, определенного в стандарте DVB-S.2.

На фиг. 13 представлена иллюстрация матрицы проверки на четность кода LDPC, определенного в стандарте DVB-S.2.

На фиг. 14 представлена иллюстрация компоновки точки сигнала 16QAM.

На фиг. 15 представлена иллюстрация компоновки точки сигнала 64QAM.

На фиг. 16 представлена иллюстрация компоновки точки сигнала 64QAM.

На фиг. 17 представлена иллюстрация компоновки точки сигнала 64QAM.

На фиг. 18 представлена иллюстрация компоновки точки сигнала, определенной в стандарте DVB-S.2.

На фиг. 19 представлена иллюстрация компоновки точки сигнала, определенной в стандарте DVB-S.2.

На фиг. 20 представлена иллюстрация компоновки точки сигнала, определенной в стандарте DVB-S.2.

На фиг. 21 представлена иллюстрация компоновки точки сигнала, определенной в стандарте DVB-S.2.

На фиг. 22 представлена иллюстрация обработки демультиплексора 25.

На фиг. 23 представлена иллюстрация обработки демультиплексора 25.

На фиг. 24 представлена иллюстрация графа Таннера для декодирования кода LDPC.

На фиг. 25 представлена иллюстрация матрицы ΗT четности, становящейся ступенчатой структурой, и графа Таннера, соответствующего матрице ΗT четности.

На фиг. 26 представлена иллюстрация матрицы ΗT четности матрицы Η проверки на четность, соответствующей коду LDPC после перемежения четности.

На фиг. 27 представлена иллюстрация преобразованной матрицы проверки на четность.

На фиг. 28 представлена иллюстрация обработки перемежителя 24 со скручиванием столбцов.

На фиг. 29 представлена иллюстрация номера столбца запоминающего устройства 31, необходимого для перемежения со скручиванием столбцов, и адреса положения начала записи.

На фиг. 30 представлена иллюстрация номера столбца запоминающего устройства 31, необходимого для перемежения со скручиванием столбцов, и адреса положения начала записи.

На фиг. 31 показана обработка, иллюстрирующая блок-схему последовательности операций, выполняемых перемежителем 116 битов и преобразователем 117.

На фиг. 32 представлена иллюстрация модели канала связи, принятого в результате моделирования.

На фиг. 33 представлена иллюстрация соотношения частоты ошибок, полученного моделированием, и частоты fd Допплера, вызывавшей дрожание частоты.

На фиг. 34 представлена иллюстрация соотношения частоты ошибок, полученного моделированием, и частоты fd Допплера, вызывавшей дрожание частоты.

На фиг. 35 показана блок-схема, поясняющая пример конфигурации кодера 115 LDPC.

На фиг. 36 показана обработка, иллюстрирующая блок-схему последовательности операций кодера 115 LDPC.

На фиг. 37 представлена иллюстрация примера таблицы исходного значения матрицы проверки на четность, в которой скорость кодирования составляет 1/4, и длина кода равна 16200.

На фиг. 38 представлена иллюстрация способа вычисления матрицы Η проверки на четность из таблицы исходного значения матрицы проверки на четность.

На фиг. 39 представлена иллюстрация примера таблицы исходного значения матрицы проверки на четность кода 16k для Sx при r=7/15.

На фиг. 40 представлена иллюстрация примера таблицы исходного значения матрицы проверки на четность кода 16k для Sx при r=8/15.

На фиг. 41 представлена иллюстрация примера графа Таннера такой группы последовательности степени, в которой вес столбца равен 3, и вес строки равен 6.

На фиг. 42 представлена иллюстрация примера графа Таннера группы типа с множеством ребер.

На фиг. 43 представлена иллюстрация минимальной длины цикла и с порогом рабочей характеристики матрицы проверки на четность кода 16k для Sx.

На фиг. 44 представлена иллюстрация матрицы проверки на четность кода 16k для Sx.

На фиг. 45 представлена иллюстрация матрицы проверки на четность кода 16k для Sx.

На фиг. 46 представлена иллюстрация обработки взаимного обмена, в соответствии с текущим способом.

На фиг. 47 представлена иллюстрация обработки взаимного обмена, в соответствии с текущим способом.

На фиг. 48 представлена иллюстрация первого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 8PSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

На фиг. 49 представлена иллюстрация второго примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 8PSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

На фиг. 50 представлена иллюстрация результата моделирования для измерения BER/FER путем моделирования.

На фиг. 51 представлена иллюстрация результата моделирования для измерения BER/FER путем моделирования.

На фиг. 52 показана блок-схема, поясняющая модель системы передачи для системы передачи, в которой используется моделирование.

На фиг. 53 представлена иллюстрация первого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

На фиг. 54 представлена иллюстрация второго примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

На фиг. 55 представлена иллюстрация третьего примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

На фиг. 56 представлена иллюстрация четвертого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

На фиг. 57 представлена иллюстрация пятого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

На фиг. 58 представлена иллюстрация шестого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

На фиг. 59 представлена иллюстрация седьмого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

На фиг. 60 представлена иллюстрация восьмого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

На фиг. 61 представлена иллюстрация результата моделирования для измерения BER/FER путем моделирования.

На фиг. 62 представлена иллюстрация результата моделирования для измерения BER/FER путем моделирования.

На фиг. 63 представлена иллюстрация примера компоновки точек сигнала 16APSK и отношения γ радиуса, когда 16APSK принят как способ модуляции.

На фиг. 64 представлена иллюстрация примера компоновки точек сигнала 16APSK и отношения γ радиуса, когда 16APSK принят как способ модуляции.

На фиг. 65 показана блок-схема, поясняющая пример конфигурации приемного устройства 12 на фиг. 7.

На фиг. 66 показана блок-схема, поясняющая пример конфигурации обратного перемежителя 165 битов

На фиг. 67 показана блок-схема последовательности операций, иллюстрирующая, обработку, выполняемую обратным преобразователем 164, обратным перемежителем 165 битов и декодером 166 LDPC.

На фиг. 68 представлена иллюстрация примера матрицы проверки на четность кода LDPC.

На фиг. 69 представлена иллюстрация матрицы (матрица проверки на четность), полученной при выполнении замены строки и замен столбца в отношении матрицы проверки на четность.

На фиг. 70 представлена иллюстрация матрицы проверки на четность, которая была разнесена в модулях матриц размером 5×5.

На фиг. 71 показана блок-схема, поясняющая пример конфигурации устройства декодирования, которое совместно выполняет операцию узла по Р.

На фиг. 72 показана блок-схема, поясняющая пример конфигурации декодера 166 LDPC.

На фиг. 73 представлена иллюстрация обработки мультиплексора 54 образования обратного перемежителя 165 битов.

На фиг. 74 представлена иллюстрация обработки обратного перемежителя 55 со скручиванием столбцов.

На фиг. 75 показана блок-схема, поясняющая другой пример конфигурации обратного перемежителя 165 битов.

На фиг. 76 показана блок-схема, поясняющая первый пример конфигурации системы приема, которую можно применять в приемном устройстве 12.

На фиг. 77 показана блок-схема, поясняющая второй пример конфигурации системы приема, которую можно применять в приемном устройстве 12.

На фиг. 78 показана блок-схема, поясняющая третий пример конфигурации системы приема, которую можно применять в приемном устройстве 12.

На фиг. 79 показана блок-схема, поясняющая пример конфигурации варианта осуществления компьютера, в котором применяется настоящая технология.

Осуществление изобретения

Ниже будет описан код LPDC перед описанием вариантов осуществления настоящей технологии.

Код LDPC

Код LDPC представляет собой линейный код, и код LDPC не обязательно должен представлять собой двоичный код. Однако, в данном случае, предполагается, что код LDPC представляет собой двоичный код.

Максимальная характеристика кода LDPC состоит в том, что матрица проверки на четность, определяющая код LDPC, является разреженной. В этом случае разреженная матрица представляет собой матрицу, в которой количество "1" среди элементов матрицы очень мало (матрица, в которой большинство элементов составляет 0).

На фиг. 1 показана иллюстрация примера матрицы H проверки на четность кода LDPC.

В матрице H проверки на четность по фиг. 1 вес каждого столбца (вес столбца) (количество "1") становится равным "3", и вес каждого ряда (вес ряда) становится равным "6".

При кодировании используют код LDPC (кодирование LDPC), например, матрицу G генерирования генерируют на основе матрицы H проверки на четность, и матрицу G генерирования умножают на биты двоичной информации, таким образом, что генерируется кодовое слово (код LDPC).

В частности, устройство кодирования, которое выполняет кодирование LDPC, вначале рассчитывает матрицу G генерирования, в которой реализуется уравнение GHT=0, между транспонированной матрицей ΗT матрицы H проверки на четность и матрицей G генерирования. В этом случае, когда матрица G генерирования представляет собой матрицу K×N, устройство кодирования умножает матрицу G генерирования на строку битов (вектор u) информационных битов, включающих в себя K битов, и генерирует кодовое слово с (=uG), включающее в себя N битов. Кодовое слово (код LDPC), которое генерирует устройство кодирования, принимают на стороне приема, используя заданный путь связи.

Код LDPC может быть декодирован с использованием алгоритма, называемого вероятностным декодированием, предложенным Галлагером, то есть, с использованием алгоритма передачи сообщений, используя распространение доверия по, так называемому, графу Таннера, включающему в себя переменный узел (также называется узлом сообщения) и узел проверки. Ниже переменный узел и узел проверки, соответственно, называются просто узлами.

На фиг. 2 показана блок-схема последовательности операций, иллюстрирующая последовательность декодирования кода LDPC.

Ниже реальное значение (прием LLR), которое получают путем представления вероятности "0" значения в i-ом бите кода для кода LDPC (одного кодового слова), принятого стороной приема, логарифмом отношения вероятностей, соответственно, называются значением u0i приема. Кроме того, выход сообщения из узла проверки называют uj, и выход сообщения из переменного узла обозначают как vi.

Вначале, при декодировании кода LDPC, как представлено на фиг. 2, на этапе S11, принимают код LDPC, сообщение (сообщение узла проверки) uj инициализируют в "0", и переменную k, которая принимает значение целого числа, в качестве счетчика повторения обработки инициализируют в "0", и обработка переходит на этап S12. На этапе S12 сообщение (сообщение переменного узла) vi рассчитывают путем выполнения операции (операция переменного узла), представленной уравнением (1), на основе значения u0i приема, полученного при приеме кода LDPC, и сообщение uj рассчитывают путем выполнения операции (операции проверочного узла), представленной уравнением (2), на основе сообщения vi.

Уравнение 1

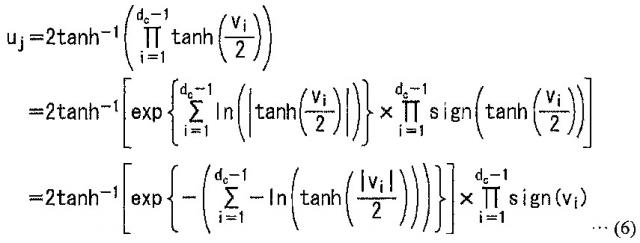

Уравнение 2

Здесь dv и dc в уравнении (1) и в уравнении (2), соответственно, представляют собой параметры, которые могут быть произвольно выбраны и иллюстрируется количество "1" в продольном направлении (столбец) и в поперечном направлении (ряд) в матрице Н проверки на четность. Например, в случае кода LDPC (код LDPC (3, 6)) в отношении матрицы Н проверки на четность с весом столбца 3 и весом ряда 6, как представлено на фиг. 1, устанавливают dv=3 и dc=6.

В операции переменного узла в уравнении (1) и в операции проверочного узла в уравнении (2), поскольку сообщение, введенное из ребра (линия, соединяющая переменный узел и проверочный узел) для вывода сообщения, не является целью операции, диапазон операции становится равным от 1 до dv-1 или от 1 до dc-1. Операция проверочного узла в соответствии с уравнением (2), выполняется фактически путем предварительного формирования таблицы функции R (v1, v2), представленной уравнением (3), определенной по выходу в отношении двух входных значений v1 и v2, и последовательно (рекурсивно) используя таблицу, как представлено уравнением (4).

Уравнение 3

Уравнение 4

На этапе S12, выполняют последовательное приращение переменной k на "1", и обработка переходит на этап S13. На этапе S13 определяют, превышает ли величина переменной k заданное число раз С повторений декодирований. Когда на этапе S13 определяют, что переменная k не больше чем С, обработка возвращается на этап S12, и ту же обработку повторяют ниже.

Когда на этапе S13 определяют, что переменная k больше, чем С, обработка переходит на этап S14, сообщение vi, которое соответствует результату декодирования, которое должно быть в конечном итоге выведено, рассчитывают путем выполнения операции, представленной уравнением (5), и выводят, и обработка декодирования кода LDPC заканчивается.

Уравнение 5

В этом случае, операция по уравнению (5) выполняется, используя сообщение uj из всех ребер, соединенных с переменным узлом, отличных от операции переменного узла в соответствии с уравнением (1).

На фиг. 3 представлена иллюстрация примера матрицы Н проверки на четность для кода LDPC (3, 6) (скорость кодирования 1/2 и длина кода 12).

В матрице Н проверки на четность по фиг. 3 вес столбца установлен равным 3, и вес ряда установлен равным 6, аналогично фиг. 1.

На фиг. 4 представлена иллюстрация графа Таннера матрицы Н проверки на четность по фиг. 3.

На фиг. 4 проверочный узел представлен "+" (плюс), и переменный узел представлен "=" (равенство). Проверочный узел и переменный узел соответствуют ряду и столбцу матрицы Н проверки на четность. Линия, которая соединяет проверочный узел и переменный узел, представляет собой кромку и соответствует "1" элементов матрицы проверки на четность.

Таким образом, когда элемент j-ого ряда и i-ого столбца матрицы проверки на четность равен 1, на фиг. 4, i-ый переменный узел (узел "=") с верхней стороны и j-ый проверочный узел (узел "+") с верхней стороны соединяются ребром. Ребро представляет, что бит кода, соответствующий переменному узлу, имеет состояние ограничения, соответствующее проверочному узлу.

В алгоритме произведения суммы, который представляет собой способ декодирования для кода LDPC, многократно выполняют операцию переменного узла и операцию проверочного узла.

На фиг. 5 показана иллюстрация операции переменного узла, которая выполняется переменным узлом.

В переменном узле сообщение vi, которое соответствует кромке для расчетов, рассчитывают с помощью операции переменного узла по уравнению (1), используя сообщения u1 и u2 из остальных ребер, соединенных с переменным узлом и значением u0i приема. Сообщения, которые соответствуют другим ребрам, также рассчитывают, используя тот же способ.

На фиг. 6 представлена иллюстрация операции проверочного узла, которую выполняет проверочный узел.

В этом случае, операция проверочного узла по уравнению (2) может быть перезаписана уравнением (6), используя соотношение уравнения а×b=exp{ln(|а |)+ln(|b|)}×sign(а)×sign(b). Однако, sign(x) равен 1, в случае х≥0, и равен -1, в случае х<0.

Уравнение 6

При х≥0, если функция φ(х) определена, как уравнение φ(х)=ln (tanh (х/2)), реализуется уравнение φ-1(х)=2tanh-1(e-x). По этой причине уравнение (6) может быть изменено в уравнение (7).

Уравнение 7

В проверочном узле операцию проверочного узла в соответствии с уравнением (2) выполняют в соответствии с уравнением (7).

Таким образом, в проверочном узле, как представлено на фиг. 6, сообщение uj, которое соответствует ребру для расчета, рассчитывают, используя операцию проверочного узла по уравнению (7), используя сообщения v1, v2, v3, v4 и v5 из оставшихся ребер, соединенных с проверочным узлом. Сообщения, которые соответствуют другим ребрам, также рассчитывают с помощью того же способа.

Функция φ(х) в уравнении (7) может быть представлена, как φ(х)=ln((ех+1)/(ех-1)), и φ(х)=φ-1(х) удовлетворяется при х>0. Когда функции φ(х) и φ-1(х) воплощают в виде аппаратных средств, функции φ(х) и φ-1(х) могут быть воплощены, используя LUT (справочную таблицу). Однако, обе функции φ(х) и φ-1(х) становятся одной LUT.

Пример конфигурации системы передачи, в которой применяется настоящая технология

На фиг. 7 показана иллюстрация примера конфигурации варианта осуществления системы передачи (термин система означает логическое объединение множества устройств, и устройство в каждой конфигурации может быть размещено или может не быть размещено в одном и том же корпусе), в котором применяется настоящее изобретение.

На фиг. 7 система передачи включает в себя устройство 11 передачи и устройство 12 приема.

Например, устройство 11 передачи передает (выполняет широковещательную передачу) (передает) программу телевизионной широковещательной передачи, и так далее. Таким образом, например, устройство 11 передачи кодирует целевые данные, которые представляют собой цель передачи, такие как данные изображения и аудиоданные, как программу, в кодах LDPC, и, например, передает их через путь 13 передачи данных, такой как спутниковый контур, наземная волна и кабель (проводной контур).

Устройство 12 приема принимает код LDPC, переданный из устройства 11 передачи через путь 13 передачи данных, декодирует код LDPC для получения целевых данных, и выводит эти целевые данные.

В этом случае, известно, что код LDPC, используемый системой передачи по фиг. 7, проявляет очень высокие возможности на пути передачи данных в условиях AWGN (аддитивного белого Гауссова шума).

В то же время, на пути 13 передачи данных могут быть сгенерированы пакетная ошибка или разрушение информации. В частности, в случае, когда путь 13 передачи данных представляет собой наземную волну, например, в системе OFDM (ортогональное мультиплексирование с частотным разделением), мощность определенного символа может стать равной 0 (разрушение информации) в соответствии с задержкой эхо-сигнала (другого канала распространения, чем основной канал), в среде с многолучевым распространением, в которой D/U (отношение желательного к нежелательному) составляет 0 дБ (мощность нежелательного = мощность эхо-сигнала, равная мощности желательного = основной канал распространения).

В случае частотного дрожания сигнала (канал передачи данных, в котором суммируют задержку, равную 0, и эхо-сигнал, имеющий допплеровскую частоту), когда D/U составляет 0 дБ, общая мощность символа OFDM в определенный момент времени может стать равной 0 (разрушение информации), из-за допплеровской частоты.

Кроме того, пакетная ошибка может быть сгенерирована из-за ситуации в проводной линии от модуля приема (не представлен на чертежах) стороны приемного устройства 12, такого как антенна, принимающая сигнал из устройства 11 передачи, в приемное устройство 12, или из-за нестабильности источника питания приемного устройства 12.

В то же время, при декодировании кода LDPC в переменном узле, в соответствии со столбцом матрицы H проверки на четность, и бита кода для кода LDPC, как представлено на фиг. 5, описанной выше, выполняется операция переменного узла, в соответствии с уравнением (1), с добавлением (значения приема u0i для) кода бита для кода LDPC. По этой причине, если генерируется ошибка в битах кода, используемых для операции переменного узла, точность рассчитанного сообщения ухудшается.

При декодировании кода LDPC, в проверочном узле, операция проверочного узла по уравнению (7) выполняется, используя сообщение, рассчитанное переменным узлом, соединенным с проверочным узлом. По этой причине, если увеличивается количество проверочных узлов, в которых генерируется ошибка (включая в себя разрушение информации), одновременно в множестве подключенных переменных узлов (кодах бита для кодов LDPC, соответствующих им), характеристика декодирования ухудшается.

Таким образом, если данные в двух или больше переменных узлах для переменных узлов, соединенных с проверочным узлом, одновременно будут разрушены, проверочный узел возвращает сообщение, в котором вероятность значения, равная 0, и вероятность значения, равная 1, равны друг другу для всех переменных узлов. В этом случае проверочный узел, который возвращает сообщение равных вероятностей, не способствует одной обработке декодирования (одному набору операции переменного узла и операции проверочного узла). В результате, необходимо увеличить количество раз повторений обработки декодирования, характеристики декодирования ухудшаются, и увеличивается потребление энергии питания приемного устройства 12, которое выполняет декодирование кода LDPC.

Поэтому, в системе передачи по фиг. 7, устойчивость к пакетным ошибкам или к разрушению может быть улучшена, в то время как рабочие характеристики канала передачи данных AWGN (канала AWGN) сохраняется.

Пример конфигурации устройства 11 передачи

На фиг. 8 показана блок-схема, иллюстрирующая пример конфигурации устройства 11 передачи по фиг. 7.

В устройстве 11 передачи, один или больше входных потоков, соответствующим целевым данным, подают в адаптацию режима/мультиплексор 111.

Адаптация режима/мультиплексор 111 выполняет выбор режима и выполняет такую обработку, как мультиплексирование одного или больше входных потоков, подаваемых в него, в соответствии с необходимостью, и подает полученные в результате данные в заполнитель 112.

Заполнитель 112 выполняет необходимое заполнение нулями (вставку нулей) в отношении данных, подаваемых из режима адаптации/мультиплексора 111, и подает полученные в результате данные в скремблер 113 ВВ.

Скремблер 113 ВВ выполняет скремблирование в основной полосе пропускания (скремблирование ВВ) в отношении данных, подаваемых из заполнителя 112, и подает полученные в результате данные в кодер 114 ВСН.

Кодер 114 ВСН выполняет кодирование ВСН в отношении данных, подаваемых из скремблера 113 ВВ, и подает полученные в р