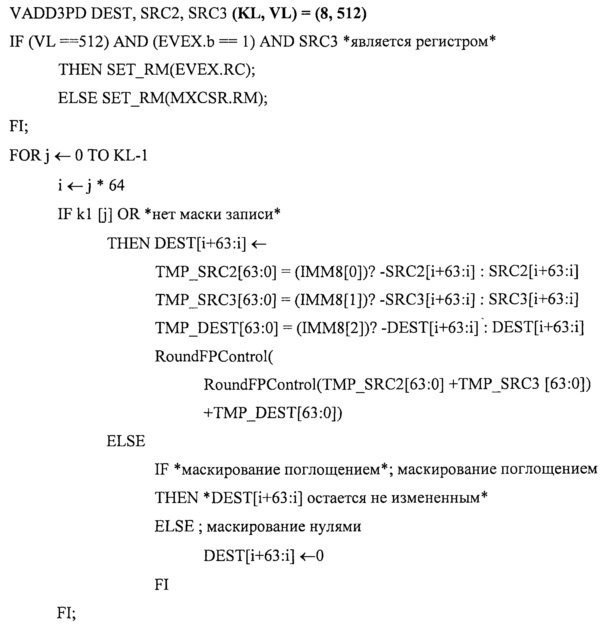

Процессоры, способы, системы и команды для сложения трех операндов-источников с плавающей запятой

Иллюстрации

Показать всеГруппа изобретений относится к области вычислительной техники и может быть использована для сложения чисел с плавающей запятой. Техническим результатом является увеличение производительности. Процессор одного аспекта изобретения содержит блок декодирования для декодирования команды сложения трех источников с плавающей запятой, указывающей первый операнд-источник, содержащий первый элемент данных с плавающей запятой, второй операнд-источник, содержащий второй элемент данных с плавающей запятой, и третий операнд-источник, содержащий третий элемент данных с плавающей запятой. Блок исполнения соединен с блоком декодирования и сохраняет результат в операнде-назначении, который указан командой. Результат содержит результирующий элемент данных с плавающей запятой, который содержит первую округленную сумму с плавающей запятой, которая представляет собой алгебраическую сумму второй округленной суммы с плавающей запятой и третьего элемента данных с плавающей запятой. Вторая округленная сумма с плавающей запятой представляет собой алгебраическую сумму первого элемента данных с плавающей запятой и второго элемента данных с плавающей запятой. 4 н. и 21 з.п. ф-лы, 30 ил., 5 табл.

Реферат

Область техники, к которой относится изобретение

Описанные в настоящем документе варианты осуществления изобретения, в общем, касаются процессоров. В частности, описанные в настоящем документе варианты осуществления изобретения, в общем, касаются процессоров для сложения чисел с плавающей запятой в ответ на команды.

Уровень техники

Числа с, плавающей запятой обычно используются в процессорах, вычислительных системах и других электронных устройствах. Преимущество чисел с плавающей запятой состоит в том, что они позволяют широкий диапазон числовых значений представлять в сравнительно компактном числовом формате и/или сравнительно компактным количеством битов. Биты чисел с плавающей запятой могут быть распределены на несколько составляющих полей, известных как знак, мантисса и показатель степени числа с плавающей запятой. Знак, мантисса, основание и показатель степени могут быть связаны следующим образом:

.

Выражение «(-1)знак» представляет минус единицу в степени, равной знаку. Это выражение вычисляет, является ли число с плавающей запятой положительным (+) или отрицательным (-). Например, когда знак является целым нулем, число с плавающей запятой является положительным, или, в качестве альтернативы, когда знак равен целой единице, число с плавающей запятой является отрицательным. Мантисса содержит строку цифр, длина которой во многом определяет точность числа с плавающей запятой. Мантиссу также иногда называют значащими цифрами, коэффициентом или дробной частью. Запятая (например, десятичная запятая для десятичного формата или двоичная запятая для двоичного формата) обычно неявно расположена в фиксированной позиции (например, непосредственно справа от самой левой или самой старшей цифры мантиссы, что в некоторых случаях может подразумеваться). Примером мантиссы в двоичном случае является «1.10010010000111111011011». Цифры мантиссы, расположенные слева от запятой (например, «10010010000111111011011»), могут представлять биты дробной части. Выражение «основаниепоказатель степени» представляет основание, возведенное в степень, равную показателю степени. Основание обычно является основанием, равным 2 (для двоичного случая), равным 10 (для десятичного случая) или равным 16 (для шестнадцатеричного случая). Основание иногда называют основанием степени. Показатель степени также иногда называют характеристикой или масштабом. Возведение основания в степень, равную показателю степени, фактически сдвигает запятую (например, от неявной или подразумеваемой начальной позиции) на количество позиций, равное показателю степени. Запятую сдвигают вправо, если показатель степени положителен, или влево, если показатель степени отрицателен.

Институт (IEEE) инженеров по электротехнике и электронике стандартизовал несколько различных форматов с плавающей запятой в стандарте IEEE 754. Типично, формат с плавающей запятой одинарной точности содержит 32 бита и содержит 23 бита мантиссы в битах [22:0], 8 битов показателя степени в битах [30:23] и один бит знака в бите [31]. Формат с плавающей запятой двойной точности содержит 64 бита и содержит 52 бита мантиссы в битах [51:0], 11 битов показателя степени в битах [62:52] и один бит знака в бите [63]. В технике также известны другие форматы с плавающей запятой, такие как, например, формат с плавающей запятой половинной точности, формат с плавающей запятой расширенной двойной точности и формат с плавающей запятой четверной точности. Дополнительные подробности о числах и форматах с плавающей запятой, при желании, доступны в IEEE 754.

Краткое описание чертежей

Изобретение будет лучше понятно из последующего описания и приложенных чертежей, используемых для иллюстрации вариантов осуществления изобретения. На чертежах:

Фиг. 1 - вид, показывающий структурную схему одного варианта осуществления процессора, выполненного для реализации варианта осуществления команды сложения трех источников с плавающей запятой;

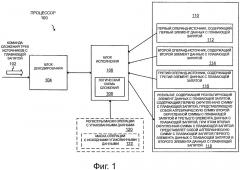

фиг. 2 - вид, показывающий блок-схему одного варианта осуществления способа осуществления варианта осуществления команды сложения трех источников с плавающей запятой;

фиг. 3 - вид, показывающий схему одного варианта осуществления операции сложения трех упакованных, возможно маскированных, источников с плавающей запятой;

фиг. 4 - вид, показывающий схему одного варианта осуществления операции сложения трех скалярных, возможно маскированных, источников с плавающей запятой;

фиг. 5 - вид, показывающий схему одного варианта осуществления операции сложения трех упакованных, возможно маскированных, возможно с управлением отрицанием, источников с плавающей запятой;

фиг. 6 - вид, показывающий схему одного варианта осуществления операции сложения трех скалярных, возможно маскированных, возможно с управлением отрицанием, источников с плавающей запятой;

фиг. 7 - вид, показывающий схему одного варианта осуществления суммирующего устройства для трех источников с плавающей запятой;

фиг. 8 - вид, показывающий схему одного варианта осуществления двух последовательно связанных суммирующих устройств для двух источников с плавающей запятой;

фиг. 9 - вид, показывающий схему одного варианта осуществления суммирующего устройства для двух источников с плавающей запятой с линией повторения, которая связывает выход с входом;

фиг. 10 - вид, показывающий схему одного варианта осуществления подходящего формата команды для команды сложения трех источников с плавающей запятой;

фиг. 11 - вид, показывающий схему одного варианта осуществления подходящего набора регистров упакованных данных;

фиг. 12 - вид, показывающий таблицу, иллюстрирующую то, что количество битов маски зависит от ширины упакованных данных и ширины элемента данных;

фиг. 13 - вид, показывающий схему одного варианта осуществления подходящего набора регистров масок операций;

фиг. 14А-14В - виды, показывающие схемы, иллюстрирующие общий формат векторно-ориентированных команд и его шаблоны команд, в соответствии с вариантами осуществления изобретения;

фиг. 15А - вид, показывающий схему одного примера конкретного формата векторно-ориентированных команд, в соответствии с вариантами осуществления изобретения;

фиг. 15В - вид, показывающий схему, иллюстрирующую поля одного конкретного формата векторно-ориентированных команд, которые составляют поле полного кода операции, в соответствии с одним вариантом осуществления изобретения;

фиг. 15С - вид, показывающий схему, иллюстрирующую поля одного конкретного формата векторно-ориентированных команд, которые составляют поле индекса регистра, в соответствии с одним вариантом осуществления изобретения;

фиг. 15D - вид, показывающий схему, иллюстрирующую поля одного конкретного формата векторно-ориентированных команд, который составляют поле операции приращения, в соответствии с одним вариантом осуществления изобретения;

фиг.16 - вид, показывающий схему одного варианта осуществления архитектуры регистров;

фиг. 17А - вид, показывающий структурную схему, иллюстрирующую вариант осуществления конвейера с исполнением команд по очереди и вариант осуществления конвейера с внеочередным исполнением/направлением команд, с переименованием регистров;

фиг. 17В - вид, показывающий структурную схему варианта осуществления ядра процессора, содержащего входной блок, связанный с блоком механизма исполнения, при этом входной блок и блок механизма исполнения связаны с блоком памяти;

фиг. 18А - вид, показывающий структурную схему варианта осуществления одного ядра процессора вместе с соединением с внутренней сетью на кристалле и с локальным подмножеством кэш-памяти уровня 2 (L2);

фиг. 18В - вид, показывающий увеличенную структурную схему варианта осуществления части ядра процессора с фиг. 18А;

фиг. 19 - вид, показывающий структурную схему варианта осуществления процессора, который может содержать более одного ядра, может содержать контроллер интегрированной памяти и может содержать интегрированную графику;

фиг. 20 вид, показывающий структурную схему первого варианта осуществления архитектуры компьютера;

фиг. 21 - вид, показывающий структурную схему второго варианта осуществления архитектуры компьютера;

фиг. 22 - вид, показывающий структурную схему третьего варианта осуществления архитектуры компьютера;

фиг. 23 - вид, показывающий структурную схему четвертого варианта осуществления архитектуры компьютера;

фиг. 24 вид, показывающий структурную схему использования программного устройства преобразования команд для преобразования двоичных команд исходного набора команд в двоичные команды целевого набора команд, в соответствии с вариантами осуществления изобретения.

Осуществление изобретения

В настоящем документе описаны команды сложения трех операндов-источников с плавающей запятой, процессоры для исполнения этих команд, способы, реализуемые процессорами при обработке или исполнении этих команд, и системы, содержащие один или несколько процессоров для обработки или исполнения этих команд. В последующем описании изложено большое количество конкретных подробностей (например, конкретные операции команд, форматы данных, конфигурации процессоров, подробности микроархитектуры, последовательности операций и так далее). Тем не менее, варианты осуществления изобретения могут быть реализованы без этих конкретных подробностей. В других примерах хорошо известные схемы, структуры и технологии не показаны подробно, чтобы не мешать пониманию описания.

На фиг. 1 показана структурная схема одного варианта осуществления процессора 100, выполненного для реализации варианта осуществления команды 102 сложения трех источников с плавающей запятой. В некоторых вариантах осуществления изобретения процессор может быть процессором общего назначения (например, такой тип процессора часто используют в настольных компьютерах, ноутбуках или других компьютерах). В. качестве альтернативы, процессор может быть процессором специального назначения. Примеры подходящих процессоров специального назначения содержат, помимо прочего, графические процессоры, сетевые процессоры, процессоры связи, криптографические процессоры, сопроцессоры, встроенные процессоры, цифровые сигнальные процессоры (DSP) и контроллеры (например, микроконтроллеры). Процессор может быть любым из различных процессоров (CISC) со сложным набором команд, различных процессоров (RISC) с сокращенным набором команд, различных процессоров (VLIW) с очень длинным командным словом, их различных гибридов или процессоров других типов.

Во время работы процессор 100 может принимать вариант осуществления команды 102 сложения трех источников с плавающей запятой. Например, команда сложения трех источников с плавающей запятой может быть принята от блока вызова команд, очереди команд или подобного. Команда сложения трех источников с плавающей запятой может представлять макрокоманду, команду языка ассемблера, команду машинного кода или команду или сигнал управления набора команд процессора. В некоторых вариантах осуществления изобретения команда сложения трех источников с плавающей запятой может прямо определять (например, с помощью одного или нескольких полей или наборов битов) или другим образом указывать (например, неявно указывать, благодаря соотнесению регистра с помощью карты эмуляции регистров и так далее) первый операнд-источник 112, который должен содержать, по меньшей мере, первый элемент данных с плавающей запятой, может определять или другим образом указывать второй операнд-источник 114, который должен содержать, по меньшей мере, второй элемент данных с плавающей запятой, может определять или другим образом указывать третий операнд-источник 116, который должен содержать, по меньшей мере, третий элемент данных с плавающей запятой, и может определять или другим образом указывать операнд-назначение (например, место хранения назначения), где должен храниться результат 118.

Обращаясь снова к фиг. 1, процессор содержит блок декодирования или декодер 104. Блок декодирования может принять и декодировать команду 102 сложения трех источников с плавающей запятой. Блок декодирования может подать на выход одну или несколько микрокоманд, микроопераций, точек входа микрокода, декодированных команд или сигналов управления, или другие сравнительно низкоуровневые команды или сигналы управления, которые отражают, представляют и/или получаются из команды сложения трех источников с плавающей запятой. Одна или несколько низкоуровневых команд или сигналов управления могут реализовывать высокоуровневую команду сложения трех источников с плавающей запятой с помощью одной или нескольких низкоуровневых (например, уровня схемы или уровня аппаратного обеспечения) операций. В некоторых вариантах осуществления изобретения блок декодирования содержит одну или несколько входных структур (например, порт (порты), соединение (соединения), интерфейс и так далее) для приема команды, логическую схему распознавания и декодирования команд, связанную с входными структурами для приема, распознавания и декодирования команды в одну или несколько соответствующих низкоуровневых команд или сигналов управления, и одну или несколько выходных структур (например, порт (порты), соединение (соединения), интерфейс и так далее), связанных с логической схемой распознавания и декодирования команд, для подачи на выход одной или нескольких соответствующих низкоуровневых команд или сигналов управления. Блок декодирования может быть реализован с использованием различных механизмов, в том числе, помимо прочего, постоянных запоминающих устройств (ROM) микрокода, таблиц соответствия, аппаратных реализаций, программируемых логических массивов (PLA) и других известных в технике механизмов.

В некоторых вариантах осуществления изобретения вместо прямого предоставления команды сложения трех источников с плавающей запятой в блок декодирования, при желании, может быть использован эмулятор, транслятор, устройство трансформирования, интерпретатор команд или другой модуль преобразования команд. В технике известны различные типы модулей преобразования команд, и они могут быть реализованы в форме аппаратного обеспечения, программного обеспечения, аппаратнореализованного программного обеспечения или их комбинации. В некоторых вариантах осуществления изобретения модуль преобразования команд может быть расположен снаружи процессора обработки команд, например, на отдельном кристалле и/или в памяти (например, статичный, динамичный модуль или модуль эмуляции команд времени выполнения). В качестве примера модуль преобразования команд может принимать команду сложения трех источников с плавающей запятой, которая может быть из первого набора команд, и может эмулировать, транслировать, трансформировать, интерпретировать или другим образом преобразовывать команду сложения трех источников с плавающей запятой в одну или несколько соответствующих, или полученных промежуточных команд или сигналов управления, которые могут быть из второго другого набора команд. Одна или несколько промежуточных команд или сигналов управления второго набора команд могут быть предоставлены на блок декодирования, который может декодировать принятые одну или несколько команд или сигналов управления второго набора команд в одну или несколько низкоуровневых команд или сигналов управления, которые могут быть исполнены естественным аппаратным обеспечением процессора (например, одним или несколькими блоками исполнения).

Процессор также содержит набор 110 регистров. Каждый из регистров может представлять собой место хранения на кристалле, которое выполнено для хранения данных с плавающей запятой. В качестве примера, регистры могут быть регистрами с плавающей запятой, выполненными с возможностью хранения элементов данных с плавающей запятой, регистрами упакованных данных, выполненными с возможностью хранения упакованных или скалярных элементов данных с плавающей запятой, или подобными. Регистры могут представлять архитектурные или архитектурно видимые регистры (например, файл архитектурных регистров), которые видимы программному обеспечению и/или программисту и/или могут являться регистрами, указанными командами набора команд процессора для идентификации операндов. Эти архитектурные регистры отличаются от других не архитектурных регистров или не архитектурно видимых регистров в заданной микроархитектуре (например, временные регистры, буферы переупорядочивания, регистров выгрузки и так далее). Регистры могут быть реализованы различным образом в различных микроархитектурах с использованием хорошо известных технологий, и они не ограничены каким-либо конкретным типом схемы. Примеры подходящих типов регистров содержат, помимо прочего, специальные физические регистры, динамически выделяемые физические регистры с использованием переименования регистров и комбинации перечисленного.

В некоторых вариантах осуществления изобретения первый операнд-источник 112 может, при желании, храниться в первом регистре набора, второй операнд-источник 114 может, при желании, храниться во втором регистре набора, третий операнд-источник 116 может, при желании, храниться в третьем регистре набора и операнд-назначение может, при желании, храниться в четвертом регистре набора. В некоторых случаях, регистр, используемый для операнда-назначения, может отличаться от регистров, используемых для первого, второго и третьего операндов-источников. В других случаях, регистр, используемый для одного из операндов-источников, может быть повторно использован для операнда-назначения (например, результат может быть записан поверх одного из операндов-источников). В качестве альтернативы, ячейки памяти или другие ячейки запоминающего устройства могут быть, при желании, использованы для одного или нескольких из указанных операндов.

Обращаясь снова к фиг. 1, блок 106 исполнения связан с блоком 104 декодирования и набором 110 регистров. В некоторых вариантах осуществления изобретения блок исполнения также может быть связан с необязательным регистром 120 маски операции с упакованными данными и/или необязательной маской 122 операции с упакованными данными, как будет дополнительно описано ниже, хотя этого не требуется. Блок исполнения может принимать одну или несколько декодированных, или другим образом преобразованных команд или сигналов управления, которые представляют команду сложения трех источников с плавающей запятой и/или которые получены из указанной команды. Блок исполнения также может принимать первый операнд-источник 112, содержащий, по меньшей мере, первый элемент данных с плавающей запятой, второй операнд-источник 114, содержащий, по меньшей мере, второй элемент данных с плавающей запятой, и третий операнд-источник 116, содержащий, по меньшей мере, третий элемент данных с плавающей запятой. Блок исполнения выполнен с возможностью, в ответ на команду сложения трех источников с плавающей запятой или в результате этой команды (например, в ответ на одну или несколько команд или сигналов управления, декодированных прямо или косвенно (например, с помощью эмуляции) из этой команды), сохранения результата 118 в операнде-назначении, указанном командой. В некоторых вариантах осуществления изобретения результат может содержать, по меньшей мере, результирующий элемент данных с плавающей запятой, который соответствует первому, второму и третьему элементам данных с плавающей запятой. В некоторых вариантах осуществления изобретения результирующий элемент данных с плавающей запятой может содержать, по меньшей мере, первую округленную сумму с плавающей запятой. Первая округленная сумма с плавающей запятой является числом с плавающей запятой, при этом осуществлено надлежащее округление с плавающей запятой. В некоторых вариантах осуществления изобретения первая округленная сумма с плавающей запятой может представлять собой алгебраическую сумму второй округленной суммы с плавающей запятой и третьего элемента данных с плавающей запятой. В некоторых вариантах осуществления изобретения вторая округленная сумма с плавающей запятой может представлять собой алгебраическую сумму первого элемента данных с плавающей запятой и второго элемента данных с плавающей запятой. В некоторых вариантах осуществления изобретения результат может быть любым из показанных и описанных результатов для фиг. 3-6, хотя объем изобретения этим не ограничен.

Для ясности, в настоящем документе термин «алгебраическая сумма» первого значения и второго значения используют для обозначения суммы, которая позволяет брать любое значение из первого и второго значений с обратным знаком. Например, алгебраическая сумма второй округленной суммы с плавающей запятой и третьего элемента данных с плавающей запятой может содержать сумму третьего элемента данных с плавающей запятой и второй округленной суммы с плавающей запятой или сумму второй округленной суммы с плавающей запятой и третьего элемента данных с плавающей запятой с обратным знаком (отрицание). Аналогично, алгебраическая сумма первого и второго элементов данных с плавающей запятой может содержать сумму первого элемента данных с плавающей запятой и второго элемента данных с плавающей запятой, сумму первого элемента данных с плавающей запятой и второго элемента данных с плавающей запятой с обратным знаком, сумму первого элемента данных с плавающей запятой с обратным знаком и второго элемента данных с плавающей запятой с обратным знаком и сумму первого элемента данных с плавающей запятой с обратным знаком и второго элемента данных с плавающей запятой. Как будет подробнее описано ниже, некоторые, но не все, варианты осуществления изобретения могут, при желании, позволять брать любой один, два или все элементы данных с обратным знаком до сложения, хотя этого не требуется (например, другой вариант осуществления изобретения не позволяет брать такое отрицание).

Предпочтительно, что команда сложения трех источников с плавающей запятой может осуществлять два сложения в рамках исполнения одной команды (например, макрокоманды, команды из набора команд и так далее). Обычно требуется две различные команды. Способность осуществлять оба сложения в одной команде может позволить получить определенные преимущества с точки зрения в производительности и/или энергопотребления. Во-первых, оба сложения могут быть осуществления при декодировании одной команды, вместо декодирования двух отдельных команд. Это может помочь увеличить производительность декодирования команды благодаря освобождению области декодирования для другой команды. Это также может помочь уменьшить величину потребления электроэнергии, так как для осуществления двух сложений декодируют на одну команду меньше. Улучшения производительности также могут быть достигнуты путем отказа от записи промежуточной суммы одного из двух сложений в архитектурный регистр и последующего считывания промежуточной суммы из архитектурного регистра с целью осуществления второго сложения. Такие записи и считывания из архитектурного регистра обычно подразумевают дополнительное время или ожидание (например, порядка нескольких тактовых циклов). Это также может помочь избежать связывания архитектурного регистра и помочь уменьшить количество операций переименования регистров. Исключение считываний, записей и операций переименования регистров также может помочь уменьшить потребление электроэнергии. Для определенных процессоров, уменьшение потребления электроэнергии может привести к увеличению производительности, так как определенные процессоры (например, это особенно относится к процессорам, используемым для высокопроизводительных вычислений) могут обладать производительностью, которая имеет тенденцию быть ограниченной доступными границами потребления электроэнергии. Соответственно, уменьшение потребления электроэнергии также может вести к увеличению производительности.

Округление с плавающей запятой может быть использовано тогда, когда точный результат операции с плавающей запятой (например, сложения с плавающей запятой) требует больше цифр, чем присутствует цифр в мантиссе. В некоторых вариантах осуществления изобретения результат может отражать две различные операции округления с плавающей запятой, вместо одной операции округления с плавающей запятой. Более конкретно, первая начальная операция округления с плавающей запятой может быть осуществлена для суммы, подразумевающей первый и второй элементы данных с плавающей запятой с целью выработки первой округленной суммы и далее вторая операция округления с плавающей запятой может быть осуществлена для суммы третьего элемента данных с плавающей запятой и первой округленной суммы. Как будет подробно объяснено ниже, эти две операции округления с плавающей запятой могут отражать микроархитектурную реализацию команды. Например, в некоторых вариантах осуществления изобретения микроархитектура, используемая для реализации команды, может использовать логическую схему, которая не способна одновременно сложить три значения с плавающей запятой. В качестве одного примера, как будет подробно описано ниже, два суммирующих устройства для чисел с плавающей запятой могут быть использованы последовательно и каждое может быть использовано для осуществления одновременного сложения только двух значений с плавающей запятой. Например, в первом суммирующем устройстве может быть получена сумма двух значений с плавающей запятой и далее для суммы может быть осуществлена первая операция округления с плавающей запятой, и далее во втором суммирующем устройстве может быть получена сумма третьего значения с плавающей запятой и округленной суммы, и далее для суммы, поданной на выход второго суммирующего устройства, может быть осуществлена вторая операция округления.

В качестве другого примера, как будет подробно описано ниже, может быть повторно использовано одно суммирующие устройство для чисел с плавающей запятой и во время каждого цикла или прохода суммирующего устройства может быть осуществлено одновременное сложение только двух значений с плавающей запятой. Например, в один проход может быть получена сумму двух значений с плавающей запятой, и далее для этой суммы может быть осуществлена первая операция округления с плавающей запятой, и далее во второй проход может быть получена сумма третьего значения с плавающей запятой и округленной суммы с первого прохода, и далее для суммы, поданной на выход суммирующего устройства во втором проходе, может быть осуществлена вторая операция округления. Как будет подробно описано ниже, преимущества такой микроархитектурной реализации состоят в том, что, например, исключается необходимость в специальной и/или, в общем, большой и сложной логической схеме для осуществления одновременного сложения трех значений с плавающей запятой. Результаты, включающиеся в себя две операции округления с плавающей запятой, могут немного отличаться от случая осуществления одной операции округления с плавающей запятой и это отражает такие микроархитектурные реализации.

В некоторых вариантах осуществления изобретения для обоих округлений может использоваться операция округления или режим округления одного типа. Различные типы операций округления или режимов округления подходят для различных вариантов осуществления изобретения. Примерами подходящих режимов округления являются, помимо прочего, следующие: (1) округление до ближайшего четного; (2) округление в меньшую сторону к отрицательной бесконечности; (3) округление в большую сторону к положительной бесконечности; и (4) округление в сторону нуля с отбрасыванием.

В некоторых вариантах осуществления изобретения команда сложения трех источников с плавающей запятой может поддерживать встроенное управление режимом округления, хотя этого не требуется. Обычно, управление режимом округления, в целом, определено в регистре состояния и управления плавающей запятой (например, MXCSR). Некоторые команды способны обеспечить переопределение округления для каждой команды с помощью полей кодирования в операнде с непосредственным значением. В некоторых вариантах осуществления изобретения управление переопределением режима округления для каждой команды может быть обеспечено с помощью кодирования команды и за рамками непосредственного значения. В качестве примера, в некоторых вариантах осуществления изобретения, управление режимом округления может быть встроено в префикс (например, EVEX префикс) как статичное управление или управление переопределением режима округления для каждой команды. Это может позволить программисту статично применять конкретный режим округления, который может переопределить режим округления в регистре состояния и управления плавающей запятой (например, MXCSR). В некоторых вариантах осуществления изобретения, при желании, может подразумеваться запрещение сообщения обо всех исключениях с плавающей запятой, когда такое управление режимом округления обеспечивают с помощью кодирования команды. Запрещение сообщения об всех исключениях с плавающей запятой может иметь место независимо от любых конкретных битов маски для запрещения или разрешения сообщения о соответствующих исключениях с плавающей запятой в регистре состояния и управления плавающей запятой (например, MXCSR). Запрещение сообщения об этих исключениях с плавающей запятой может означать, что биты или флаги в регистре состояния и управления плавающей запятой (например, MXCSR) могут не обновляться при появлении таких исключений с плавающей запятой (то есть, о них не сообщают).

Возвращаясь снова к фиг. 1, блок 106 исполнения и/или процессор 100 могут содержать конкретную или специфичную логическую схему (например, транзисторы, интегральные схемы или другое аппаратное обеспечение, потенциально объединенное с встроенными программами (например, команды, сохраненные в энергонезависимой памяти) и/или программным обеспечением), которые выполнены с возможностью реализации команды сложения трех источников с плавающей запятой и хранения результата в ответ на команду сложения трех источников с плавающей запятой и/или в результате команды сложения трех источников с плавающей запятой (например, в ответ на одну или несколько команд или сигналов управления, декодированных или другим образом полученных из команды сложения трех источников с плавающей запятой). Блок исполнения может содержать логическую схему 108 сложения с плавающей запятой. В качестве примера блок исполнения и/или логическая схема сложения с плавающей запятой содержат суммирующее устройство для чисел с плавающей запятой, объединенное устройство (FMA) сложения-умножения с плавающей запятой, блок арифметики с плавающей запятой, логический блок арифметики с плавающей запятой или подобные. В некоторых вариантах осуществления изобретения блок исполнения может содержать одну или несколько входных структур (например, порт (порты), соединение (соединения), интерфейс и так далее) для приема операндов-источников, логическую схему или схему сложения с плавающей запятой, связанную с входной структурой (структурами) для приема и обработки операндов-источников и выработки результата, и одну или несколько выходных структур (например, порт (порты), соединение (соединения), интерфейс и так далее), связанных с логической схемой или схемой сложения с плавающей запятой с целью подачи результата на выход. В некоторых вариантах осуществления изобретения блок исполнения может содержать схему или логическую схему, показанную и описанную на каких-либо фиг. из фиг. 7-9, на которых приведены. примеры подходящих микроархитектурных конструкций, хотя объем изобретения этим не ограничен.

Для ясности описания будет показан и описан сравнительно простой процессор 100. В других вариантах осуществления изобретения, при желании, процессор может содержать другие хорошо известные компоненты процессора. Возможные примеры таких компонентов включают в себя, помимо прочего, блок вызова команд, кэш-памяти данных и команд, кэш-памяти второго или более высоких уровней, логическую схему с внеочередным исполнением команд, блок планирования исполнения команд, блок переименования регистров, блок выгрузки, блок интерфейса шины, буферы предыстории преобразования данных и команд, буферы предварительного вызова, очереди микрокоманд, устройства, задающие последовательность микрокоманд, другие компоненты, содержащиеся в процессорах и их различные комбинации. Подходят большое количество разных комбинаций и конфигураций таких компонентов. Варианты осуществления изобретения не ограничены какой-либо известной комбинацией или конфигурацией. Более того, варианты осуществления изобретения могут содержаться в процессорах с несколькими ядрами, логических процессорах или устройствах исполнения, по меньшей мере, один из которых содержит блок декодирования и блок исполнения для реализации варианта осуществления команды сложения трех источников с плавающей запятой.

На фиг. 2 показана схема одного варианта способа 225 реализации варианта осуществления команды сложения трех источников с плавающей запятой. В различных вариантах осуществления изобретения способ может быть выполнен процессором, устройством обработки команд или другим цифровым логическим устройством. В некоторых вариантах осуществления изобретения операции и/или способ с фиг. 2 могут быть выполнены процессором и/или в процессоре с фиг. 1. Компоненты, признаки и конкретные необязательные подробности, описанные в настоящем документе для процессора с фиг. 1, также, при желании, применимы к операциям и/или способу с фиг. 2. В качестве альтернативы операции и/или способ с фиг. 2 могут быть выполнены аналогичным или другим процессором или устройством. Более того, процессор с фиг. 1 может выполнить операции и/или способ, аналогичные, похожие или отличные от операций и/или способа с фиг. 2.

Способ включает в себя в блоке 226 прием команды сложения трех источников с плавающей запятой. В различных аспектах изобретения, команда может быть принята в процессоре, устройстве обработки команд или его участке (например, блоке вызова команд, блоке декодирования, блоке интерфейса шины и так далее). В различных аспектах команда может быть принята от источника, расположенного не на кристалле (например, из памяти, соединения и так далее) или от источника на кристалле (например, из кэш-памяти команд, очереди команд и так далее). Команда сложения трех источников с плавающей запятой может определять или другим образом указывать первый операнд-источник, содержащий, по меньшей мере, первый элемент данных с плавающей запятой, определять или другим образом указывать второй операнд-источник, содержащий, по меньшей мере, второй элемент данных с плавающей запятой, и может определять или другим образом указывать третий операнд-источник, содержащий, по меньшей мере, третий элемент данных с плавающей запятой.

В блоке 227 результат сохраняют в операнде-назначении в ответ на команду сложения трех источников с плавающей запятой и/или в результате команды сложения трех источников с плавающей запятой. Операнд-назначение может быть определен или другим образом указан в команде сложения трех источников с плавающей запятой. Обычно, блок исполнения, устройство обработки команд или процессор могут выполнять команду и сохранять результат. Результат может содержать, по меньшей мере, результирующий элемент данных с плавающей запятой, который должен соответствовать первому, второму и третьему элементам данных с плавающей запятой. Результирующий элемент данных с плавающей запятой может содержать первую округленную сумму с плавающей запятой. В некоторых вариантах осуществления изобретения первая округленная сумма с плавающей запятой может представлять собой алгебраическую сумму второй округленной суммы с плавающей запятой и третьего элемента данных с плавающей запятой. В некоторых вариантах осуществления изобретения вторая округленная сумма с плавающей запятой может представлять собой алгебраическую сумму п