Звено связи многокристальной интегральной схемы

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в облегчении связи между двумя устройствами, потенциально поддерживающими многочисленные различные протоколы. Устройство приема данных содержит логику физического уровня, чтобы принимать данные по одной или более дорожкам для данных физического звена связи; принимать действительный сигнал по другой из дорожек физического звена связи, причем действительный сигнал идентифицирует, что действительные данные следуют за подтверждением действительного сигнала по одной или более дорожкам для данных; и принимать потоковый сигнал по другой из дорожек физического звена связи, причем потоковый сигнал должен идентифицировать тип данных на одной или более дорожках для данных, в котором тип содержит пакетные данные уровня звена связи, которые предназначены для облегчения переключения состояния звена связи для физического звена связи. 3 н. и 20 з.п. ф-лы, 26 ил., 1 табл.

Реферат

Область техники, к которой относится изобретение

Настоящее раскрытие относится к компьютерной системе и, в частности (но не исключительно), к межсоединениям типа "точка-точка".

Уровень техники

Прогресс в области технологии полупроводников и разработки логических схем позволил увеличить количество логических элементов, которые могут присутствовать в устройствах интегральных схем. Как следствие, конфигурации компьютерных систем прошли эволюцию от одиночных или многочисленных интегральных схем в системе до многоядерного, многоцепочечного аппаратурного обеспечения и многочисленных логических процессоров, присутствующих в индивидуальных интегральных схемах, а также других интерфейсов, интегрированных внутри таких процессоров. Процессор или интегральная схема обычно содержит одиночный кристалл физического процессора, где кристалл процессора может содержать множество ядер, цепочек аппаратурного обеспечения, логических процессоров, интерфейсов, памяти, концентраторов контроллеров и т.д.

В результате повышения возможности размещения большей вычислительной мощности в меньших корпусах интегральных схем, возросла популярность малогабаритных компьютерных устройств. Количество смартфонов, планшетов, ультратонких ноутбуков и другого оборудования пользователя возросло экспоненциально. Однако, такие более малогабаритные устройства опираются на серверы как для хранения данных, так и для сложной обработки, которая превышает форм-фактор. Следовательно, спрос на компьютерном рынке на высокопроизводительные устройства (то есть, на серверное пространство) также вырос. Например, в модемных серверах обычно существует не только одиночный процессор с множеством ядер, но также и многочисленные физические процессоры (также упоминаемые как многочисленные сокеты), чтобы повысить вычислительную мощность. Но поскольку вычислительная мощность растет вместе с ростом количества устройств в компьютерной системе, связь между сокетами и другими устройствами становится более критичной.

Фактически, межсоединения выросли из более традиционных многоточечных шин, которые имеют дело прежде всего с электрическими соединениям, чтобы полностью развивать архитектуры межсоединений, облегчающих быстрое соединение. К сожалению, поскольку потребность в будущих процессорах растет с более высокими скоростями, соответствующие потребности накладываются на возможности существующих архитектур межсоединений.

Краткое описание чертежей

Фиг. 1 - вариант осуществления компьютерной системы, содержащей архитектуру межсоединений.

Фиг. 2 - вариант осуществления архитектуры межсоединений, содержащей многоуровневый набор.

Фиг. 3 - вариант осуществления запроса или пакета, который должен формироваться или приниматься в рамках архитектуры межсоединений.

Фиг. 4 - вариант осуществления пары передатчика и приемника для архитектуры межсоединений.

Фиг. 5 - вариант осуществления многокристального корпуса интегральной схемы.

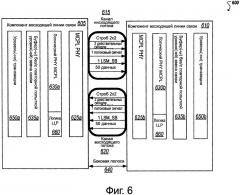

Фиг. 6 - упрощенная блок-схема звена связи многокристального корпуса интегральной схемы (MCPL).

Фиг. 7 - пример сигнализации в примерной MCPL.

Фиг. 8 - упрощенная блок-схема дорожки для передачи данных в примерной MCPL.

Фиг. 9 - упрощенная блок-схема примерных технологий подавления перекрестных помех в варианте осуществления MCPL.

Фиг. 10 - упрощенная схема примерных компонент подавления перекрестных помех в варианте осуществления MCPL.

Фиг. 11 - упрощенная блок-схема MCPL.

Фиг. 12 - упрощенная блок-схема MCPL, взаимодействующей с логикой верхнего уровня по многочисленным протоколам, использующим логический интерфейс PHY (LPIF).

Фиг. 13 - пример сигнализации примерной MCPL в сочетании с восстановлением звена связи.

Фиг. 14А-14С - примерные битовые отображения данных на дорожках примерной MCPL.

Фиг. 15 - участок примерного конечного автомата звена связи.

Фиг. 16 - поток, связанный с примерной центровкой звена связи.

Фиг. 17 - примерный конечный автомат звена связи.

Фиг. 18 - сигнализация для ввода состояния низкого энергопотребления.

Фиг. 19 - вариант осуществления блок-схемы компьютерной системы, содержащей многоядерный процессор.

Фиг. 20 - другой вариант осуществления блок-схемы компьютерной системы, содержащей многоядерный процессор.

Фиг. 21 - вариант осуществления блок-схемы процессора.

Фиг. 22 - другой вариант осуществления блок-схемы компьютерной системы, содержащей процессор.

Фиг. 23 - вариант осуществления блока компьютерной системы, содержащей многочисленные процессоры.

Фиг. 24 - примерная система, реализуемая как система на чипе (SoC).

Схожие ссылочные номера и обозначения на различных чертежах указывают схожие элементы.

Подробное описание

В последующем описании излагаются многочисленные конкретные подробности, такие как примеры конкретных типов процессоров и системных конфигураций, конкретного аппаратурного обеспечения, конкретных архитектурных и микроархитектурных подробностей, конкретных конфигураций регистров, конкретных типов команд, конкретных системных компонент, конкретных результатов измерений/максимумов, конкретных стадий и работы процессорного конвейера и т.д., чтобы обеспечить полное понимание настоящего изобретения. Специалистам в данной области техники должно быть, однако, очевидным, что эти конкретные подробности нет необходимости использовать для практической реализации настоящего изобретения. В других случаях, известные компоненты или способы, такие как конкретные и альтернативные архитектуры процессоров, конкретные логические схемы/управляющие программы для описанных алгоритмов, конкретная встроенная управляющая программа, конкретная взаимосвязанная операция, конкретные логические конфигурации, конкретные производственные технологии и материалы, конкретные реализации компиляторов, конкретное выражение алгоритмов в управляющей программе, конкретные технологии/логика отключения электропитания и стробирования и другие конкретные операционные подробности компьютерной системы не были описаны подробно, чтобы избежать излишнего запутывания настоящего изобретения.

Хотя последующие варианты осуществления могут быть описаны со ссылкой на энергосбережение и эффективность использования энергии в конкретных интегральных схемах, таких как компьютерные платформы или микропроцессоры, к другим типам интегральных схем и логических устройств применимы другие варианты осуществления. Схожие технологии и принципы вариантов осуществления, описанные здесь, могут быть применены к другим типам схем или полупроводниковых устройств, которые также могут извлечь выгоду из улучшенного использования энергии и энергосбережения. Например, раскрытые варианты осуществления не ограничиваются настольными компьютерными системами или Ultrabooks™. Они могут также использоваться в других устройствах, таких как карманные устройства, планшеты, другие тонкие ноутбуки, устройства с системами на чипе (SOC) и встраиваемые применения. К некоторым примерам карманных устройств относятся сотовые телефоны, устройства, работающие по интернет-протоколу, цифровые фотоаппараты, персональные цифровые секретари (PDA) и карманные персональные компьютеры. Встраиваемые применения обычно содержат микроконтроллер, цифровой сигнальный процессор (DSP), систему на чипе, сетевые компьютеры (NetPC), цифровые приемники, сетевые концентраторы, переключатели глобальной сети (WAN) или любую другую систему, способную выполнять представленные ниже функции и операции. Кроме того, описанные здесь устройство, способы, и системы не ограничивается физическими компьютерными устройствами, а могут также относиться к оптимизации программного обеспечения для энергосбережения и эффективности использования электропитания. Как станет совершенно очевидным в приведенном ниже описании, описанные здесь варианты осуществления способов, устройств и систем (неважно, со ссылкой на аппаратурные средства, встроенное программное обеспечение, программное обеспечение или их комбинации), являются жизненно важными для будущей "зеленой технологии", сбалансированной с требуемыми рабочими характеристиками.

По мере прогресса компьютерных систем, содержащиеся в них компоненты становятся все более сложными. В результате сложность архитектуры межсоединений и связей между компонентами также возрастает, чтобы обеспечить удовлетворение требований к ширине полосы для оптимальной работы составляющих компонент. Дополнительно, различные сегменты рынка требуют различных вариантов архитектур межсоединений для удовлетворения потребностей рынка. Например, серверы требуют более высокопроизводительных рабочих характеристик, тогда как мобильная экосистема иногда способна пожертвовать общей производительностью в целях экономии электропитания. К тому же, единственной целью большинства связных структур является обеспечение максимально возможных рабочих характеристик при максимальной экономии потребляемой мощности. Ниже обсуждается множество межсоединений, которые потенциально могут извлечь выгоду из описанных здесь вариантов изобретения.

Одна из связных архитектур межсоединений содержит экспресс-архитектуру межсоединений периферийных компонент (Peripheral Component Interconnect (PCI) Express (PCIe)). Первичная цель PCIe состоит в том, чтобы позволить компонентам и устройствам, получаемым от различных поставщиков, взаимодействовать в открытой архитектуре, перекрывая многочисленные сегменты рынка: клиенты (настольные и мобильные компьютеры), серверы (стандартные и внутренние предприятий) и встроенные устройства и устройства связи. PCI Express является высокопроизводительным межсоединением ввода-вывода общего назначения, предназначенным для широкого разнообразия будущих компьютерных и связных платформ. Некоторые атрибуты PCI, такие как модель использования, архитектура загрузки и хранения и интерфейсы программного обеспечения поддерживались во всех версиях, хотя предшествующие реализации с параллельной шиной были заменены хорошо масштабируемым, полностью последовательным интерфейсом. Более свежие версии PCI Express обладают преимуществом перспективы для соединений "точка-точка", технологии на основе переключений и пакетированного протокола, чтобы предоставить новые уровни рабочих характеристик и функций. Управление электропитанием, Power Management (управление электропитанием), Quality Of Service (QoS) (качество обслуживания), поддержка Hot-Plug/Hot-Swap ("горячего" подключения/"горячей" замены), Data Integrity (целостность данных) и Error Handling (обработка ошибок) являются лишь некоторыми из перспективных функций, поддерживаемых PCI Express.

На фиг. 1 показан вариант осуществления связной структуры, состоящей из звеньев связи "точка-точка", которые связывают между собой набор компонент. Система 100 содержит процессор 105 и системную память 110, связанные с концентратором 115 контроллера. Процессор 105 содержит любой элемент обработки, такой как микропроцессор, ведущий процессор, встроенный процессор, сопроцессор или другой процессор. Процессор 105 соединяется с концентратором 115 контроллера через шину внешнего интерфейса (FSB) 106. В одном из вариантов осуществления FSB 106 является последовательным межсоединением "точка-точка", как описано ниже. В другом варианте осуществления, линия 106 звена связи содержит архитектуру последовательных дифференциальных межсоединений, совместимую с различными стандартами межсоединений.

Системная память 110 содержит любое устройство памяти, такое как оперативная память (RAM), энергонезависимая память (NV) или другая память, доступная устройствам в системе 100. Системная память 110 соединяется с концентратором 115 контроллера через интерфейс 116 памяти. Примерами интерфейса памяти являются интерфейс памяти с двойной скоростью передачи данных (DDR), двухканальный интерфейс памяти DDR и интерфейс динамической памяти RAM (DRAM).

В одном из вариантов осуществления концентратор 115 контроллера является корневым концентратором, корневым комплексом или корневым контроллером в иерархии межсоединений для экспресс-межсоединений периферийных компонент (PCIe или PCIE). Примерами концентратора 115 контроллера являются чипсет, концентратор контроллера памяти (МСН), северный мост, концентратор контроллера межсоединений (ICH), южный мост и корневой контроллер/концентратор. Часто термин "чипсет" относится к двум физически раздельным концентраторам контроллеров, то есть, к концентратору контроллера памяти (МСН), связанному с концентратором контроллера межсоединений (ICH). Заметим, что существующие системы часто содержат МСН, интегрированный с процессором 105, тогда как контроллер 115 должен осуществлять связь с устройствами ввода-вывода способом, подобным описанному ниже. В некоторых вариантах осуществления, как вариант, дополнительно поддерживается одноранговая маршрутизация через корневой комплекс 115.

Здесь концентратор 115 контроллера связывается с переключателем/мостом 120 через последовательное звено 119 связи. Модули 117 и 121 ввода-вывода, которые могут также упоминаться как интерфейсы/порты 117 и 121, содержат/осуществляют стек многоуровневого протокола, чтобы обеспечивать передачу между концентратором контроллера 115 и переключателем 120. В одном из вариантов осуществления с переключателем 120 способны связываться многочисленные устройства.

Переключатель/мост 120 маршрутизирует пакеты/сообщения от устройства 125 по восходящий линии, то есть, вверх по иерархии в направлении корневого комплекса к концентратору 115 контроллера, и по нисходящей линии, то есть, вниз по иерархии в направлении от корневого контроллера корня, от процессора 105 или системной памяти 110 к устройству 125. Выключатель 120 в одном из вариантов осуществления относится к логической сборке многочисленных виртуальных устройств мостов типа "от PCI к PCI". Устройство 125 содержит любое внутреннее или внешнее устройство или компонент, которые должны связываться с электронной системой, такой как устройство ввода-вывода, контроллер сетевого интерфейса (NIC), расширительная плата, аудиопроцессор, сетевой процессор, жесткий диск, запоминающее устройство, ROM на CD/DVD, монитор, принтер, "мышь", клавиатура, маршрутизатор, мобильное запоминающее устройство, устройство Firewire, устройство универсальной последовательной шины (USB), сканер и другие устройства ввода-вывода. Часто на жаргоне PCIe устройство упоминается как конечная точка. Хотя это специально не показано, устройство 125 может содержать PCIe к мосту PCI/PCI-X, чтобы поддерживать устройства PCI действующей или другой версии. Устройства конечной точки в PCIe часто классифицируются как действующие, PCIe или интегрированные конечные точки корневого комплекса.

Графический ускоритель 130 также связывается с концентратором 115 контроллера через последовательную линию 132 связи. В одном из вариантов осуществления графический ускоритель 130 связывается с МСН, который связывается с ICH. Переключатель 120 и, соответственно, устройство 125 ввода-вывода затем связывается с ICH. Модули 131 и 118 ввода-вывода должны также реализовывать стек многоуровневого протокола, чтобы осуществлять связь между графическим ускорителем 130 и концентратором 115 контроллера. Подобно МСН, обсуждавшемуся выше, графический контроллер или графический ускоритель 130 сам по себе может интегрироваться в процессор 105.

На фиг. 2 показан вариант осуществления стека многоуровневого протокола. Стек 200 многоуровневого протокола содержит любую форму стека многоуровневой связи, такую как стек Quick Path Interconnect (QPI), стек PCIe, стек высокопроизводительных компьютерных межсоединений или другой многоуровневый стек. Хотя обсуждение далее на фиг. 1-4 делает ссылку только на стек PCIe, те же самые концепции могут быть применены к другим стекам межсоединений. В одном из вариантов осуществления стек 200 является стеком протокола PCIe, содержащим уровень 205 транзакции, уровень 210 звена связи для передачи данных и физический уровень 220. Интерфейс, такой как интерфейс 117, 118, 121, 122, 126 и 131 на фиг. 1, может быть представлен как стек 200 протокола связи. Представление в виде стека протокола связи может также упоминаться как модуль или интерфейс, осуществляющий/содержащий стек протокола.

PCI Express использует пакеты для передачи информации между компонентами. Пакеты формируются на уровне 205 транзакции и на уровне 210 звена передачи данных, чтобы переносить информацию от передающего компонента к приемному компоненту. По мере того, как переданные пакеты проходят через другие уровни, они обогащаются дополнительной информацией, необходимой для обработки пакетов на этих уровнях. На приемной стороне происходит обратный процесс и пакеты получают преобразованными из их представления на физическом уровне 220 в представление на уровне звена 210 связи для передачи данных и, окончательно, (для пакетов уровня транзакции) в форму, которая может обрабатываться на уровне 205 транзакции приемного устройства.

Уровень транзакции

В одном из вариантов осуществления уровень 205 транзакции должен обеспечивать интерфейс между ядром обработки устройства и межсоединительной архитектурой, такой как уровень 210 звена связи для передачи данных и физический уровень 220. В этом отношении первичная ответственность уровня 205 транзакции заключается в сборке и разборке пакетов (то есть, пакетов уровня транзакции или TLP). Уровень 205 трансляции обычно руководит управлением потока кредит-база для TLP. PCIe осуществляет транзакции с разделением, то есть, транзакции с запросом и ответом, разделенными во времени, позволяя звену связи в то время, когда целевое устройство собирает данные для ответа, передавать другой трафик.

Кроме того, PCIe использует управлением потоком кредит-база. В этой схеме устройство рекламирует начальный объем кредита для каждого из приемных буферов на уровне 205 транзакции. Внешнее устройство на противоположном конце линии связи, такое как концентратор 115 контроллера, показанный на фиг. 1, подсчитывает количество кредитов, использованных каждым TLP. Транзакция может передаваться, если транзакция не превышает кредитный лимит. После получения ответа объем кредита восстанавливается. Преимущество кредитной схемы состоит в том, что время ожидания возврата кредита не влияет на рабочие характеристики при условии, что не возникает кредитный лимит.

В одном из вариантов осуществления четыре адресных пространства транзакции содержат адресное пространство конфигурации, адресное пространство памяти, адресное пространство ввода/вывода и адресное пространство сообщения. Транзакции пространства памяти содержат один или более запросов считывания и запросов записи, чтобы передавать данные в местоположение отображенной памяти и от него. В одном из вариантов осуществления транзакции пространства памяти способны использовать два различных адресных формата, например, формат короткого адреса, такой как 32-разрядный адрес, или формат длинного адреса, такой как 64-разрядный адрес. Транзакции пространства конфигурации используются для доступа к пространству конфигурации устройств PCIe. Транзакции в пространстве конфигурации содержат запросы считывания и запросы записи. Транзакции пространства сообщения (или, просто сообщения) определяются для поддержки внутриполосной передачи между средствами PCIe.

Поэтому в одном из вариантов осуществления, уровень 205 транзакции собирает заголовок/полезную нагрузку пакета 206. Формат для текущего заголовка/полезной нагрузки пакета может быть найден в технических требованиях PCIe на веб-сайте технических требований PCIe.

Сразу обращаемся к фиг. 3, где показан вариант осуществления дескриптора транзакции PCIe. В одном из вариантов осуществления дескриптор 300 транзакции является механизмом переноса информацию о транзакции. В этом отношении дескриптор 300 транзакции поддерживает идентификацию транзакции в системе. Другое потенциальное использование содержит модификации слежения за упорядочиванием транзакции по умолчанию и ассоциации транзакции с каналами.

Дескриптор 300 транзакции содержит поле 302 глобального идентификатора, поле 304 атрибутов и поле 306 идентификатора. В показанном примере поле 302 глобального идентификатора изображается содержащим локальное поле 308 идентификатора транзакции и поле 310 идентификатора источника. В одном из вариантов осуществления глобальный идентификатор 302 транзакции является уникальным для всех исходящих запросов.

В соответствии с одной из реализаций, локальное поле 308 идентификатора транзакции является полем, формируемым средством запроса, и оно уникально для всех исходящих запросов, которые требуют завершения для данного запрашивающего средства. Дополнительно, в этом примере, идентификатор 310 источника однозначно идентифицирует средство запросчика внутри иерархии PCIe. Соответственно, вместе с ID 310 источника локальное поле 308 идентификатора транзакции обеспечивает глобальную идентификацию транзакции внутри области иерархии.

Поле 304 атрибутов определяет характеристики и зависимости транзакции. В этом отношении, поле 304 атрибутов потенциально используется для предоставления дополнительной информации, позволяющей модификацию обработки транзакции по умолчанию. В одном из вариантов осуществления поле 304 атрибутов содержит поле 312 приоритетов, зарезервированное поле 314, поле 316 упорядочивания и поле 318 отсутствия перехвата. Здесь субполе 312 приоритета может быть модифицировано инициатором, чтобы назначить приоритет транзакции. Зарезервированное поле 314 атрибутов оставляется зарезервированным на будущее или используется согласно назначению поставщиком. Возможные модели использования, использующие приоритет или атрибуты безопасности, могут реализовываться, используя резервное поле атрибутов.

В этом примере поле 316 атрибутов упорядочивания используется для предоставления дополнительной информации, транспортирующей тип упорядочивания, который может модифицировать правила упорядочивания, действующие по умолчанию. Согласно одной примерной реализации, атрибут "0" упорядочивания обозначает, что должны применяться правила упорядочивания по умолчанию, а атрибут "1" упорядочивания обозначает упрощенное упорядочивание, при котором записи могут пропускаться в одном и том же направлении, а завершения считывания могут пропускать записи в том же самом направлении. Поле 318 атрибута перехвата используется для определения, перехватываются ли транзакции. Как показано на чертеже, поле 306 идентификатора канала идентифицирует канал, с которым связывается транзакция.

Уровень линии связи

Уровень 210 звена связи, также упоминаемый как уровень 210 связи для передачи данных, действует как промежуточный этап между уровнем 205 транзакции и физическим уровнем 220. В одном варианте осуществления ответственность уровня 210 звена связи для передачи данных обеспечивает достоверный механизм для обмена пакетами уровня транзакции (TLP) между двумя компонентами линии связи. Одна сторона уровня 210 звена связи для передачи данных принимает TLP, собранные уровнем 205 транзакции, применяет идентификатор 211 последовательности пакетов, то есть, количество идентификаций или количество пакетов, вычисляет и применяет код обнаружения ошибки, то есть, CRC 212, и представляет модифицированные TLP на физический уровень 220 для передачи через физический уровень на внешнее устройство.

Физический уровень

В одном из вариантов осуществления физический уровень 220 содержит логический субблок 221 и электрический субблок 222, чтобы физически передавать пакет внешнему устройству. Здесь логический субблок 221 ответственен за "цифровые" функции физического уровня 221. В этом отношении, логический субблок содержит секцию передачи для подготовки исходящей информации к передаче физическим субблоком 222 и секцию приемника для идентификации и подготовки принятой информации перед пропусканием ее на уровень 210 звена связи.

Физический блок 222 содержит передатчик и приемник. Передатчик снабжен логическим субблоком 221 с символами, которые передатчик переводит в последовательную форму и передает внешнему устройству. На приемник от внешнего устройства подаются переведенные в последовательную форму символы и приемник преобразует принятые сигналы в битовый поток. Битовый поток переводится обратно из последовательной формы в параллельную и подается на логический субблок 221. В одном из вариантов осуществления используется код передачи 8b/10b, где передаются/принимаются десятиразрядные символы. Здесь, специальные символы используются, чтобы кадрировать пакет с получением кадров 223. Кроме того, в одном из примеров, приемник также обеспечивает тактовые сигналы символов, восстанавливаемые из входящего последовательного потока.

Как указано выше, хотя уровень 205 транзакции, уровень 210 звена связи и физический уровень 220 обсуждаются со ссылкой на конкретный вариант осуществления стека протокола PCIe, стек многоуровневого протокола этим не ограничивается. Фактически, может присутствовать/осуществляться любой многоуровневый протокол. Как пример, порт/интерфейс, который представляется в качестве многоуровневого протокола, содержит: (1) первый уровень, на котором собираются пакеты, то есть, уровень транзакции; второй уровень, на котором устанавливается последовательная форма пакетов, то есть, звена связи; и третий уровень для передачи пакетов, то есть, физический уровень. В качестве конкретного примера, используется многоуровневый протокол интерфейса по общепринятому стандарту (common standard interface, CSI).

Далее на фиг. 4 показан вариант осуществления последовательной связной структуры PCIe типа "точка-точка". Хотя на чертеже показан вариант осуществления последовательной линии связи PCIe типа "точка-точка", последовательное звено связи типа "точка-точка" этим не ограничивается, поскольку оно содержит любой путь передачи сигнала для передачи последовательных данных. В показанном варианте осуществления основное звено связи PCIe содержит две низковольтные, дифференцированно запускаемые сигнальные пары: передающая пара 406/411 и приемная пара 412/407. Соответственно, устройство 405 содержит передающую логику 406 для передачи данных на устройство 410 и приемную логику 407 для приема данных от устройства 410. Другими словами, в звене связи PCIe содержатся два пути передачи, то есть, пути 416 и 417, и два пути приема, то есть, пути 418 и 419.

Термин "путь передачи" относится к любому пути передачи данных, такому как линия передачи, медная линия, оптическая линия, канал беспроводной связи, линия инфракрасной связи или другой канал связи. Соединение между двумя устройствами, такими как устройство 405 и устройство 410, упоминается как звено связи, такое как звено 415 связи. Звено связи может поддерживать одну дорожку - каждая дорожка представляет набор дифференциальных сигнальных пар (одна пара для передачи, одна пара для приема). Чтобы определить ширину полосы пропускания, звено связи может объединять множество дорожек, обозначенные как xN, где N - любая поддерживаемая ширина звена связи, такая как 1, 2, 4, 8, 12, 16, 32, 64 или шире.

Термин "дифференциальная пара" относится к двум путям передачи, таким как линии 416 и 417, для передачи дифференциальных сигналов. Как пример, когда линия 416 переключается с низковольтного уровня на высоковольтный уровень, то есть, формируется нарастающий фронт, линия 417 переключается с высокого логического уровня на низкий логический уровень, то есть, формируется ниспадающий фронт. Дифференциальные сигналы потенциально демонстрируют лучшие электрические характеристики, такие как лучшая целостность сигнала, то есть, перекрестная связь, положительный/отрицательный выброс напряжения, звон и т.д. Это позволяет получить лучшее временное окно, дающее возможность более высоких частот передачи.

На фиг. 5 показана упрощенная блок-схема 500 примерной многокристальной интегральной схемы 505, содержащей два или более чипов или кристаллов, (например, 510, 515) соединенных для осуществления связи, используя примерное звено 520 связи многокристальной интегральной схемы (MCPL). Хотя на фиг. 5 показан пример из двух (или более) кристаллов, которые соединяются, используя примерную MCPL 520, следует понимать, что принципы и функции, описанные здесь в отношении реализаций MCPL, могут применяться среди потенциально возможных других примеров к любому межсоединению или звену связи, соединяющим кристалл (например, 510) и другие компоненты, содержащие два или более кристаллов (например, 510, 515), соединяя кристалл (или чип) с другим, находящимся вне кристалла компонентом, соединяя кристалл с другим устройством или находящимся вне корпуса интегральной схемы кристаллом (например, 505), соединяя кристалл с корпусом BGA интегральной схемы реализуя временное соединение на керамической подложке (POINT),.

Обычно, многокристальная интегральная схема (например, 505) может быть электронной интегральной схемой, где многочисленные интегральные схемы (IC), полупроводниковые кристаллы или другие дискретные компоненты (например, 510, 515) помещены на объединяющую подложку (например, кремниевую или другую полупроводниковую подложку), облегчая использование объединенных компонент в качестве единого компонента (например, как бы большей интегральной схемы). В некоторых случаях крупные компоненты (например, кристаллы 510, 515) сами могут быть системными интегральными схемами, такими как системы на чипе (SoC), многопроцессорные чипы или другие компоненты, которые содержат многочисленные компоненты (например, 525-530 и 540-545) на устройстве, например, на едином кристалле (например, 510, 515). Многокристальные интегральные схемы 505 могут обеспечивать гибкость при построении сложных и изменяемых систем из потенциально возможных многочисленных дискретных компонент и систем. Например, из числа множества примеров, каждый из кристаллов 510, 515 может изготавливаться или как-либо иначе поставляться двумя различными предприятиями, а кремниевая подложка 505 интегральной схемы может обеспечиваться третьим предприятием. Дополнительно, кристаллы и другие компоненты внутри многокристальной интегральной схемы 505 сами могут содержать межсоединение или другие связные структуры (например, 535, 550), обеспечивая инфраструктуру для связи между компонентами (например, 525-530 и 540-545) внутри устройства (например, 510, 515, соответственно). Различные компоненты и межсоединения (например, 535, 550) могут потенциально поддерживать или использовать многие различные протоколы. Дополнительно, связь между кристаллами (например, 510, 515) потенциально может содержать транзакции между различными компонентами на кристаллах по многочисленным различным протоколам. Разработка механизмов обеспечения связи между чипами (или кристаллами) многокристальной интегральной схемы может быть многообещающей, когда традиционные решения, использующие узкоспециализированные, дорогостоящие и специализированные для интегральной схемы решения, основанные на конкретных сочетаниях компонент (и требуемых транзакциях), целесообразны для взаимных соединений.

Примеры, системы, алгоритмы, устройства, логика и функции, описанные в рамках настоящих технических требований могут решать, по меньшей мере, некоторые из идентифицированных выше проблем, потенциально включая и многие другие, неявно упомянутые здесь. Например, в некоторых реализациях могут обеспечиваться широкая полоса пропускания, низкая мощность, интерфейс с малой задержкой, чтобы соединять ведущее устройство (например, центральный процессор) или другое устройство с сопутствующим чипом, который находится в той же самой интегральной схеме, что и ведущее устройство. Такое звено связи многокристальной интегральной схемы (MCPL) может поддерживать многочисленные варианты корпуса интегральной схемы, многочисленные протоколы ввода-вывода, а также характеристики надежности, доступности и удобства обслуживания (RAS). Дополнительно, физический уровень (PHY) может содержать электрический уровень и логический уровень и может поддерживать более протяженные длины каналов, в том числе, длины канала до приблизительно 45 мм, а в некоторых случаях и более. В некоторых реализациях примерная MCPL может работать на высоких скоростях передачи данных, в том числе, на скоростях, превышающих 8-10 Гб/с.

В одной из примерных реализаций MCPL электрический уровень PHY может улучшать традиционные решения многоканальных межсоединений (например, многоканальный ввод-вывод DRAM), увеличивая скорость передачи данных и конфигурацию канала, например, посредством многочисленных функций, таких как, например, среди прочих потенциально возможных примеров, регулируемое окончание промежуточного канала, активное подавление маломощных перекрестных помех, схемная избыточность, коррекция и выравнивание рабочего цикла на каждый бит, линейное кодирование и выравнивание передатчиков.

В одной из примерных реализаций MCPL может быть осуществлен логический уровень PHY, который может дополнительно помочь (например, функции электрического уровня) в повышении скорости передачи данных и расширении конфигурации канала, в то же время также позволяя межсоединение для маршрутизации многочисленных протоколов через электрический уровень. Такие реализации могут обеспечивать и определять модульный общий физический уровень, который является протокольно агностическим и спроектирован для работы с потенциально любым существующим или будущим протоколом межсоединений.

На фиг. 6 представлена упрощенная блок-схема 600, показывающая, по меньшей мере, часть системы, содержащую примерную реализацию звена связи многокристальной интегральной схемы (MCPL). MCPL может быть осуществлена, используя физические электрические соединения (например, провода, реализуемые как дорожки), соединяющие первое устройство 605 (например, первый кристалл, содержащий один или более субкомпонент) со вторым устройством 610 (например, вторым кристаллом, содержащим один или более других субкомпонент). В конкретном примере, показанном на высокоуровневом представлении схемы 600, все сигналы (в каналах 615, 620) могут быть однонаправленными и дорожки могут обеспечиваться для сигналов данных, чтобы иметь как восходящую, так и нисходящую передачу данных. Хотя блок-схема 600 на фиг. 6 относится к первому компоненту 605 как к восходящему компоненту, а ко второму компоненту 610 как к нисходящему компоненту, и физические дорожки MCPL используются при передаче данных в качестве нисходящего канала 615 и используются при приеме данных (от узла 610) в качестве восходящего канала 620, следует понимать, что MCPL между устройствами 605, 610 может использоваться каждым из устройств, чтобы передавать и принимать данные между устройствами.

В одной из примерных реализаций MCPL может обеспечивать физический уровень (PHY), содержащий электрический PHY 625а, b (или, все вместе, 625) MCPL и исполняемую логику, осуществляющую логический PHY 630а, b (или, все вместе, 630) MCPL. Электрический, или физический PHY 625 может обеспечивать физическое соединение, через которое передаются данные между устройствами 605, 610. Компоненты и логика формирования сигнала могут быть осуществлены в сочетании с физическим уровнем PHY 625, чтобы установить для звена связи возможности передачи данных с высокой скоростью и конфигурации канала, которые в некоторых приложениях могут содержать плотно сгруппированные физические соединения на длинах приблизительно 45 мм или более. Логический PHY 630 может содержать логику для облегчения синхронизации, управления состоянием звена связи (например, для уровней 635а, 635b звена связи) и мультиплексирования протокола между потенциально многочисленными различными протоколами, используемые для связи по MCPL.

В одной из примерных реализаций физический PHY 625 может содержать для каждого канала (например, 615, 620) набор дорожек для передачи данных, по которым могут передаваться данные внутри полосы. В этом конкретном примере в каждом восходящем и нисходящем каналах 615, 620 обеспечиваются 50 дорожек для данных, хотя может использоваться и любое другое количество дорожек, разрешенное ограничениями по расположению и энергетике, требуемыми приложениями, ограничениями на устройство и т.д. Каждый канал может дополнительно содержать одну или более выделенных дорожек для строб-сигнала или синхронизации, канального сигнала, одну или более выделенных дорожек для действительного сигнала для канала, одну или более выделенн