Устройство поиска информации

Иллюстрации

Показать всеИзобретение относится к области электросвязи и может быть использовано для поиска и оперативной идентификации информации в сетях передачи данных с коммутацией пакетов и в информационно-справочных (поисковых) системах. Техническим результатом является повышение достоверности определения типа ожидаемых блоков двоичной информации. Устройство поиска информации содержит N≥2 блоков хранения маски, N блоков селекции, делитель частоты, формирователь временных интервалов, регистр стратегии поиска, блок формирования адреса маски переходов, блок индикации, N селекционных контроллеров времени поиска, главный контроллер времени поиска, генератор тактовых импульсов, блок проверки сценария поиска, блок коррекции сценария поиска. 2 з.п. ф-лы, 13 ил.

Реферат

Изобретение относится к области электросвязи и может быть использовано для поиска и оперативной идентификации информации в сетях передачи данных с коммутацией пакетов и в информационно-справочных (поисковых) системах.

Известно устройство по Патенту РФ №РФ №2115952 «Устройство поиска информации» МПК G06F 17/40, опубликованное 20.07.98 и включающее регистры границ, суммирующие и вычитающие счетчики, схемы сравнения, блоки памяти и блоки вычисления. Этот аналог в ходе приема цифрового сообщения и поиска определенной цифровой последовательности позволяет определить параметры и соответствие последовательности передачи правилам обмена данными, установленным для данного протокола.

Недостатком данного устройства является относительно большое время, необходимое для идентификации пакетов (так как идентификация осуществляется путем последовательного анализа значений признаков) и узкая область применения - только для анализа протокола TFTP на предмет соответствия наблюдаемой последовательности пакетов правилам, установленным для данного протокола. Все это ограничивает применение устройства-аналога для анализа протоколов в современных высокоскоростных вычислительных сетях.

Известно устройство по Патенту РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, опубликованное 20.12.2007 г., Бюл. №35. Это устройство содержит N≥2 блоков хранения маски, N блоков селекции, делитель частоты, формирователь временных интервалов, регистр стратегии поиска, блок формирования адреса маски переходов и блок индикации. Устройство обеспечивает расширение области применения и быстродействие анализа входящих пакетов устройства-прототипа за счет идентификации пакетов путем параллельного анализа значений признаков идентификации и контроля последовательности обмена ими на предмет соответствия любым, априорно заданным правилам.

Однако данное устройство имеет недостаток - относительно низкую вероятность своевременного поиска информации в условиях непрерывной динамики смены состояний разноприоритетных запросов на поиск информации и с учетом влияющих факторов.

Из известных наиболее близким аналогом (прототипом) по своей технической сущности заявленному устройству является устройство по Патенту РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16.

Устройство-прототип включает N≥2 блоков хранения маски, N блоков селекции, делитель частоты, формирователь временных интервалов, регистр стратегии поиска, блок формирования адреса маски переходов, блок индикации, N селекционных контроллеров времени поиска, главный контроллер времени поиска и генератор тактовых импульсов.

В устройстве-прототипе тактовый вход делителя частоты является первым тактовым входом устройства, а выход делителя частоты соединен с тактовым входом формирователя временных интервалов, при этом K-разрядный, где К=(log2 N)+1, выход «Код события» блока формирования адреса маски переходов подключен к K-разрядным входам «Код события» регистра стратегии поиска и блока индикации соответственно, входы разрешения записи N блоков хранения маски объединены и являются входом разрешения записи устройства, L-разрядные информационные входы, где L≥2, N блоков селекции объединены и являются L-разрядным информационным входом устройства. Первые L-разрядные входы «Маска 1» и «Маска 2» N блоков хранения маски, являются первыми L-разрядными входами соответственно «Маска 1» и «Маска 2» устройства, вторые L-разрядные выходы «Маска 1» и «Маска 2» N блоков хранения маски подключены к вторым L-разрядным входам «Маска 1» и «Маска 2» соответствующих блоков селекции, вход «Начальный сброс» формирователя временных интервалов соединен с входом «Начальный сброс» блока формирования адреса маски переходов и является входом «Начальный сброс» устройства, при этом, М-разрядный вход «Код времени ожидания» формирователя временных интервалов, где М≥2 - разрядность кода времени ожидания, является М-разрядным входом «Код времени ожидания» устройства, а выход формирователя временных интервалов соединен с входом «Сброс» блока формирования адреса маски переходов, сигнальный выход регистра стратегии поиска соединен с сигнальными входами формирователя временных интервалов и блока формирования адреса маски переходов, K-разрядный адресный вход, управляющий вход, N-разрядный информационный вход и разрешающий вход регистра стратегии поиска являются соответственно K-разрядным адресным входом, управляющим входом, N-разрядным информационным входом и разрешающим входом устройства, входы «Выбор кристалла» и «Чтение/запись» регистра стратегии поиска являются соответственно входами «Выбор кристалла» и «Чтение/запись» устройства, N-разрядный вход «Правило завершения поиска» и выход «Результат поиска» блока индикации являются соответственно N-разрядным входом «Правило завершения поиска» и выходом «Результат поиска» устройства. При этом выход «Результат сравнения» n-го блока селекции, где n=1, 2, …, N, соединен с входом «Результат сравнения» n-го селекционного контроллера времени поиска, выход «Результат сравнения» которого соединен с n-м входом «Результат сравнения» регистра стратегии поиска и с n-м входом «Результат сравнения» блока формирования адреса маски переходов, выход генератора тактовых импульсов подключен к тактовому входу n-ого блока селекции, вход «Обнуление» которого является n-м входом «Обнуление» устройства, причем S-разрядный корректирующий вход, где S≥2 - разрядность корректирующего кода времени поиска, n-ого блока селекции объединен с S-разрядным проверочным входом n-ого селекционного контроллера времени поиска и подключен к n-ому S-разрядному выходу главного контроллера времени поиска, N S-разрядных входов которого являются соответствующими N S-разрядными входами «Коррекция максимального времени поиска» устройства.

Такая схема, по сравнению с устройствами-аналогами, позволяет повысить вероятность своевременного поиска информации в условиях непрерывной динамики смены состояний поисковых запросов и с учетом влияющих факторов, за счет дешифровки, динамической коррекции и синхронизации значений (границ) максимального времени поиска для каждого конкретного сценария (поискового запроса).

Однако прототип имеет недостаток - относительно низкую достоверность определения типа ожидаемых блоков двоичной информации (БДИ), в условиях, характерных для поисковых процессов, протекающих в реальных системах, когда параметры сценария поиска (значения признаков идентификации (битовых масок) и порядок их следования), могут носить недостоверный (недостаточный, неполный и противоречивый) характер.

Данное устройство позволяет реализовывать поисковые запросы с учетом динамики управляющих воздействий и внешних факторов, с учетом изменяющихся во времени текущих требований абонентов к своевременности поиска информации, в то время как при поиске информации в реальных системах, широкое применение находят нейросетевые модели [1-6], объективно основанные на недостоверно (недостаточно, неполно и противоречиво) заданных значениях параметров сценария поиска, где значения признаков идентификации (битовых масок) и порядок их следования, определяющие тип БДИ, носят недостаточный (неполный и противоречивый) характер, традиционно описываемый с привлечением математики искусственных нейронных сетей.

Под «поиском» понимается параллельный анализ значений признаков идентификации БДИ и контроль порядка их следования на предмет соответствия заданным правилам - определение кода типа БДИ.

Под «сценарием поиска» понимается классический метод формальной графики, определяющий заданные правила следования БДИ.

Под «признаком идентификации» понимаются значения битов в соответствующих позициях БДИ.

Под «кодом типа БДИ» понимается код, соответствующий сценарию поиска и, с точки зрения физики процесса, адресу, по которому в оперативном запоминающем устройстве хранится маска переходов, определяющая этот конкретный тип ожидаемых БДИ.

Под «параметрами сценария поиска» понимается набор параметров, описывающих правила следования блоков двоичной информации - набор (множество бит кода) значений признаков идентификации (битовых масок) этих блоков и порядок их следования.

Под «реализацией поисковых запросов» понимается совокупность действий информационно-справочной (поисковой) системы, включающая выборку запроса на поиск информации из очереди, выделение этому запросу ресурса и собственно поиск информации в соответствии с заданным сценарием поиска, а также проведение завершающих операций. Поисковый запрос - посылка сигнала на поиск, инициирующего ответ.

Целью изобретения является разработка устройства, обеспечивающего повышение достоверности определения типа ожидаемых блоков двоичной информации за счет обеспечения возможности поиска информации с учетом верификации (нейроанализа) данных, характеризующих неоднозначно (недостоверно, неполно) заданные значения признаков идентификации (адреса битовых масок) - значения кода типа БДИ, создание устройства поиска информации, способного с высокой достоверностью реализовывать поисковые запросы, характерные для реальных поисковых систем - когда сценарий поиска реализуются в условиях недостаточности (неполноты и противоречивости) данных об истинных значениях параметров поиска.

Указанная цель достигается тем, что в известное устройство поиска информации, содержащее N≥2 блоков хранения маски, N блоков селекции, делитель частоты, формирователь временных интервалов, регистр стратегии поиска, блок формирования адреса маски переходов, блок индикации, N селекционных контроллеров времени поиска, главный контроллер времени поиска и генератор тактовых импульсов, дополнительно включены блок проверки сценария поиска, предназначенный для предварительного анализа данных об истинных значениях кода типа БДИ, и блок коррекции сценария поиска, предназначенный для записи, хранения результатов анализа кода типа БДИ и математически корректной верификации этого кода, идентифицируемого на основе неоднозначного (недостоверного, неполного) сценария, к виду, пригодному для получения однозначных (достоверных) результатов конкретного поиска. При этом тактовый вход делителя частоты является первым тактовым входом устройства, а выход делителя частоты соединен с тактовым входом формирователя временных интервалов, входы разрешения записи N блоков хранения маски объединены и являются входом разрешения записи устройства, L-разрядные информационные входы, где L≥2, N блоков селекции объединены и являются L-разрядным информационным входом устройства. Причем первые L-разрядные входы «Маска 1» и «Маска 2» N блоков хранения маски, являются первыми L-разрядными входами соответственно «Маска 1» и «Маска 2» устройства. Вторые L-разрядные выходы «Маска 1» и «Маска 2» N блоков хранения маски подключены ко вторым L-разрядным входам «Маска 1» и «Маска 2» соответствующих блоков селекции. Вход «Начальный сброс» формирователя временных интервалов соединен с входом «Начальный сброс» блока формирования адреса маски переходов и является входом «Начальный сброс» устройства. При этом, М-разрядный вход «Код времени ожидания» формирователя временных интервалов, где М≥2 - разрядность кода времени ожидания, является М-разрядным входом «Код времени ожидания» устройства, а выход формирователя временных интервалов соединен с входом «Сброс» блока формирования адреса маски переходов, сигнальный выход регистра стратегии поиска соединен с сигнальными входами формирователя временных интервалов и блока формирования адреса маски переходов. Причем K-разрядный адресный вход, где K=(log2 N)+1, управляющий вход, N-разрядный информационный вход и разрешающий вход регистра стратегии поиска являются соответственно K-разрядным адресным входом, управляющим входом, N-разрядным информационным входом и разрешающим входом устройства, входы «Выбор кристалла» и «Чтение/запись» регистра стратегии поиска являются соответственно входами «Выбор кристалла» и «Чтение/запись» устройства, N-разрядный вход «Правило завершения поиска» и выход «Результат поиска» блока индикации являются соответственно N-разрядным входом «Правило завершения поиска» и выходом «Результат поиска» устройства. При этом выход «Результат сравнения» n-го блока селекции, где n=1, 2, …, N, соединен с входом «Результат сравнения» n-го селекционного контроллера времени поиска, выход «Результат сравнения» которого соединен с n-м входом «Результат сравнения» регистра стратегии поиска и с n-м входом «Результат сравнения» блока формирования адреса маски переходов. Выход генератора тактовых импульсов подключен к тактовому входу «n-ого блока селекции, вход «Обнуление» которого является n-м входом «Обнуление» устройства. При этом S-разрядный корректирующий вход, где S≥2 - разрядность корректирующего кода времени поиска, n-ого блока селекции объединен с S-разрядным проверочным входом n-ого селекционного контроллера времени поиска и подключен к n-ому S-разрядному выходу главного контроллера времени поиска, N S-разрядных входов которого являются соответствующими N S-разрядными входами «Коррекция максимального времени поиска» устройства. Причем K-разрядный выход «Код события» блока формирования адреса маски переходов соединен с K-разрядным входом блока проверки сценария поиска, K-разрядный корректировочный выход которого подключен K-разрядному корректировочному входу блока коррекции сценария поиска, контрольный вход которого соединен с контрольным выходом блока проверки сценария поиска. При этом K-разрядный прямой выход блока проверки сценария поиска соединен с K-разрядным прямым выходом блока коррекции сценария поиска и подключен к K-разрядным входам «Код события» регистра стратегии поиска и блока индикации соответственно.

Блок проверки сценария поиска состоит из селектора кода типа БДИ и преобразователя кода типа БДИ, предназначенных соответственно для предварительного анализа (селекции) и регистрации данных, характеризующих значения кода типа БДИ, а также преобразования этих данных из параллельного кода в последовательный. При этом К-разрядный выход преобразователя кода типа БДИ является K-разрядным корректировочным выходом блока проверки сценария поиска, выход передачи преобразователя кода типа БДИ является контрольным выходом блока проверки сценария поиска, разрешающий выход преобразователя кода типа БДИ соединен с инверсным разрешающим входом селектора кода типа БДИ, K-разрядный выход которого является K-разрядным прямым выходом блока проверки сценария поиска. Запрещающий вход преобразователя кода типа БДИ подключен к запрещающему выходу селектора кода типа БДИ, K-разрядный вход которого соединен с K-разрядным входом преобразователя кода типа БДИ и является K-разрядным входом блока проверки сценария поиска.

Блок коррекции сценария поиска состоит из программируемого вычислителя и запоминающего элемента, предназначенных соответственно для преобразования идентифицируемых недостоверно (неполно, противоречиво) значений кода типа БДИ, а также для записи и хранения верифицированных значений этого кода. При этом K-разрядный вход I программируемого вычислителя является K-разрядным корректировочным входом блока коррекции сценария поиска. Вход разрешения выходов А программируемого вычислителя является контрольным входом блока коррекции сценария поиска, К выходов А программируемого вычислителя соединены с соответствующими К входами запоминающего элемента, K-разрядный выход которого является K-разрядным прямым выходом блока коррекции сценария поиска.

Благодаря новой совокупности существенных признаков, за счет введения блока проверки сценария поиска, обеспечивающего предварительное выявление (селекцию) неоднозначно (недостоверно, неполно) идентифицируемых значений кода типа БДИ и блока коррекции сценария поиска, обеспечивающего запись, хранение результатов анализа значений кода типа БДИ и математически корректное вычислительное преобразование (распознавание) этих значений с использованием нейроматематических методов, в заявленном устройстве достигается возможность предварительного анализа и верификации кода типа БДИ, обуславливающая повышение достоверности определения типа ожидаемых блоков двоичной информации, и, как следствие, повышение достоверности выполнения поисковых запросов, характерного для реальных поисковых систем - когда сценарий поиска реализуется в условиях недостаточности (неполноты и противоречивости) данных об истинных значениях параметров данного сценария.

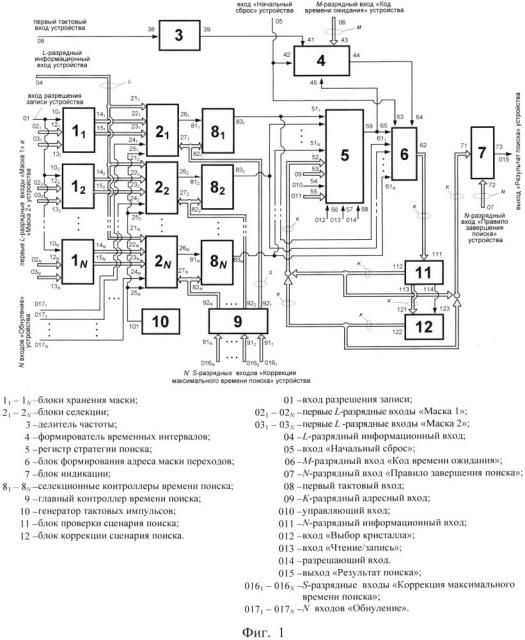

Заявленное устройство поясняется чертежами, на которых представлены:

на фиг. 1 - структурная схема устройства поиска информации;

на фиг. 2 - структурная схема блока проверки сценария поиска;

на фиг. 3 - структурная схема блока коррекции сценария поиска;

на фиг. 4 - структурная схема n-го () блока хранения маски;

на фиг. 5 - структурная схема n-го () блока селекции;

на фиг. 6 - структурная схема формирователя временных интервалов;

на фиг. 7 - структурная схема регистра стратегии поиска;

на фиг. 8 - структурная схема блока формирования адреса маски переходов;

на фиг. 9 - структурная схема блока индикации;

на фиг. 10 - структурная схема n-го () селекционного контроллера времени поиска;

на фиг. 11 - структурная схема главного контроллера времени поиска;

на фиг. 12 - пример сценария поиска;

на фиг. 13 - пример заполнения масок переходов, маски начала сценария и маски окончания сценария.

Устройство (см. фиг. 1) состоит из N, где N≥2, блоков хранения маски 11-1N, N блоков селекции 21-2N, делителя частоты 3, формирователя временных интервалов 4, регистра стратегии поиска 5, блока формирования адреса маски переходов 6, блока индикации 7, N селекционных контроллеров времени поиска 81-8N, главного контроллера времени поиска 9, генератора тактовых импульсов 10, блока проверки сценария поиска 11 и блока коррекции сценария поиска 12.

Элементы соединены между собой следующим образом (см. фиг. 1). Тактовый вход 38 делителя частоты 3 является первым тактовым входом 08 устройства, а выход 39 делителя частоты 3 соединен с тактовым входом 41 формирователя временных интервалов 4. Входы разрешения записи 101-10N N блоков хранения маски 11-1N объединены и являются входом разрешения записи 01 устройства. L-разрядные информационные входы 211-21N, где L≥2, N блоков селекции 21-2N объединены и являются L-разрядным информационным входом 04 устройства. Первые L-разрядные входы «Маска 1» 12n и «Маска 2» 13n n-го блока хранения маски 1n, где n=1, 2, …, N, являются n-ми первыми L-разрядными входами соответственно «Маска 1» 02n и «Маска 2» 03n устройства. Вторые L-разрядные выходы «Маска 1» 14n и «Маска 2» 15n n-го блока хранения маски 1n подключены к соответствующим вторым L-разрядным входам «Маска 1» 22n и «Маска 2» 23n n-го блока селекции 2n. Вход «Начальный сброс» 42 формирователя временных интервалов 4 соединен с входом «Начальный сброс» 63 блока формирования адреса маски переходов 6 и является входом «Начальный сброс» 05 устройства. При этом, М-разрядный вход «Код времени ожидания» 43 формирователя временных интервалов 4, где М≥2 - разрядность кода времени ожидания, является М-разрядным входом «Код времени ожидания» 06 устройства, а выход 44 формирователя временных интервалов 4 соединен с входом «Сброс» 64 блока формирования адреса маски переходов 6. Сигнальный выход 59 регистра стратегии поиска 5 соединен с сигнальными входами 45 и 65 формирователя временных интервалов 4 и блока формирования адреса маски переходов 6 соответственно. K-разрядный, где К=(log2 N)+1, адресный вход 53, управляющий вход 54, N-разрядный информационный вход 55 и разрешающий вход 58 регистра стратегии поиска 5 являются соответственно K-разрядным адресным входом 09, управляющим входом 010, N-разрядным информационным входом 011 и разрешающим входом 014 устройства. Входы «Выбор кристалла» 56 и «Чтение/запись» 57 регистра стратегии поиска 5 являются соответственно входами «Выбор кристалла» 012 и «Чтение/запись» 013 устройства. N-разрядный вход «Правило завершения поиска» 72 и выход «Результат поиска» 73 блока индикации 7 являются соответственно N-разрядным входом «Правило завершения поиска» 07 и выходом «Результат поиска» 015 устройства. Выходы «Результат сравнения» 261-26N блоков селекции 21-2N соединены с соответствующими входами «Результат сравнения» 811-81N соответствующих селекционных контроллеров времени поиска 81-8N, выходы «Результат сравнения» 831-83N которых соединены с соответствующими входами «Результат сравнения» 511-51N регистра стратегии поиска 5 и с соответствующими входами «Результат сравнения» 611-61N блока формирования адреса маски переходов 6. Выход 101 генератора тактовых импульсов 10 подключен к тактовым входам 251-25N каждого из N блоков селекции 21-2N, входы «Обнуление» 241-24N которых являются соответствующими входами «Обнуление» 0171-017N устройства. Причем S-разрядный, где S≥2 - разрядность корректирующего кода времени поиска, корректирующий вход 27n n-ого блока селекции 2n соединен с S-разрядным проверочным входом 82n n-ого селекционного контроллера времени поиска 8n и подключен к n-ому S-разрядному выходу 92n главного контроллера времени поиска 9, N S-разрядных входов 911-91N которого являются соответствующими N S-разрядными входами «Коррекция максимального времени поиска» 016 устройства. При этом K-разрядный выход «Код события» 62 блока формирования адреса маски переходов 6 соединен с K-разрядным входом 111 блока проверки сценария поиска 11, K-разрядный корректировочный выход 113 которого подключен к K-разрядному корректировочному входу 121 блока коррекции сценария поиска 12, контрольный вход 123 которого соединен с контрольным выходом 114 блока проверки сценария поиска 11, K-разрядный прямой выход 112 которого соединен с K-разрядным прямым выходом 122 блока коррекции сценария поиска 12 и подключен к K-разрядным входам «Код события» 52 и 71 регистра стратегии поиска 5 и блока индикации 7 соответственно.

Число «N, (N≥2)» (блоков, разрядов, входов, выходов и т.п.) определяется в соответствии с возможным количеством типов БДИ (они определяют общее количество масок переходов, характеризующих состав сценариев поиска) и, как правило, составляет от 2 (двух) до 500 (пятисот).

Число «K, (где K=(log2 N)+1)» характеризует разрядность кода адреса маски переходов, адреса, по которому в оперативном запоминающем устройстве хранится маска переходов, определяющая тип ожидаемых согласно сценария поиска БДИ. Иными словами, это количество двоичных разрядов, достаточное для адресации N масок переходов и маски начала сценария поиска, как правило, составляет от 2 (двух) до 20 (двадцати).

Число «М, (М≥2)» характеризует разрядность кода времени ожидания - кода допустимого интервала времени, в течение которого ожидается очередной БДИ, заданный сценарием поиска и, как правило, составляет от 2 (двух) до 10 (десяти).

Число «L, (L≥2)» характеризует максимально возможное количество разрядов в БДИ, используемых в сценарии поиска и составляет от 2 (двух) до 10 (десяти).

Число «S, (S≥2)» характеризует разрядность корректирующего кода времени поиска, разрядность кода, обуславливающего изначальное или подвергшееся коррекции (новое) значение максимального времени поиска для каждого конкретного сценария (поискового запроса) и, как правило, составляет от 2 (двух) до 10 (десяти).

Блок проверки сценария поиска 11, изображенный на фиг. 2, предназначен для предварительного анализа (селекции) данных об истинных значениях кода типа БДИ и принятия решения о математической природе этих данных (данные однозначны или неоднозначны (недостоверны, неполны) и нуждаются в верификации), а также для регистрации данных, характеризующих тип ожидаемых БДИ и преобразования этих данных из параллельного кода в последовательный.

Блок проверки сценария поиска 11 (фиг. 2) состоит из селектора кода типа БДИ 11.1 и преобразователя кода типа БДИ 11.2, K-разрядный выход которого является K-разрядным корректировочным выходом 113 блока проверки сценария поиска 11, выход передачи TxD преобразователя кода типа БДИ 11.2 является контрольным выходом 114 блока проверки сценария поиска 11, разрешающий выход DSR преобразователя кода типа БДИ 11.2 соединен с инверсным разрешающим входом селектора кода типа БДИ 11.1, K-разрядный выход которого является K-разрядным прямым выходом 112 блока проверки сценария поиска 11. Запрещающий вход DST преобразователя кода типа БДИ 11.2 подключен к запрещающему выходу МТ селектора кода типа БДИ 11.1, K-разрядный вход которого соединен с K-разрядным входом преобразователя кода типа БДИ 11.2 и является K-разрядным входом 111 блока проверки сценария поиска 11.

Селектор кода типа БДИ 11.1 блока проверки сценария поиска 11 предназначен для осуществления процедуры предварительного анализа (селекции) данных об истинных значениях кода типа БДИ и принятия решения о математической природе этих данных - данные, характеризующие тип ожидаемых БДИ идентифицированы (определены) однозначно или неоднозначно (недостоверно, неполно) и нуждаются в верификации. Селектор кода типа БДИ 11.1 может быть технически реализован в виде серийно выпускаемого селектора на КМДП-структурах с одним инверсным разрешающим входом и одним запрещающим выходом, на базе интегральной микросхемы серии 564 (например, SEL К564КП2), как показано в литературе [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994. С. 28-33].

Преобразователь кода типа БДИ 11.2 блока проверки сценария поиска 11 предназначен для регистрации данных, характеризующих тип ожидаемых БДИ и преобразования этих данных из параллельного кода в последовательный. Преобразователь кода типа БДИ 11.2 может быть технически реализован в виде универсального программируемого синхронно-асинхронного приемопередатчика на базе интегральной микросхемы PCI КР580ИК51, описанной в [Гришин Г.Г., Мошков А.А., Ольшанский О.В. и др. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. 2-е изд. - Л.: Судостроение, 1988. С. 66-74, рис. 3.14].

Блок коррекции сценария поиска 12, изображенный на фиг. 3, предназначен для преобразования идентифицируемых недостоверно (неполно, противоречиво) значений кода типа БДИ, к виду, пригодному для однозначного принятия достоверного решения о типе конкретных ожидаемых БДИ, записи и хранения значений кода, содержащего верифицированные результаты анализа типа ожидаемых БДИ, а также для преобразования этих данных из последовательного кода в параллельный.

Блок коррекции сценария поиска 12 (фиг. 3) состоит из программируемого вычислителя 12.1 и запоминающего элемента 12.2. При этом K-разрядный вход I программируемого вычислителя 12.1 является K-разрядным корректировочным входом 121 блока коррекции сценария поиска 12. Вход OE1 разрешения выходов А программируемого вычислителя 12.1 является контрольным входом 123 блока коррекции сценария поиска 12, К выходов А (А1-AK) программируемого вычислителя 12.1 соединены с соответствующими K входами 12.2-11-12.2-1K запоминающего элемента 12.2, K-разрядный выход которого является K-разрядным прямым выходом 122 блока коррекции сценария поиска 12.

Программируемый вычислитель 12.1 блока коррекции сценария поиска 12 предназначен для осуществления процедуры преобразования идентифицируемых недостоверно (неполно, противоречиво) значений кода, к виду, пригодному для однозначного принятия достоверного решения о типе конкретных ожидаемых БДИ. Программируемый вычислитель 12.1 представляет собой серийно выпускаемую микропроцессорную секцию (МПС или MPS - Micro-Processoring Section) типа MPS К1804ВС1, подробно описанную в [Гришин Г.Г., Мошков А.А., Ольшанский О.В. и др. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. 2-е изд. - Л.: Судостроение, 1988. С. 243-281, рис. 7.1 и 7.2].

Запоминающий элемент 12.2 блока коррекции сценария поиска 12 предназначен для записи и хранения значений кода, содержащего верифицированные результаты анализа типа ожидаемых БДИ, а также для преобразования этих данных из последовательного кода в параллельный. Запоминающий элемент 12.2 может быть технически реализован на базе серийно выпускаемого программируемого запоминающего устройства с К входами и K-разрядным выходом, в соответствии с описанием, представленным в работе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 198-200, рис. 6.11].

Блоки хранения маски 11-1N, входящие в общую структурную схему, идентичны и предназначены для хранения битовых масок, используемых для идентификации элементов входящего потока данных. Принцип работы и структура блоков хранения маски известны, описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 5), структурная схема проиллюстрирована, на примере n-го () блока хранения маски, на фиг. 4.

Блоки селекции 21-2N, входящие в общую структурную схему, идентичны и предназначены для контроля и идентификации соответствующих элементов входящего потока данных, формирования результата поиска, контроля оставшегося времени поиска, а также выработки управляющих сигналов по истечении установленного изначального или вновь вводимого в динамике управления времени поиска для каждого поискового запроса. Структура блоков селекции (БС) и их алгоритм работы известны, подробно описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 4), структурная схема изображена, на примере n-го () БС, на фиг. 5.

Делитель частоты 3, входящий в общую структурную схему, предназначен для увеличения периода следования поступающей на его вход последовательности импульсов. Схема реализации делителя частоты известна и описана в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16). В частности, делитель частоты 3 может быть построен на базе счетчика, как описано в [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с. 62-74]. При этом входом делителя будет счетный вход счетчика, а выходом делителя - один из выходов счетчика.

Формирователь временных интервалов 4, входящий в общую структурную схему, предназначен для контроля интервала времени между элементами входящего потока данных и формирования сигнала по его истечении. Структура и принцип действия формирователя временных интервалов известны, детально описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 6), схема изображена на фиг. 6.

Регистр стратегии поиска 5, входящий в общую структурную схему, предназначен для проверки соответствия порядка следования идентифицированных элементов входящего потока данных заданным правилам и формирования сигнала при поступлении элемента, ожидаемого в соответствии с правилами. Состав элементов и принцип работы регистра стратегии поиска известны, подробно описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 7), структурная схема регистра изображена на фиг. 7.

Блок формирования адреса маски переходов 6, входящий в общую структурную схему, предназначен для формирования и хранения кода, соответствующего маске, определяющей следующий элемент, который должен быть идентифицирован во входящем потоке данных. Принцип работы, состав и взаимосвязь элементов блока формирования адреса маски переходов известны, детально описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 8), структурная схема изображена на фиг. 8.

Блок индикации 7, входящий в общую структурную схему, предназначен для обнаружения признаков, свидетельствующих о завершении заданной правилами последовательности элементов входящего потока данных и формирования соответствующего сигнала. Структура и порядок работы блока индикации известны, описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 9), структурная схема изображена на фиг. 9.

Селекционные контроллеры времени поиска 81-8N, входящие в общую структурную схему, идентичны и предназначены для дешифровки, дополнительного сравнения и контроля нового, вводимого в динамике управления процессом реализации поисковых запросов, S-разрядного кода, обуславливающего новое значение (границы) максимального времени поиска для каждого конкретного поискового запроса. Структура селекционных контроллеров времени поиска (СКВП) и алгоритм их работы известны, подробно описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 2), структурная схема изображена, на примере n-го () СКВП, на фиг. 10.

Главный контроллер времени поиска 9 предназначен для динамической коррекции значений (границ) максимального времени поиска для каждого поискового запроса из любого сочетания N масок переходов (сценариев поиска). Принцип работы, состав, назначение и взаимосвязь элементов главного контроллера времени поиска известны, детально описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 3), структурная схема изображена на фиг. 11.

Генератор тактовых импульсов 10, входящий в общую структурную схему, предназначен для выработки синхронизирующей последовательности импульсов. Техническая реализация генератора тактовых импульсов 10 возможна на базе серийно выпускаемого генератора тактовых импульсов, описанного в работе [Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987. С. 50-53].

Устройство поиска информации работает следующим образом.

Известно [1-6], что с точки зрения верификации кода типа БДИ, существует возможность распознавания (определения) данных, характеризующих этот код, заданных как количественно, так и качественно (недостоверно, неполно, противоречиво). Эта возможность реализуется с использованием нейросетевых вычислительных методов и алгоритмов, позволяющих путем последовательных нейросетевых преобразований, осуществить переход от недостоверно (недостаточно, неполно) распознанных (определенных) данных, характеризующих код типа БДИ к виду данных, пригодному для однозначного принятия достоверного решения о значениях элементов этого кода, в рамках конкретного сценария поиска.

При этом код, характеризующий тип (типы) ожидаемых БДИ - конкретный сценарий поиска и определяющий соответствующие маски переходов, может быть верифицирован на основе математических методов принятия решений в слабоструктурированных задачах - нейросетевых вычислительных методов и алгоритмов, которые достаточно просто могут быть аппаратно реализуемы.

Нейросетевые вычислительные методы и алгоритмы работают на основе экспертных оценок, а для решения задачи объединения мнений экспертов, знания которых используются, например, для верификации кода типа БДИ, используется один из типовых вычислительных алгоритмов теории нейронных сетей - нейросетевой экстраполирующий вычислительный алгоритм, или, так называемая, экстраполирующая нейронная сеть (ЭНС), являющаяся разновидностью известных вычислительных моделей ассоциативной памяти [1-6].

Вычислительный нейросетевой алгоритм (экстраполирующая нейронная сеть) такого класса состоит из двух слоев вычислителей (нейронов) - входного слоя Ua и выходного слоя Ub. Входной слой Ua состоит из Квх нейронов, обладающих набором прямых и обратных связей с Квых нейронами выходного с