Универсальный асинхронный конвертор параллельного цифрового кода

Иллюстрации

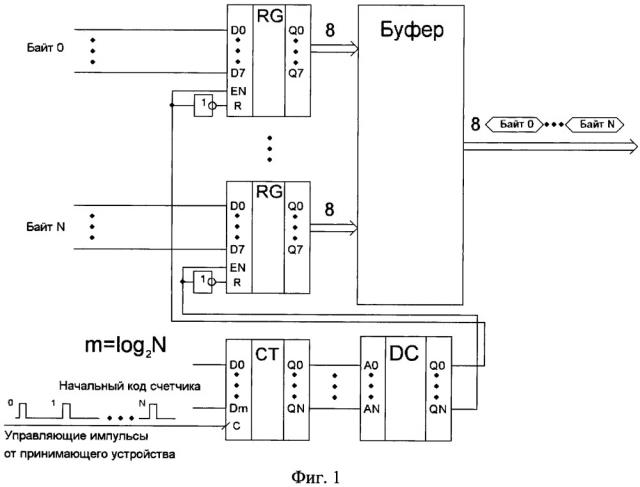

Показать всеИзобретение относится к области представления и передачи цифровых сигналов. Техническим результатом является увеличение разрядности преобразуемого кода, повышение надежности и помехозащищенности схемы. Устройство содержит N 8-разрядных цифровых регистров, буфер, счетчик, дешифратор. 1 ил.

Реферат

Заявляемое техническое решение относится к области представления и передачи цифровых сигналов и предназначено для преобразования передаваемого многоразрядного параллельного цифрового кода в последовательность 8-разрядных цифровых слов.

Например, известен способ передачи параллельного цифрового кода без преобразования (интерфейс Centronics) (см. Огик П. Использование LPT-порта для ввода/вывода информации. // Пер. с франц. Комарова М.А. - М.: НТ Пресс, 2006). Такой способ передачи цифрового кода обладает рядом недостатков:

- необходимость применять микросхемы с большим числом линий портов ввода-вывода;

- увеличение сложности схемы приема информации как следствие уменьшение надежности всей системы;

- повышенные требования помехозащищенности физической среды передачи данных особенно при работе на больших частотах;

- увеличение вероятности возникновения ошибок при передаче цифрового кода.

Наиболее близким является способ передачи параллельного цифрового кода с помощью операций поразрядного сдвига (см. Угрюмов Е.П. Цифровая схемотехника. - БХВ-Петербург, 2004). При этом способе цифровой код поразрядно передается по одной физической линии. Такой способ передачи цифрового кода также обладает рядом недостатков:

- невысокая скорость передачи данных в случае передачи многоразрядного цифрового кода;

- более сложное по сравнению с передачей цифрового кода без преобразования управление потоком передачи выделенных порций информации (цифровых слов).

Предлагаемое техническое решение позволяет устранить вышеупомянутые недостатки:

- упростить передачу и представление цифрового кода;

- упростить схему принимающего устройства;

- увеличить скорость передачи данных в 8 раз по сравнению со схемой поразрядного сдвига;

- обладает свойством универсальности схемы, позволяет достаточно легко изменять число регистров, ориентированных на получение входных данных.

Техническим результатом, на достижение которого направлено заявляемое изобретение, является уменьшение числа линий передачи цифрового кода, повышение надежности и помехозащищенности схемы.

Указанный технический результат достигается тем, что в универсальном асинхронном конверторе параллельного цифрового кода, предназначенном для преобразования параллельного цифрового кода в последовательность байт и построенном на основе микросхем 8-разрядных цифровых регистров, преобразование кода разрядности, не превосходящей 8*N, где N - число байт, осуществляется путем последовательной передачи данных с входов микросхем регистров (байт) на общую восьмиразрядную шину, при этом выходы регистров соединены с общей шиной через буферный элемент, а управление процессом передачи осуществляется принимающим устройством асинхронно путем генерации коротких прямоугольных импульсов для переключения микросхем регистров кодом на выходе дешифратора.

На фиг. 1 дана функциональная схема универсального асинхронного конвертора.

Заявляемое устройство работает следующим образом.

В универсальном асинхронном конверторе используются N 8-разрядных регистров (см. функциональную схему универсального асинхронного конвертора на фиг. 1), организующих передачу данных с входа на выход по фронту синхронизирующего сигнала, получаемого от принимающего устройства, которое и определяет скорость выдачи данных конвертором. Схема, приведенная на фиг. 1, является универсальной, так как допускает ее использование для преобразования параллельного кода сколь угодно большой разрядности (при разрядности большей чем 256*8 вместо отдельных счетчиков и дешифратора будут группы из таких микросхем, но едва ли реальная разрядность на входе схемы будет больше 32 или 64 байт). Выходы регистров объединены через буферный элемент, выдача данных от буферного элемента осуществляется на общую восьмиразрядную шину данных. Как видно из фиг. 1, выбор регистра осуществляется с помощью счетчика, работающего по фронту сигнала от принимающего устройства и микросхемы дешифратора, преобразующей код счетчика в номер активной линии, и, соответственно, номер выбранного регистра. Все остальные регистры, кроме регистра, активного в данный момент, находятся в неактивном (сброшенном) состоянии, а на их выходах логические нули. По вышеуказанной схеме происходит последовательный опрос каждого регистра и передача его входных данных на принимающее устройство. Буферный элемент может быть реализован несколькими различными способами, например восьмью логическими элементами ИЛИ N в 1 или простым монтажным соединением выводом регистров, в случае если выходы регистров имеют третье состояние (высокоимпедансное (Z) состояние).

Универсальный асинхронный конвертор параллельного цифрового кода, предназначенный для преобразования параллельного цифрового кода в последовательность байт, построенный на основе микросхем 8-разрядных цифровых регистров, отличающийся тем, что преобразование параллельного цифрового кода разрядности 8*N, где N - число байт, осуществляется путем последовательной передачи данных с входов микросхем регистров (байт) на общую восьмиразрядную шину, при этом выходы регистров соединены с общей шиной через буферный элемент, а управление процессом передачи осуществляется с помощью счетчика, работающего по фронту сигнала от принимающего устройства и микросхемы дешифратора, преобразующей код счетчика в номер активной линии, соответствующей номеру выбранного регистра.