Устройство обработки данных и способ обработки данных

Иллюстрации

Показать всеГруппа изобретений относится к области обработки данных и может быть использована для кодирования/декодирования с использованием LDPC-кода. Техническим результатом является уменьшение частоты ошибок при передаче данных. LDPC-код имеет длину кода 16200 битов и кодовую скорость 12/15. LDPC-код включает в себя информационный бит и бит четности, и матрица H контроля четности выполнена с информационной частью матрицы, соответствующей информационному биту LDPC-кода и части матрицы четности, соответствующей биту четности. Информационная часть матрицы H контроля четности представлена таблицей начальных значений матрицы контроля четности, представляющих собой позицию элемента 1 в информационной части матрицы с интервалом 360 столбцов. 5 н. и 15 з.п. ф-лы, 60 ил.

Реферат

Область техники, к которой относится изобретение

Данная технология относится к устройству обработки данных и способу обработки данных и, в частности, относится к устройству обработки данных и способу обработки данных, которые способны обеспечить хорошее качество связи при передаче данных с использованием, например, LDPC-кода.

Уровень техники

Код разреженного контроля четности (LDPC) имеет высокую способность коррекции ошибки и в последние годы широко использовался в схеме передачи, включающей в себя цифровое широковещание, такое как, например, европейский стандарт цифрового телевизионного вещания (DVB)-S.2, DVB-T.2 и DVB-C.2 (например, смотри NPL 1).

Последние исследования показывают, что при увеличении длины кода LDPC-код имеет характеристики, близкие к пределу Шеннона и аналогичные турбокодам или т.п. В дополнение к этому, поскольку LDPC-код имеет свойства минимального расстояния, пропорционального длине кода, LDPC-код имеет преимущество в том, что характеристика вероятности блочной ошибки является хорошей, и так называемое явление минимального уровня ошибок, которое наблюдается как свойство декодирования турбо-кода или т.п., почти не возникает в виде свойства.

Перечень цитируемой литературы

Непатентная литература

NPL 1: DVB-S.2: ETSI EN 302307 V1.2.1 (2009-08)

Сущность изобретения

Техническая задача

При передаче данных с использованием, например, LDPC-кода, LDPC-код формируется в символе квадратурной модуляции (цифровой модуляции), такой как квадратурная фазовая манипуляция (QPSK) (символизируется), и символ передается путем отображения в сигнальную точку квадратурной модуляции.

Такая передача данных с использованием LDPC-кода становится широко распространенной во всем мире, и остается востребованным обеспечение хорошего качества связи.

Данная технология была выполнена с учетом таких обстоятельств, и задача изобретения состоит в том, чтобы обеспечить хорошее качество связи при передаче данных с использованием LDPC-кода.

Решение технической задачи

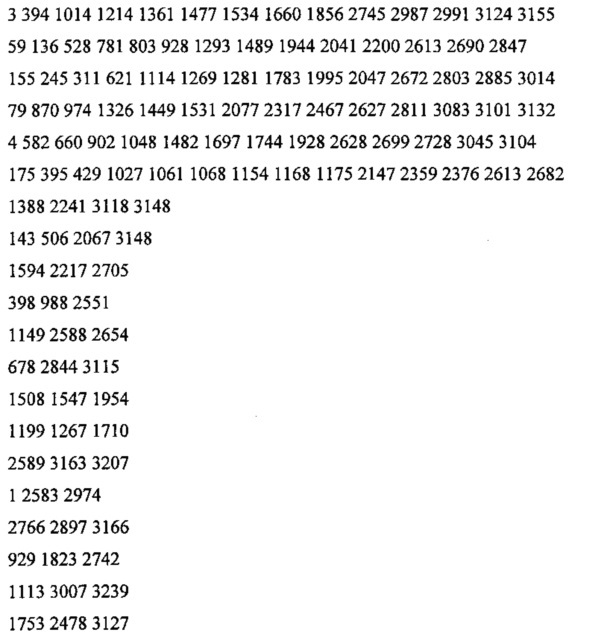

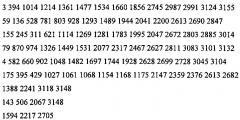

Первое устройство обработки данных (способ обработки данных) данной технологии включает в себя блок кодирования (этап кодирования), который кодирует информационный бит в LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, на основании матрицы контроля четности кода разреженного контроля четности (LDPC), в которой LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

В первом устройстве обработки данных/способе обработки данных, информационный бит кодируется в LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, на основании матрицы контроля четности кода разреженного контроля четности (LDPC). LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

Второе устройство обработки данных (способ обработки данных) данной технологии включает в себя блок декодирования (этап декодирования), который декодирует LDPC-код, полученный из данных, которые передаются из передающего устройства, включающего в себя блок кодирования, который кодирует информационный бит в LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, на основании матрицы контроля четности кода разреженного контроля четности (LDPC), в которой LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

Во втором устройстве обработки данных/способе обработки данных декодируется LDPC-код, который получается из данных, переданных из передающего устройства, причем передающее устройство включает в себя блок кодирования (этап кодирования) который кодирует информационный бит в LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, на основании матрицы контроля четности кода разреженного контроля четности (LDPC), в которой LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

Третье устройство обработки данных данной технологии включает в себя блок декодирования, который декодирует LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, на основании матрицы контроля четности кода разреженного контроля четности (LDPC), в которой LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

В третьем устройстве обработки данных LDPC-код, имеющий длину кода 16200 битов и кодовую скорость 12/15, декодируется на основании матрицы контроля четности кода разреженного контроля четности (LDPC). LDPC-код включает в себя информационный бит и бит четности, матрица контроля четности включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности, информационная часть матрицы представлена таблицей начальных значений матрицы контроля четности, таблица начальных значений матрицы контроля четности представляет собой таблицу, представляющую позиции элементов 1 в информационной части матрицы с интервалом 360 столбцов, и представляет собой

В дополнение, устройство обработки данных может представлять собой независимое устройство или может представлять собой внутренний блок, конфигурирующий одно устройство.

Преимущественные эффекты изобретения

Согласно настоящему изобретению можно обеспечить хорошее качество связи при передаче данных с использованием LDPC-кода.

В дополнение к этому, эффекты, описанные в данном документе, являются только иллюстративными, при этом эффекты данной технологии не предназначены для ограничения эффектов, которые описаны в данном документе, и могут существовать дополнительные эффекты.

Краткое описание чертежей

Фиг. 1 - схема, изображающая матрицу Н контроля четности LDPC-кода.

Фиг. 2 - блок-схема последовательности операций, иллюстрирующая процедуру декодирования LDPC-кода.

Фиг. 3 - схема, иллюстрирующая пример матрицы контроля четности LDPC-кода.

Фиг. 4 - схема, иллюстрирующая график Таннера матрицы контроля четности.

Фиг. 5 - схема, иллюстрирующая переменный узел.

Фиг. 6 - схема, иллюстрирующая контрольный узел.

Фиг. 7 - схема, иллюстрирующая пример конфигурации варианта осуществления передающей системы, в которой применяется данная технология.

Фиг. 8 - схема, иллюстрирующая пример конфигурации передающего устройства 11.

Фиг. 9 - блок-схема, иллюстрирующая пример конфигурации перемежителя 116 битов.

Фиг. 10 - схема, иллюстрирующая матрица контроля четности.

Фиг. 11 - схема, иллюстрирующая матрицу четности.

Фиг. 12 - схема, иллюстрирующая матрицу контроля четности LDPC-кода, который определен в стандарте DVB-S.2.

Фиг. 13 - схема, изображающая матрицу контроля четности LDPC-кода, который определен в стандарте DVB-S.2.

Фиг. 14 - схема, иллюстрирующая размещение сигнальных точек 16QAM.

Фиг. 15 - схема, иллюстрирующая размещение сигнальных точек 64QAM.

Фиг. 16 - схема, иллюстрирующая размещение сигнальных точек 64QAM.

Фиг. 17 - схема, иллюстрирующая размещение сигнальных точек 64QAM.

Фиг. 18 - схема, иллюстрирующая размещение сигнальных точек, которое определено в стандарте DVB-S.2.

Фиг. 19 - схема, иллюстрирующая размещение сигнальных точек, которое определено в стандарте DVB-S.2.

Фиг. 20 - схема, иллюстрирующая размещение сигнальных точек, которое определено в стандарте DVB-S.2.

Фиг. 21 - схема, иллюстрирующая размещение сигнальных точек, которое определено в стандарте DVB-S.2.

Фиг. 22 - схема, изображающая процесс, выполняемый демультиплексором 25.

Фиг. 23 - схема, изображающая процесс, выполняемый демультиплексором 25.

Фиг. 24 - схема, иллюстрирующая график Таннера для декодирования LDPC-кода.

Фиг. 25 - схема, иллюстрирующая матрицу HT четности имеющий ступенчатую структуру и график Таннера, соответствующий матрице HT четности.

Фиг. 26 - схема, иллюстрирующая матрицу HT четности матрицы H контроля четности, соответствующей LDPC-коду после перемежения четности.

Фиг. 27 - схема, иллюстрирующая матрицу контроля четности преобразования.

Фиг. 28 - схема, изображающая процесс, выполняемый перемежителем 24 со скручиванием столбцов.

Фиг. 29 - схема, иллюстрирующая число столбцов и адрес позиции начала записи памяти 31, которая требуется для перемежения со скручиванием столбцов.

Фиг. 30 - схема, иллюстрирующая число столбцов и адрес позиции начала записи памяти 31, которая требуется для перемежения со скручиванием столбцов.

Фиг. 31 - блок-схема последовательности операций, иллюстрирующая процесс, выполняемый в перемежителе 116 битов и устройстве 117 отображения.

Фиг. 32 - схема, иллюстрирующая модель канала связи, используемую при моделировании.

Фиг. 33 - схема, иллюстрирующая зависимость между частотой появления ошибок, полученной путем моделирования, и доплеровской частотой fd фазового дрожания.

Фиг. 34 - схема, иллюстрирующая зависимость между частотой появления ошибок, полученной путем модуляции, и доплеровской частотой fd фазового дрожания.

Фиг. 35 - блок-схема, иллюстрирующая пример конфигурации LDPC-кодера 115.

Фиг. 36 - блок-схема последовательности операций, иллюстрирующая процесс LDPC-кодера 115.

Фиг. 37 - схема, иллюстрирующая пример таблицы начальных значений матрицы контроля четности, в которой кодовая скорость равна 1/4, и длина кода равна 16200.

Фиг. 38 - схема, изображающая способ получения матрицы H контроля четности из таблицы начальных значений матрицы контроля четности.

Фиг. 39 - схема, иллюстрирующая пример таблицы начальных значений матрицы контроля четности кода 16k с r=12/15.

Фиг. 40 - схема, иллюстрирующая пример график Таннера ансамбля степенной последовательности, в которой вес столбца равен 3, и вес строки равен 6.

Фиг. 41 - схема, иллюстрирующая пример графика Таннера ансамбля многореберного типа.

Фиг. 42 - схема, иллюстрирующая минимальную длину цикла и порог производительности матрицы контроля четности кода 16k с r=12/15.

Фиг. 43 - схема, изображающая матрицу контроля четности кода 16k с r=12/15.

Фиг. 44 - схема, изображающая матрицу контроля четности кода 16k с r=12/15.

Фиг. 45 - схема, иллюстрирующая результат моделирования измерения BER/FER.

Фиг. 46 - блок-схема, иллюстрирующая пример конфигурации приемного устройства 12.

Фиг. 47 - блок-схема, иллюстрирующая пример конфигурации деперемежителя 165 битов.

Фиг. 48 - блок-схема последовательности операций, иллюстрирующая процесс, выполняемый устройством 164 обратного отображения, деперемежителем 165 битов и LDPC-декодером 166.

Фиг. 49 - схема, иллюстрирующая пример матрицы контроля четности LDPC-кода.

Фиг. 50 - схема, иллюстрирующая матрица (матрицу контроля четности преобразования), полученную путем выполнения перестановки строк и перестановки столбцов в отношении матрицы контроля четности.

Фиг. 51 - схема, иллюстрирующая матрицу контроля четности преобразования, которая разделена на 5×5 блоков.

Фиг. 52 - блок-схема, иллюстрирующая пример конфигурации устройства декодирования, которое выполняет вычисление узла в группах P.

Фиг. 53 - блок-схема, иллюстрирующая пример конфигурации LDPC-декодера 166.

Фиг. 54 - схема, изображающая процесс, выполняемый мультиплексором 54, конфигурирующим деперемежитель 165 битов.

Фиг. 55 - схема, изображающая процесс, выполняемый деперемежителем 55 со скручиванием столбцов.

Фиг. 56 - блок-схема, иллюстрирующая другой пример конфигурации деперемежителя 165 битов.

Фиг. 57 - блок-схема, иллюстрирующая первой пример конфигурации приемной системы, в которой может применяться приемное устройство 12.

Фиг. 58 - блок-схема, иллюстрирующая второй пример конфигурации приемной системы, в которой может применяться приемное устройство 12.

Фиг. 59 - блок-схема, иллюстрирующая третий пример конфигурации приемной системы, в которой может применяться приемное устройство 12.

Фиг. 60 - блок-схема, иллюстрирующая пример конфигурации варианта осуществления компьютера, в котором применяется настоящая технология.

Подробное описание изобретения

Описание вариантов осуществления

Далее перед описанием вариантов осуществления данной технологии будет описан LDPC-код.

LDPC-код

Кроме того, LDPC-код представляет собой линейный код и не должен быть двоичным, но, в данном случае, описание будет приведено исходя из предположения того, что LDPC-код является двоичным.

Наиболее существенный признак LDPC-кода состоит в том, что матрица контроля четности, определяющая LDPC-код, является разреженной матрицей. В данном случае, разреженная матрица представляет собой матрицу, в которой число "1" элементов матрицы является очень маленьким (в основном элементы матрицы равны 0).

На фиг. 1 показана схема, иллюстрирующая матрицу H контроля четности LDPC-кода.

В матрице H контроля четности на фиг. 1, вес каждого столбца (вес столбца) (число "1") (вес) установлен на "3", и вес каждой строки (вес строки) установлен на "6".

При кодировании с использованием LDPC-кода (LDPC-кодирования), например, порождающая матрицы G, вырабатывается на основании матрицы H контроля четности, и кодовое слово (LDPC-код), вырабатывается путем умножения порождающей матрицы G на двоичный информационный бит.

В частности, устройство кодирования, которое выполняет LDPC-кодирование, сначала вычисляет порождающую матрицу G, в которой между матрицей H контроля четности и ее транспонированной матрицей HT устанавливается уравнение GHT=0. В данном случае, когда порождающая матрица G представляет собой матрицу размером K×N, устройство кодирования умножает битовую последовательность (вектор u) информационного бита, сформированного из K битов, с порождающей матрицей G для того, чтобы выработать кодовое слово c (=uG), сформированное из N битов. Кодовое слово (LDPC-код), выработанное с помощью устройства кодирования, принимается на приемной стороне через предварительно определенной канал связи.

Декодирование LDPC-кода представляет собой алгоритм, который предложен и упоминается как вероятностное кодирование Галлагера, и алгоритм можно выполнить с помощью алгоритма передачи сообщений путем распространения по так называемому графу Таннера, который выполнен с переменным узлом (который также упоминается как узел сообщения) и проверочным узлом. Здесь и далее переменный узел и контрольный узел упоминаются при необходимости просто как узел.

На фиг. 2 показана блок-схема последовательности операций, иллюстрирующая процедуру декодирования LDPC-кода.

Здесь и далее при необходимости действительное число (принятое LLR), которое получено путем правдоподобия "0" значения кодового бита LDPC-кода (кодовое слово 1), принятое на приемной стороне в качестве логарифмического отношения правдоподобия, упоминается как принятое значение u0i. Кроме того, предполагается, что сообщение, выходящее из проверочного узла, будет представлять собой uj, и предполагается, что сообщение, выходящее из переменного узла, будет представлять собой vi.

Сначала при декодировании LDPC-кода, как показано на фиг. 2, на этапе S11 принимается LDPC-код, сообщение uj (сообщение проверочного узла) устанавливается в "0", переменная k, которая представляет собой целое число в качестве счетчика итерационного процесса, устанавливается в "0", и процесс переходит на этапе S12. На этапе S12 сообщение vi (сообщение переменного узла) получается путем выполнения вычисления (вычисления переменного узла), показанного в уравнении (1), на основании принятого значения u0i, полученного путем приема LDPC-кода, и сообщение uj получается путем выполнения вычисления (вычисления проверочного узла), показанного в уравнении (2), на основании сообщения vi.

В данном случае, dv и dc в уравнении (1) и в уравнении (2) представляют собой, соответственно, параметры, показывающие число "1" в вертикальном направлении (в направлении столбца) и в горизонтальном направлении (в направлении строки) матрицы H контроля четности, которую можно выбрать произвольным образом. Например, в случае LDPC-кода, показанного на фиг. 1, в котором вес столбца равен 3, и вес строки равен 6 (LDPC-код (3, 6)), он устанавливается с параметрами dv=3 и dc=6.

В дополнение к этому, при вычислении переменного узла из уравнения (1) и вычислении проверочного узла из уравнения (2) сообщение, которое вводится с края (линия, соединяющая переменный узел и проверочный узел), и из которого должно выводиться сообщение, не используется в качестве цели вычисления, и таким образом, диапазон вычисления равен 1 - Dv-1 или 1 - Dc-1. Кроме того, вычисление проверочного узла из уравнения (2) выполняется фактически путем предварительного создания таблицы из функции R(v1,v2), показанной в уравнении (3), которая определена в качестве одного выхода для двух входов v1 и v2 и непрерывно (рекурсивно) использует таблицу, как показано в уравнении (4).

На этапе S12 переменная k получает приращение на "1", и процесс переходит на этап S13. На этапе S13 определяется, больше или нет переменная k, чем предварительно определенное итерационное число C декодирования. На этапе S13, если определено, что переменная k не будет больше, чем C, процесс возвращается на этап S12, и повторяется тот же самый процесс.

Кроме того, на этапе S13, если определено, что переменная k больше, чем C, процесс переходит на этап S14, сообщение vi, в качестве результата декодирования, который будет окончательно выводиться, получается и выводится путем выполнения вычисления, показанного в уравнении (5), и процесс декодирования LDPC-кода заканчивается.

В данном случае, вычисление уравнения (5) отличается от вычисления переменного узла из уравнения (1) и выполняется с использованием сообщения uj со всех ребер, связанных с переменным узлом.

На фиг. 3 показана схема, иллюстрирующая пример матрицы H контроля четности с LDPC-кодом (3, 6) (кодовая скорость равна 1/2, длина кода равна 12).

В матрице H контроля четности, показанной на фиг. 3, вес столбца установлен на 3, и вес строки установлен на 6, аналогично фиг. 1.

На фиг. 4 показана схема, иллюстрирующая график Таннера матрицы H контроля четности (фиг. 3).

В данном случае, на фиг. 4, проверочные узлы показаны знаком плюс "+", и переменные узлы показаны знаком равно "=". Проверочные узлы и переменные узлы, соответственно, соответствуют строкам и столбцам матрицы H контроля четности. Соединительные линии между проверочными узлами и переменными узлами представляют собой ребро, и ребра соответствуют элементам "1" в матрице контроля четности.

Другими словами, если элемент в j-ой строке и i-ом столбце матрицы контроля четности равен 1 (фиг. 4), i-ый переменный узел (узел "=") сверху и j-ый проверочный узел (узел "+") сверху соединены с помощью ребра. Ребро представляет собой то, что кодовый бит, соответствующий переменному узлу, имеет ограничения, соответствующие проверочному узлу.

В алгоритме произведения суммы, который представляет собой способ декодирования LDPC-кода, вычисление переменного узла и вычисление проверочного узла выполняются повторно.

На фиг. 5 показана схема, иллюстрирующая вычисление переменного узла, которое выполняется в переменном узле.

В переменном узле сообщение vi, соответствующее ребру, подлежащему вычислению, получается путем вычисления переменного узла из уравнения (1) с использованием сообщений u1 и u2 из оставшихся ребер, которые соединены с переменным узлом, и принятого значения u0i. Сообщения, соответствующие другим ребрам, получаются таким же образом.

На фиг. 6 показана схема, иллюстрирующая вычисление проверочного узла, которая выполняется в проверочном узле.

В данном случае, вычисление проверочного узла из уравнения (2) можно переписать в виде уравнения (6) с использованием функциональной зависимости уравнения a×b=exp{ln(|a|)+ln(|b|)}×sign(a)×sign(b). В данном случае, sign(x) равен 1 при x≥0, и sign(x) равен -1 при x<0.

Когда x≥0, если функция ϕ(x) определена в виде уравнения ϕ(x)=Ln(tanh(x/2)), устанавливается уравнение ϕ-1(x)=2tanh-1(e-x) таким образом, что уравнение (6) можно преобразовать в уравнение (7).

В проверочном узле вычисление проверочного узла из уравнения (2) выполняется в соответствии с уравнением (7).

Другими словами, в проверочном узле, как показано на фиг. 6, сообщение Uj, соответствующее ребру, которое будет вычисляться, получается с помощью вычисления проверочного узла из уравнения (7) с использованием сообщений v1, v2, v3, v4, и v5 из оставшихся ребер, которые соединены с проверочным узлом. Сообщения, соответствующие другим ребрам, получаются таким же образом.

В дополнение, функция ϕ(x) из уравнения (7) может быть представлена в виде уравнения ϕ(x)=ln((ex+1)/(ex-1)), когда x>0, ϕ(x)=ϕ-1(x). Когда функции ϕ(x) и ϕ-1(x) реализованы в виде обратных средств, в некоторых случаях функции можно реализовать с использованием таблиц поиска (LUT), но LUT являются одинаковыми.

Пример конфигурации передающей системы, в которой применяется настоящая технология

На фиг. 7 показана схема, иллюстрирующая пример конфигурации варианта осуществления передающей системы, в которой применяется настоящая технология (система относится к таким системам, в которых множество устройств ассемблируется логическим образом, и не имеет значение то, находится ли устройство, составляющее часть целого, в одном и том же корпусе).

На фиг. 7 передающая система включает в себя передающее устройство 11 и приемное устройство 12.

Передающее устройство 11 выполняет передачу (широковещание) (отправку), например, программ и т.п. телевизионного вещания. Другими словами, передающее устройство 11 кодирует, например, целевые данные, которые представляют собой цель передачи, такие как данные изображения и аудиоданные в виде программы в LDPC-код, и передает кодированные целевые данные через канал 13 связи, такой как, например, спутниковые линии, наземные волны, кабели (проводные линии).

Приемное устройство 12 принимает LDPC-код, который передается из передающего устройства 11 через канал 13 связи, декодирует LDPC-код в целевые данные и выводит данные.

В данном случае, известно, что LDPC-код, который используется в системе передачи, показанной на фиг. 7, проявляет в значительной степени высокую пропускную способность в канале связи с аддитивным белым гауссовым шумом (AWGN).

Между тем, канал 13 связи может вырабатывать пакетную ошибку или стирание пакета. Например, в частности, когда канал 13 связи представляет собой наземные волны, в системе ортогонального мультиплексирования с частотным разделением (OFDM) в многолучевой среде, в которой отношение желательного сигнала к нежелательному (D/U) равно 0 дБ (мощность нежелательного сигнала (эхо-сигнала) равна мощности желательного сигнала (сигнала, распространяющегося по основному пути)), мощность определенного символа становится равной 0 (стирание) в соответствии с задержкой эхо-сигнала (путь распространения отличается от основного пути распространения).

Кроме того, даже при фазовом дрожании (канал связи, в котором задержка равна 0, и добавляется эхо-сигнал из-за доплеровской частоты), если отношение D/U равно 0 дБ, мощность всех OFDM символов в специфический момент времени становится равной 0 (стирание) из-за Доплеровской частоты.

Кроме того, пакетная ошибка может возникать из-за статуса проводного соединения из приемного блока (не показан), такого как антенна, которая принимает сигналы из передающего устройства 11 на стороне приемного устройства 12 в приемное устройство 12, и нестабильности мощности приемного устройства 12.

Между тем, при декодировании LDPC-кода в столбце матрицы H контроля четности и переменного узла, соответствующего кодовому биту LDPC-кода, как показано на фиг. 5, поскольку выполняется вычисление переменного узла из уравнения (1) с добавлением кодового бита (его принятого значения u0i) LDPC-кода, если в кодовом бите, используемом при вычислении переменного узла, возникает ошибка, точность полученного сообщения уменьшается.

Затем при декодировании LDPC-кода, поскольку вычисление проверочного узла из уравнения (7) в проверочном узле выполняется с использованием сообщения, которое получено в переменном узле, который подсоединен к проверочному узлу, если увеличивается число проверочных узлов, в которых множество переменных узлов, соединенных с ним (кодовый бит LDPC-кода, соответствующий ему), одновременно становится ошибочным состоянием (включая стирание), производительность декодирования ухудшается.

Другими словами, например, если два или более переменных узлов, подсоединенных к проверочному узлу, стираются одновременно, проверочный узел возвращает сообщение, в котором вероятность наличия значения 0 и вероятность наличия значения 1 являются одинаковыми во всех переменных узлах. В этом случае, проверочный узел, которые возвращает сообщение с равной вероятностью, не вносит вклад ни в один процесс декодирования (один набор из вычисления переменного узла и вычисления проверочного узла), в результате требуется большое число итераций процесса декодирования, производительность декодирования ухудшается, и увеличивается потребляемая мощность приемного устройства 12, которая декодирует LDPC-код.

Таким образом, передающая система, показанная на фиг. 7, позволяет повысить стойкость к ошибке и стиранию пакета при сохранении производительности в канале связи AWGN (AWGN-канале).

Пример конфигурации передающего устройства 11

На фиг. 8 показана блок-схема, иллюстрирующая пример конфигурации передающего устройства 11 (фиг. 7).

В передающем устройстве 11 входные потоки из одного или более входных потоков в качестве целевых данных подаются в мультиплексор 111 с адаптацией режима.

Мультиплексор 111 с адаптацией режима выполняет процесс, такой как выбор режима и мультиплексирование одного или более входных потоков, подаваемых в него, при необходимости, и обеспечивают подачу результирующих данных в блок 112 набивки.

Блок 112 набивки выполняет необходимую набивку нулями (вставку нулей) в отношении данных, полученных из мультиплексора 111 с адаптацией режима, и обеспечивает подачу результирующих данных в BB-скремблер 113.

BB-скремблер 113 выполняет основополосное скремблирование (BB-скремблирование) в отношении данных, поступающих из блока 112 набивки, и подает результирующие данные в BCH-кодер 114.

BCH-кодер 114 выполняет BCH-кодирование-кодирование над данными, поступающими из BB-скремблера 113, и подает результирующие данные в виде целевых LDPC-данных, которые представляют собой цель LDPC-кодирования, в LDPC-кодер 115.

LDPC-кодер 115 выполняет LDPC-кодирование в соответствии с матрицей контроля четности, в которой матрица четности, которая представляет собой часть, соответствующую битам четности LDPC-кода, имеет ступенчатую структуру над целевыми LDPC-данными, поступающими из BCH-кодера 114, и выводит LDPC-код с целевыми LDPC-данными в виде информационного бита.

Другими словами, LDPC-кодер 115 выполняет LDPC-кодирование, которое кодирует целевые LDPC-данные в LDPC-код (соответствующий матрице контроля четности), который определен в предварительно определенной стандартах, таких как, например, DVB-S.2, DVB-T.2 и DVB-C.2, или в LDPC-код (соответствующий матрице контроля четности), который определяется заранее, и выводит результирующий LDPC-код.

В данном случае, LDPC-код, который определен в стандартах, таких как DVB-S.2, DVB-T.2 и DVB-C.2, представляет собой нерегулярный код повторения-накопления (IRA), и матрица четности в матрице контроля четности LDPC-кода имеет ступенчатую структуру. Матрица четности и ступенчатая структура будут описаны позже. Кроме того, код IRA описан, например, в "Irregular Repeat-accumulate Codes," Н. Jin, A. Khandekar, and RJ. McEliece, in Proceedings of 2nd International Symposium on Turbo codes and Related Topics, pp. 1-8, Sept. 2000.

LDPC-код, выводимый из кодера 115 LDPC, подается в перемежитель 116 битов.

Перемежитель 116 битов выполняет перемежение битов, которое будет описано позже, над LDPC-кодом, поступающим из LDPC-кодера 115, и подает LDPC-код после битового перемежения в блок 117 отображения.

Блок 117 отображения выполняет квадратурную модуляцию (многоуровневую модуляцию) путем отображения LDPC-кода, поступающего из перемежителя 116 битов, в сигнальную точку, представляющую один символ квадратурной модуляции, в блок кодового бита одного бита или более из LDPC-кода (символьного блока).

Другими словами, блок 117 отображения выполняет квадратурную модуляцию путем отображения LDPC-кода, поступающего из битового перемежителя 116, в сигнальные точки, которые определены в схеме модуляции, которая выполняет квадратурную модуляцию LDPC-кода, на плоскости IQ (созвездии IQ), которая определена в виде оси I, представляющей собой компоненту I, которая находится в фазе с несущей волной, и оси Q, представляющей собой компоненту Q, которая ортогональна несущей волне.

В данном случае, пример схема модуляции квадратурной модуляции, выполняемой в блоке 117 отображения, включает в себя, например, схему модуляции, которая определена в стандартах, таких как DVB-S.2, DVB-T.2 и DVB-C.2, и другие схемы модуляции, иными словами, например, двоичную фазовую манипуляцию (BPSK), квадратурную фазовую манипуляцию (QPSK), 8-позиционную фазовую манипуляцию (PSK), 16-позиционную амплитудно-фазовую манипуляцию (APSK), 32 APSK, 16-позиционную квадратурную амплитудную модуляцию (QAM), 64QAM, 256QAM, 1024QAM, 4096QAM и 4-позиционную импульсную амплитудную модуляцию (PAM). В блоке 117 отображения схема модуляции, с помощью которой выполняется квадратурная модуляция, устанавливается заранее, например, в соответствии с операцией оператора передающего устройства 11.

Данные, которые получаются с помощью процесса, выполняемого в блоке 117 отображения (результат отображения, полученные путем отображения символа в сигнальную точку), подаются во временной перемежитель 118.

Временной перемежитель 118 выполняет временное перемежение (перемежение в направлении времени) в блоке символа над данными, поступающими из блока 117 отображения, и подает результирующие данные в кодер 119 с одним входом и одним выходом/с множеством входов и одним выходом (SISO/MISO).

Кодер 119 SISO/MISO выполняет пространственно-временное кодирование над данными, поступающими из временного перемежителя 118, и подает результирующие данные в частотный перемежитель 120.

Частотный перемежитель 120 выполняет частотное перемежение (перемежение в частотном направлении) в блоке символа над данными, поступающими из кодера 119 SISO/MISO, и подает результирующие данные в блок 131 построителя кадров/выделения ресурсов.

Между тем, например, управляющие данные для управления передачей, такие как основополосная сигнализация (BB-сигнализация) (заголовок BB) подается в BCH-кодер 121.

BCH-кодер 121 аналогично BCH-кодеру 114 выполняет BCH-кодирование управляющих данных, подаваемых в него, и подает результирующие данные в LDPC-кодер 122.

LDPC-кодер 122, аналогично LDPC-кодеру 115, выполняет LDPC-кодирование над данными, поступающими из BCH-кодера 121 в качестве целевых LDPC-данных, и подает результирующий LDPC-код в блок 123 отображения.

Блок 123 отображения, аналогично блоку 117 отображения, выполняет квадратурную модуляцию путем отображения LDPC-кода, поступающего из LDPC-кодера 122, в сигнальную точку, представляющую один символ квадратурной модуляции, в блоке кодового бита из одного бита или более LDPC-кода (символьного блока), и подает результирующие данные в частотный перемежитель 124.

Частотный перемежитель 124, аналогично частотному перемежителю 120, выполняет частотное перемежение в символьном блоке над данными, поступающими из блока 123 отображения, и подает результирующие данные в блок 131 выделения ресурсов/построитель кадров.

Блок 131 выделения ресурсов/построитель кадров вставляет пилотный символ в необходимую позицию данных (символа), поступающих из частотных перемежителей 120 и 124, вырабатывает кадр, сформированный из символов с предварительно определенным числом (например, кадр физического уровня (PL), кадр T2, кадр C2 и т.п.), из результирующих данных (символа) и подает кадр в блок 132 выработки OFDM-сигнала.

Блок 132 выработки OFDM-сигнала вырабатывает OFDM-сигнал, соответствующий кадру, из кадра, поступающего из блока 131 выделения ресурсов/построения кадров, и передает OFDM-сигнал через канал 13 связи (фиг. 7).

В дополнение, передающее устройство 11 можно сконфигурировать без наличия некоторых блоков, показанных на фиг. 8, таких как, например, временной перемежитель 118, кодер 119 SISO/MISO, частотный перемежитель 120 и частотный перемежитель 124.

Фиг. 9 иллюстрирует пример конфигурации перемежителя 116 битов, показанного на фиг. 8.

Перемежитель 116 битов имеет функцию перемежения данных и выполнен с перемежителем 23 четности, перемежителем 24 со скручиванием столбцов и демультиплексором (DEMUX) 25. В дополнение, перемежитель 116 битов можно выполнить без наличия одного или двух из перемежителя 23 четности и перемежителя 24 со скручиванием столбцов.

Перемежитель 23 четности выполняет перемежение битов четности, которое обеспечивает перемежение бита четности LDPC-кода, поступающего из LDPC-кодера 115, в позиции другого бита четности и подает LDPC-код после перемежения четности в перемежитель 24 со скручиванием столбцов.

Перемежитель 24 со скручиванием столбцов выполняет перемежение со скручиванием столбцов над LDPC-кодом,