Устройство синхронизации псевдослучайной последовательности на основе мажоритарного декодирования для широкополосных систем связи

Иллюстрации

Показать всеИзобретение относится к устройству синхронизации псевдослучайной последовательности (ПСП) на основе мажоритарного декодирования для широкополосных систем связи, относящемуся к области передачи дискретной информации и используемому для синхронизации псевдослучайных последовательностей в системах связи с CDMA и MC-CDMA в каналах низкого качества. Технический результат – повышение вероятности синхронизации ПСП при использовании устройства в широкополосных системах связи CDMA и MC-CDMA в каналах низкого качества и уменьшение аппаратной сложности устройства при синхронизации апериодических ПСП. Для этого устройство содержит блок решающего устройства, регистратор фазы ПСП, генератор элементов поля α, блок ключевых схем “И”, сумматоры, коммутатор, блок счетчиков с пороговыми элементами, блок управления, датчик ПСП, схему подгона, коррелятор и блок порога. 1 ил.

Реферат

Предлагаемое изобретение относится к области передачи дискретной информации и может быть использовано для синхронизации псевдослучайной последовательности (ПСП) в каналах низкого качества как в системах специальной связи, так и в системах гражданского назначения на базе CDMA и MC-CDMA.

Устройством-аналогом является устройство, предложенное в статье Kilgus C.«Pseudonoisecodeacquisitionmajoritylogicdecoding». - IEEE Trans. onCommunication, COM-21, 1973, №6, c. 772-774.

Устройство содержит датчик ПСП, один из входов которого подключен к выходу блока декодирования (приема) ПСП, состоящего из мажоритарной решающей схемы, входы которой подключены к сумматорам по модулю два, к входам которых подключены выходы ячеек памяти регистратора фазы ПСП (сдвигового регистра).

Недостатком данного устройства является высокая аппаратная сложность при использовании апериодических ПСП, которая растет линейно с увеличением периода ПСП. К тому же устройство разработано для традиционных систем связи с одной несущей и при использовании его в системах с многими несущими или поднесущими, например в системах связи с множественным доступом МС-CDMA уменьшается точность синхронизации ПСП за счет неполного использования частотного ресурса, когда передача ПСП происходит только на одной поднесущей.

Наиболее близким техническим решением является устройство для мажоритарного декодирования ПСП, предложенное в работе Новиков И.А., Номоконов В. Н., Шебанов А. А., Яковлев Д.О. «К вопросу о мажоритарном декодировании М-последовательностей». - Вопросы радиоэлектроники. Сер. ОТ, 1976, вып. 5, с. 50-55.

Известное устройство содержит регистратор фазы ПСП, выходы ячеек памяти которого подключены через блок ключевых схем «И» к выходам ячеек памяти генератора элементов поля α; а выходы блока ключевых схем «И» через сумматоры подключены к коммутатору, выходы которого подключены к входам блока счетчиков с пороговыми элементами.

Существенным недостатком этого устройства является то, что устройство предназначено только для декодирования ПСП и также не применимо для систем связи со многими несущими MC-CDMA.

Задачей изобретения является создание устройства, предназначенного для синхронизации ПСП, которое повышает вероятность синхронизации ПСП на каналах низкого качества в широкополосных системах связи CDMA и MC-CDMA, и имеющего малую аппаратную сложность при синхронизации апериодических ПСП.

Эта задача решается тем, что в устройство для мажоритарного декодирования ПСП, содержащее регистратор фазы ПСП, выходы ячеек памяти которого подключены через блок ключевых схем «И» к выходам ячеек памяти генератора элементов поляα, а выходы блока ключевых схем «И» через сумматоры подключены к коммутатору, выходы которого подключены к входам блока счетчиков с пороговыми элементами, добавлены блок решающего устройства, блок управления, датчик ПСП, схема подгона, коррелятор и блок порога. На входы блока решающего устройства подается ПСП из подканалов, а выход подключен к входу регистратора фазы ПСП, один из выходов которого подключен к входу блока управления, выход которого параллельно подключен к одному из входов датчика ПСП и входу схемы подгона. Входы датчика ПСП подключены к выходам блока счетчиков с пороговыми элементами, а выход подключен к одному из входов коррелятора, другой вход которого подключен к выходу блока решающего устройства, выход же коррелятора подключен к входу блока порога, выход которого подключен к одному из входов датчика ПСП.

Благодаря новой совокупности существенных признаков за счет добавления блока решающего устройства, блока управления, датчика ПСП, схемы подгона, коррелятора и блока порога повышается вероятность синхронизации ПСП при использовании устройства в широкополосных системах связи CDMA и MC-CDMA и уменьшается аппаратная сложность при синхронизации апериодических ПСП, которая с увеличением периода ПСП изменяется по логарифмическому закону.

Анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна».

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

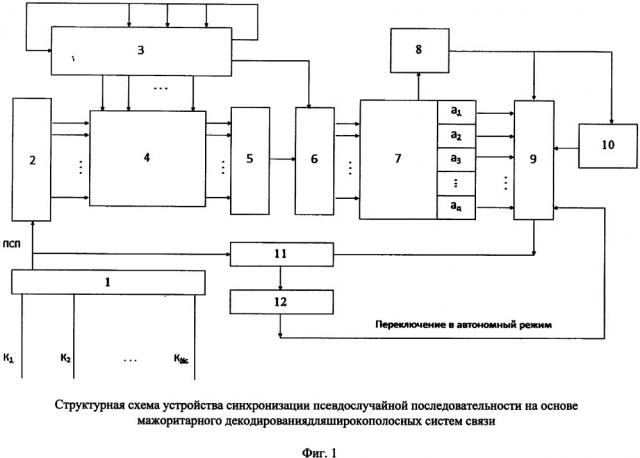

На фиг. 1 представлена структурная схема устройства синхронизации псевдослучайной последовательности для систем связи с многочастотными сигналами. Используемые в фигуре обозначения:

- идентификатор подканала или номер поднесущей в диапазоне 1…Nc;

РУ - решающее устройство;

а1, а2 ,…, аk - декодированные символы начальной фазы ПСП длиной «k» элементов;

ПСП - псевдослучайная последовательность.

Принцип работы устройства поясняется фигурой 1.

Предложенное устройство содержит блок 1 решающего устройства, на входы которого подается ПСП из подканалов, а выход подключен ко входу регистратора 2 фазы ПСП, выходы ячеек памяти которого подключены через блок 4 ключевых схем «И» к выходам ячеек памяти генератора 3 элементов поляα, а выходы блока 4 ключевых схем «И» через сумматоры 5 подключены к коммутатору 6, выходы которого подключены к входам блока 7 счетчиков с пороговыми элементами, один из выходов которого подключен ко входу блока 8 управления, выход которого параллельно подключен к одному из входов датчика 9 ПСП и входу схемы 10 подгона. Входы датчика 9 ПСП подключены к выходам блока 7 счетчиков с пороговыми элементами, а выход подключен к одному из входов коррелятора 11, в свою очередь другой вход которого подключен к выходу блока 1 решающего устройства, выход же коррелятора 11 подключен к входу блока 12 порога, выход которого подключен к одному из входов датчика 9 ПСП.

Устройство работает следующим образом. Блок 1 решающего устройства по большинству принятых символов ПСП из подканалов принимает решение о значении символа ПСП, после чего ПСП записывается в регистратор 2 фазы ПСП. Если в системе используется одна несущая, то есть традиционный CDMA, то символ ПСП сразу после демодулятора записывается в регистратор 2 фазы ПСП, то есть блок 1 решающего устройства не используется в схеме. После приема (записи в регистратор 2 фазы ПСП) первых «κ» символов ПСП запускается генератор 3 элементов поля α с начальным состоянием α°, который за один такт работы регистратора 2 фазы ПСП должен проработать «κ» тактов, при этом последовательно с помощью перемножения в блоке 4 ключевых схем «И» и последующего сложения по модулю два в блоке 5 сумматора по модулю два на выходе коммутатора 6 будут формироваться символы а1, а2 ,…, аk декодируемой начальной фазы ϕ0. В зависимости от начального состояния α° записанного в ячейки памяти генератора 3 элементов поля α, будет декодироваться определенная начальная фаза ПСП ϕ0. При приеме очередного символа состояние генератора 3 элементов поляα будет соответствовать α-1, получаемое за счет сдвига влево из состояния α°. Состояние α-1 даст на выходе сумматора символ a1 и при последовательных сдвигах генератора 3 элементов поля α вправо получим символы ПСП а2 ,…, аk декодируемой начальной фазы ϕ0. В счетчиках 7 с пороговыми элементами будут накапливаться значения а1, а2 ,…, аk и при превышении заданного порога параллельно выдается решение о значении фазы ϕ0. Далее ПСП записывается в датчик 9 ПСП и с помощью блока 8 управления и схемы 10 подгона происходит подгон фазы ПСП на величину задержки равной времени вынесения решения относительно фазы принятого отрезка, которое всегда известно на приеме. Затем ПСП из датчика 9 ПСП поступает на вход 11 коррелятора, на другой вход которого поступает ПСП из блока 1 решающего устройства, после чего напряжение на выходе коррелятора 11 сравнивается с пороговым значением блока 12 порога и при превышении его устройство синхронизации переходит в автономный режим работы. Если переход в автономный режим не происходит, то процесс синхронизации ПСП продолжается.

Устройство синхронизации псевдослучайной последовательности на основе мажоритарного декодирования для широкополосных систем связи, содержащее регистратор фазы псевдослучайной последовательности (ПСП), выходы ячеек памяти которого подключены через блок ключевых схем «И» к выходам ячеек памяти генератора элементов поля α, а выходы блока ключевых схем «И» через сумматоры подключены к коммутатору, выходы которого подключены к входам блока счетчиков с пороговыми элементами, отличающееся тем, что содержит также блок решающего устройства, блок управления, датчик ПСП, схему подгона, коррелятор и блок порога, на входы блока решающего устройства подается ПСП из подканалов, а выход подключен к входу регистратора фазы ПСП, причем один из выходов блока счетчиков с пороговыми элементами подключен к входу блока управления, выход которого параллельно подключен к одному из входов датчика ПСП и входу схемы подгона, выход которой подключен к одному из входов датчика ПСП, другие входы датчика ПСП подключены к выходам блока счетчиков с пороговыми элементами, а выход подключен к одному из входов коррелятора, другой вход которого подключен к выходу блока решающего устройства, выход же коррелятора подключен к входу блока порога, выход которого подключен к одному из входов датчика ПСП.