Устройство для распаковки данных

Иллюстрации

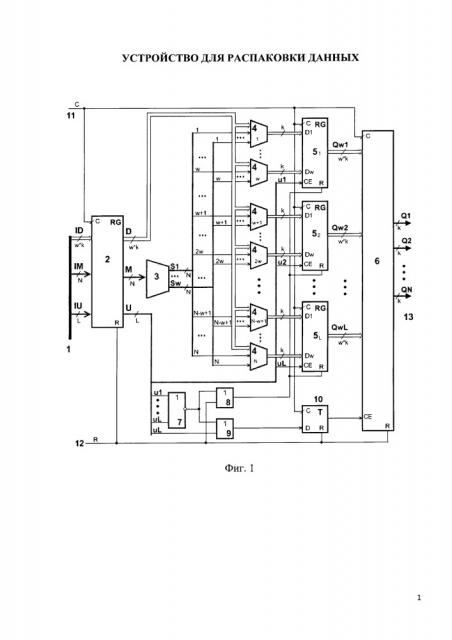

Показать всеИзобретение относится к области вычислительной техники и предназначено для использования в системах обработки информации. Техническим результатом изобретения является расширение функциональных возможностей в части возможности восстановления сжатых данных и простота реализации. Устройство содержит входной регистр данных 2, многовыходной блок приоритета 3, группу из N коммутаторов данных 41, 42, …, 4N, группу из L регистров 51, 52, …, 5L, выходной буфер 6, элемент ИЛИ-НЕ 7, первый элемент ИЛИ 8, второй элемент ИЛИ 9, D-триггер 10, а также шину входных данных 1, внешние выходы 13, внешний вход синхронизации 11, внешний вход синхронной установки нулевое состояние 12, внутренние шину данных D, шину маски символов М и шину указателей групп символов U и w групп N разрядных указателей старшей единицы S1, S2, Sw. Причем входная шина данных 1 содержит входные разряды данных ID, которые состоят из w символов по k разрядов, входные N разрядов маски символов IM и входные L разрядов указателей групп символов IU (L - количество групп по w символов из k разрядов, причем N=L*w). 4 ил.

Реферат

Изобретение относится к области вычислительной техники и предназначено для использования в системах обработки информации, а также может быть применено в блоках сжатия и распаковки данных без потерь в системах для рационального использования устройств хранения и передачи данных, обработки данных физических экспериментов.

Известен способ сжатия данных (RU №2386210 C2, МПК Н03М 7/40, Н03М 7/46, заявлено 04.08.2006, опубликовано 10.04.2010, бюл. №10), в котором сжатие данных осуществляется с помощью кодера. В первом блоке памяти кодера хранятся предварительно записанные кодовые комбинации (KK1) с числом разрядов n, где n=2, 3, 4, …, представляющие собой полный набор возможных входных кодовых комбинаций (КК). Во втором блоке памяти кодера хранятся предварительно записанные кодовые комбинации КК2, однозначно соответствующие КК1, с числом разрядов, меньшим или таким же, как в КК1. Входной поток данных разделяют на КК с одинаковым числом разрядов n. КК последовательно вводят в кодер, идентифицируют путем сравнения с КК1, отображают соответствующий выходной кодовой комбинацией КК2. КК2 представляют собой последовательность групп с одинаковым числом разрядов n в каждой. Совокупное число кодовых комбинаций КК2-mn, где m=2, 3, 4, …, n=1, 2, 3, …. Число последовательных групп КК определяют как mn-1, mn-2, …. Разрядность КК2 в группе выравнивают за счет добавления незначащего нуля перед кодовой комбинацией. Поскольку каждая комбинация КК2 характеризуется двумя параметрами - числом разрядов и численным значением, то процесс декодирования (декомпрессии, идентификации входной КК2 и КК2, а затем и КК1 в памяти декодера) проводится в два этапа: 1) выбор в памяти декодера группы из КК2 с числом разрядов, равным числу разрядов входной КК2, 2) определение внутри установленной группы кодовой комбинации КК2 с численным значением, таким же, как у входной КК2, при этом отпадает необходимость идентификации входной КК2 с КК2 других групп, записанных в памяти декодера.

Известен способ сжатия восстановления данных без потерь (RU №2403677 C1, МПК Н03М 7/30, заявлено 09.02.2009, опубликовано 10.11.2010, бюл. №31), в котором используется сжатие данных, ранее подвергнутых сжатию. В сжимаемом потоке данных считают количество нулей n0 и количество единиц n1, выбирают алгоритм присвоения неповторяющихся цифровых кодов всем возможным перестановкам с повторениями из n0 нулей и n1 единиц и нахождения соответствующей перестановки, которой присваивают цифровой код Nc, считают общее количество кодов nс, определяют значения d1=n0+n1-nc и d2=(n0+n1)/2, а для восстановления потока данных выполняют обратные операции и в соответствии с выбранным алгоритмом по значениям n0, n1, Nc находят конкретную перестановку с повторениями из n0 нулей и n1 единиц, которая соответствует исходному потоку данных.

Недостатком данных устройств является схемная сложность, что затрудняет их применение.

Наиболее близким устройством к заявленному изобретению по совокупности признаков является принятое за прототип устройство для сжатия данных (RU №2622878 С1, МПК Н03М 7/30, заявлено 01.08.2016, опубликовано 20.06.2017, бюл. №17), содержащее N входных символов D1, D2, …, DN по k разрядов соединенных с входным регистром данных 1, группу из L анализаторов символов 21, 22, …, 2L, каждый из которых содержит первую группу из w элементов ИЛИ 3, первую группу из w элементов И 4 и блок счета количества единиц 5 (L - количество групп по w символов из k разрядов, причем N=L*w), группу из (L-1) сумматоров 61, 62, …, 6L-1, группу из (L-1) схем сравнения 71, 72, …, 7L-1, группу из (L-1) D-триггеров 81, 82, 8L-1 с входом разрешения работы СЕ, асинхронным CLR и синхронным R входами установки в нулевое состояние, вторую группу из (L-1) элементов И 91, 92, …, 9L-1, третий элемент И 10, четвертый элемент И 11, второй элемент ИЛИ 12, многовыходной блок приоритета 13, блок коммутаторов данных 14, выходной буфер 15, внешние входы задания количества символов w в группе 16, внешний вход EN разрешения работы 17, внешний вход С синхронизации 18, внешний вход CLR установки в нулевое состояние 19, внешние выходы устройства Q 20, а также внутреннюю шину данных DD из N символов по k разрядов, внутреннюю N разрядную шину маски символов М, внутреннюю L разрядную шину указателей групп символов U, причем многовыходной блок приоритета 13 содержит w групп выходов, все N разрядов внутренней шины маски М соединены с входами многовыходного блока приоритета 13, внешний вход синхронизации 18 соединен с входами синхронизации С входного регистра 1 и выходного буфера 15.

Недостатком данного устройства является отсутствие средств для восстановления сжатых данных.

Техническим результатом изобретения является расширение функциональных возможностей в части возможности восстановления сжатых данных и простота реализации.

Указанный технический результат при осуществлении изобретения достигается тем, что в устройство для распаковки данных, содержащее шину входных данных 1, соединенную с входным регистром данных 2, выходной буфер 6, выходы которого содержат N выходных символов Q1, Q2, …, QN по k разрядов и являются внешними выходами устройства 13, многовыходной блок приоритета 3, который содержит w групп выходов S1, S2, …, Sw по N разрядов, а также внешний вход С синхронизации 11, внутреннюю шину данных D из w символов по k разрядов, внутреннюю N разрядную шину маски символов М, внутреннюю L разрядную шину указателей групп символов U (L - количество групп по w символов из k разрядов, причем N=L*w), причем все N разрядов внутренней шины маски М соединены с входами много выходного блока приоритета 3, внешний вход синхронизации 11 соединен с входами синхронизации С входного регистра данных 2 и выходного буфера 6,

дополнительно введены группа из N коммутаторов данных 41, 42, …, 4N, группа из L регистров 51, 52, …, 5L с синхронным входом R установки в нулевое состояние, элемент ИЛИ-НЕ 7, первый элемент ИЛИ 8, второй элемент ИЛИ 9, D-триггер 10 с синхронным входом R установки в нулевое состояние, а также введен внешний вход R синхронной установки в нулевое состояние 12,

причем шина входных данных 1 содержит группу входных разрядов данных ID из w символов по k разрядов, группу входных N разрядов маски символов IM, группу входных L разрядов указателей групп символов IU,

внешний вход синхронизации 11 также соединен с входами синхронизации С регистров 51, 52, …, 5L и D-триггера 10,

внешний вход 12 синхронной установки в нулевое состояние соединен с входами R синхронной установки в нулевое состояние входного регистра 2, D-триггера 10 и выходного буфера 6, а также соединен со вторым входом первого элементы ИЛИ 8, выход которого соединен с входами R синхронной установки в нулевое состояние регистров 51, 52, …, 5L,

причем выходы входного регистра 2 являются соответствующими w*k разрядами внутренней шины данных D, соответствующими N разрядами внутренней шины маски символов М и соответствующими L разрядами внутренней шины указателей групп символов U,

все w*k разрядов внутренней шины данных D соединены с информационными входами каждого коммутатора данных группы из N коммутаторов данных 41, 42, …, 4N, управляющие входы выборки которых соединены с соответствующими одноименными разрядами w групп выходов S1, S2, …, Sw многовыходного блока приоритета 3, выходы коммутаторов данных 41, 42, …, 4N по w групп соединены с соответствующими информационными входами Dw группы из L регистров 51, 52, …, 5L, y которых управляющие входы СЕ разрешения работы соединены с одноименными разрядами внутренней L разрядной шины указателей групп символов U, а выходы всех L регистров 51, 52, …, 5L соединены с соответствующими информационными входами выходного буфера 6,

а также все L разрядов внутренней шины указателей групп символов U соединены с входами элемента ИЛИ-НЕ 7, выход которого соединен с первыми входами первого элемента ИЛИ 8 и второго элемента ИЛИ 9, второй вход которого соединен с последним L-м разрядом uL внутренней шины указателей групп символов U, а выход второго элемента ИЛИ 9 соединен с информационным D-входом D-триггера 10, выход которого соединен с входом СЕ разрешения работы выходного буфера 6.

На фиг. 1 представлена схема предлагаемого устройства для распаковки данных. На фиг. 2 приведен формат входных данных на шине 1. На фиг. 3 приведены форматы внутренних шин и выходных данных. На фиг. 4 приведена потактовая временная диаграмма.

В устройстве приняты следующие обозначения:

С - вход синхронизации,

СЕ - вход разрешения работы,

D - внутренняя шина данных из w символов по k разрядов,

D1-Dw - информационные входы регистра,

DD - данные до сжатия,

ID - входные разряды данных - w символов по k разрядов,

IM - входные N разрядов маски символов,

IU - входные L разрядов указателей групп символов,

k - разрядность символов,

L - количество групп, причем N=L*w,

М - внутренняя N разрядная шина маски символов,

N - количество выходных символов,

Q1, Q2, …, QN - N выходных символов по k разрядов,

QD - данные после восстановления,

Qw1, Qw2, …, QwL - L групп по w символов из по k разрядов,

R - вход синхронной установки в нулевое состояние,

S1, S2, …, Sw - w групп N разрядных указателей старшей единицы в коде «1 из N»,

U - внутренняя L разрядная шина указателей групп символов,

w - количество символов в каждой группе,

1 - шина входных данных,

2 - входной регистр данных,

3 - многовыходной блок приоритета,

41, 42, …,4N - группа из N коммутаторов данных,

51, 52, …, 5L - группа из L регистров с синхронным входом R установки в нулевое состояние,

6 - выходной буфер,

7 - элемент ИЛИ-НЕ,

8 - первый элемент ИЛИ,

9 - второй элемент ИЛИ,

10 - D-триггер с синхронным входом R установки в нулевое состояние,

11 - внешний вход синхронизации,

12 - внешний вход синхронной установки нулевое состояние,

13 - внешние выходы.

Предлагаемое устройство содержит входной регистр данных 2, многовыходной блок приоритета 3, группу из N коммутаторов данных 41, 42, …, 4N, группу из L регистров 51, 52, …, 5L, выходной буфер 6, элемент ИЛИ-НЕ 7, первый элемент ИЛИ 8, второй элемент ИЛИ 9, D-триггер 10, а также шину входных данных 1, внешние выходы 13, внешний вход синхронизации 11, внешний вход синхронной установки нулевое состояние 12, внутренние шину данных D, шину маски символов М и шину указателей групп символов U и w групп N разрядных указателей старшей единицы S1, S2, …, Sw.

Входная шина данных 1 содержит входные разряды данных ID, которые состоят из w символов по k разрядов, входные N разрядов маски символов IM и входные L разрядов указателей групп символов IU, и подключена к входному регистру данных 2.

Входной регистр данных 2 предназначен для хранения текущей группы данных D из w символов по k разрядов и соответствующим этой группе кодам маски символов М и указателя групп символов U. При этом выходы входного регистра данных 2 являются соответствующими разрядами внутренних шины данных D, шины маски символов М и шины указателей групп символов U.

Входной регистр данных 2, регистры 51, 52, …, 5L, выходной буфер 6 и D-триггер 10 содержат вход синхронизации C и вход синхронной установки в нулевое состояние R.

Внешний вход синхронизации 11 соединен с входами синхронизации С входного регистра 2, регистров 51, 52, …, 5L, выходного буфера 6 и D-триггера 10.

Внешний вход 12 синхронной установки в нулевое состояние соединен с входами R синхронной установки в нулевое состояние входного регистра 2, D-триггера 10 и выходного буфера 6, а также соединен со вторым входом первого элементы ИЛИ 8, выход которого соединен с входами R синхронной установки в нулевое состояние регистров 51, 52, …, 5L.

Все w*k разрядов внутренней шины данных D соединены с информационными входами каждого коммутатора данных группы из N коммутаторов данных 41, 42, …, 4N, управляющие входы выборки которых соединены с соответствующими одноименными разрядами w групп выходов S1, S2, …, Sw многовыходного блока приоритета 3.

Многовыходной блок приоритета 3 формирует на выходах каждой из w групп из N разрядов унитарный код «1 из N», которые соответствуют значению кода на внутренней шине маски М и формируются в порядке старшинства приоритетов. Коммутаторы данных 41, 42, …, 4N предназначены для выделения из w символов по k разрядов с внутренней шины данных D одного из символов разрешенного в соответствии с унитарным кодом «1 из N», установленным на выходах w групп N разрядных указателей старшей единицы S1, S2, …, Sw.

Выходы коммутаторов данных 41, 42, …, 4N по w групп соединены с соответствующими информационными входами D1-Dw группы из L регистров 51, 52, …, 5L, у которых управляющие входы СЕ разрешения работы соединены с одноименными разрядами внутренней L разрядной шины указателей групп символов U.

Группа из L регистров 51, 52, …, 5L предназначена для записи на каждом такте до w символов по k разрядов входных данных ID, в соответствии с кодом L разрядной внутренней шины указателей групп символов U.

Выходы всех L регистров 51, 52, …, 5L соединены с соответствующими информационными входами выходного буфера 6, который предназначен для хранения восстановленного кода после распаковки данных. При этом выходы выходного буфера 6 содержат N выходных символов Q1, Q2, …, QN по k разрядов и являются внешними выходами устройства 13.

Все L разрядов внутренней шины указателей групп символов U соединены с входами элемента ИЛИ-НЕ 7, выход которого соединен с первыми входами первого элемента ИЛИ 8 и второго элемента ИЛИ 9, второй вход которого соединен с последним L-м разрядом uL внутренней шины указателей групп символов U, а выход второго элемента ИЛИ 9 соединен с информационным D-входом D-триггера 10, выход которого соединен с входом СЕ разрешения работы выходного буфера 6.

На выходе элемента ИЛИ-НЕ 7 формируется единичное значение, если нулевые значения установлены во всех L разрядах внутренней шины указателей групп символов U. D-триггер 10 предназначен для приема кода разрешения записи в выходной буфер 6.

Принцип работы предлагаемого устройства состоит в следующем.

После сжатия данных DD, содержащих N символов по k разрядов, которые разбиты на L групп по w символов в каждой группе, формируется последовательность сжатых данных ID, элементы которой содержат до w символов по k разрядов данных, разряды маски символов IM и значения указателей групп IU.

На шину входных данных 1 предлагаемого устройства поступает последовательность сжатых данных, начиная с младших групп символов, содержащая входные разряды данных ID, которые состоят из w символов по k разрядов, и соответствующие им входные N разрядов маски символов IM и входные L разрядов указателей групп символов IU (фиг. 2). При этом единичное значение разряда маски символов IM соответствует ненулевому символу в исходных данных DD до сжатия. Единичное значение разряда указателей групп символов IU соответствует номеру группы, к которому относятся текущие входные w символов по k разрядов.

Многовыходной блок приоритета 3 определяет не только сигнал с наивысшим приоритетом, но также определяет сигналы со вторым, третьим, …, w-м по старшинству приоритетами. В соответствии с кодом маски М на выходах многовыходного блока приоритета 3 формируются w групп приоритета S1, S2, …, Sw в порядке старшинства приоритета. При этом каждому из N разрядов маски символов М присваивается фиксированный приоритет. В устройстве старший приоритет присвоен младшему разряду из N разрядов маски символов М, а далее приоритет уменьшается от разряда к разряду с увеличением номера разряда. Младший приоритет задан для старшего N-го разряда маски символов М. Среди выходных w групп многовыходного блока приоритета 3 наивысший приоритет присвоен младшей первой группе S1, а далее приоритет уменьшается от группы к группе с увеличением номера группы. Младший приоритет задан для группы со старшим номером Sw. На выходах каждой из w групп приоритета S1, S2, …, Sw вырабатывается результат в виде унитарного кода «1 из N» - единичный сигнал будет установлен только на одном выходе, соответствующем высшему (старшему) приоритету.

Далее в соответствии со значениями w групп приоритета S1, S2, …, Sw на выходы группы из N коммутаторов данных 41, 42, …, 4N передаются не более w соответствующих символов входных данных ID. В соответствии с единичными значениями L разрядов указателей групп символов U проводится запись до w входных символов по k разрядов в соответствующие регистры 51, 52, …, 5L. При этом, если в соответствующих разрядах маски М установлены нулевые значения, то в регистрах 51, 52, …, 5L соответствующий им символ будет установлен нулевым.

На следующем такте с шины входных данных 1 проводится прием следующих значений сжатой последовательности данных и далее аналогично проводится восстановление данных и осуществляется прием следующих w входных символов по k разрядов в соответствующие регистры 51, 52, …, 5L.

Если на текущем такте проводится запись в старшую группу символов, когда установлено единичное значение в L-м разряде uL указателей групп символов U, или когда все разряды указателей групп символов U имеют нулевые значения (при этом также все входные символы и все разряды маски М тоже нулевые), то одновременно устанавливается в единичное значение выход D-триггера 10, по которому на следующем такте осуществляется запись значений с выходов регистров 51, 52, …, 5L в выходной буфер 6, которые соответствуют восстановленным данным после распаковки. При этом распакованные данные QD соответствуют данным DD до сжатия без потери информации.

Предлагаемое устройство работает следующим образом.

При подаче единичного сигнала R на вход синхронной установки в нулевое состояние 12 по тактовому сигналу С на внешнем входе 11 в нулевое состояние устанавливаются входной регистр данных 1, группа из L регистров 51, 52, …, 5L, D-триггер 10 и выходной буфер 6.

По следующему тактовому импульсу С осуществляется прием входных данных во входной регистр 2 с шины входных данных 1. При этом прием в регистры 51, 52, …, 5L, и выходной буфер 6 не выполняется, так как у них на входах разрешения СЕ установлены нулевые сигналы, а также в нулевом состоянии остается D-триггер 10. Далее в соответствии с кодом маски М на выходах многовыходного блока приоритета 3 формируются w групп приоритета S1, S2, …, Sw в порядке старшинства приоритета. На выходах каждой из w групп приоритета S1, S2, …, Sw вырабатывается результат в виде унитарного кода «1 из N» - единичный сигнал будет установлен только на одном выходе, соответствующем высшему (старшему) приоритету. В соответствии с единичными значениями сигналов приоритета S1, S2, …, Sw в группе из N коммутаторов данных 41, 42, …, 4N на выходы передаются не более w соответствующих символов входных данных ID. Одновременно значения L разрядов указателей групп символов U передаются на входы разрешения СЕ в группу из L регистров 51, 52, …, 5L.

По следующему тактовому импульсу С в соответствии с единичными значениями L разрядов указателей групп символов U проводится запись до w входных символов по k разрядов в соответствующие регистры 51, 52, …, 5L, а также осуществляется прием следующих данных во входной регистр 2 с шины входных данных 1. Далее аналогично, как в предыдущем такте, проводится анализ следующих разрядов кода маски М и разрядов указателей групп символов U и в группе из N коммутаторов данных 41, 42, …, 4N на выходы передаются следующие w соответствующих символов входных данных ID.

Одновременно, если разрешается запись в старшую группу символов, когда установлено единичное значение в L-м разряде uL указателей групп символов U, то единичное значение также установлено на выходе второго элемента ИЛИ 9 и устанавливается в единичное значение выход D-триггера 10, который соединен с входом разрешения СЕ выходного буфера 6, и по данному единичному сигналу на входе СЕ на следующем такте осуществляется запись значений с выходов регистров 51, 52, …, 5L в выходной буфер 6. Таким образом, на внешних выходах устройства 13 будут сформированы N выходных символов по k разрядов Q1, Q2, …, QN, которые соответствуют восстановленным данным до сжатия.

В потактовой временной диаграмме на фиг. 4 приведен пример последовательности входных данных (DD1 DD6), результат сжатия данных и восстановления сжатых данных в предлагаемом устройстве, при количестве входных символов N=16 по k=4 разрядов, количестве групп L=4 по w=4 символов в группе. На фиг. 4 в скобках указана форма представления данных - двоичная (2) или шестнадцатеричная (16). В такте 1 шестнадцать символов первых данных DD1 до сжатия содержат четыре ненулевых символа (F, 9, 5, 2), которые далее сжимаются, при этом каждая группа содержит один ненулевой символ. В такте 2 сжатые данные поступают в предлагаемое устройство на вход ID=F952, а также поступают соответствующие разряды маски IМ=4112 (содержит по одной единице в каждой группе) и разряды указателей групп символов IU=1111 (все единицы, так как по одному символу содержатся во всех группах), которые принимаются во входной регистр 2. Далее в соответствии со значениями на внутренних шинах кода маски М=4112 и указателей групп символов U=1111 проводится восстановление данных в группе из N коммутаторов данных 41, 42, 43, 44, а затем результаты восстановления в такте 3 записываются во все регистры 51, 52, 5з, 54 (Qw1, Qw2, Qw3, Qw4). При этом также в единичное состояние устанавливается D-триггер 10, так как установлено единичное значение в L-м разряде UL (IU4=1) указателей групп символов U. Поэтому на следующем такте 4 восстановленные данные QD1 (F, 9, 5, 2) записываются в выходной буфер 6 и поступают на внешние выходы 13 соответствующих выходных символов Q1, Q2, …, QN.

В такте 2 вторые данные DD2 содержат четыре ненулевых символа (С, А, 6, 7), которые по два символа расположены во второй w2 и третьей w3 группах. В такте 3 эти данные сжимаются и поступают в предлагаемое устройство на вход ID=CA67, а также соответствующие им разряды маски IМ=0А50 и указателей групп символов IU=1111. Так как в данных DD2 всего четыре символа, то все разряды указателей групп принимают единичные значения. Поэтому в такте 4 результаты восстановления записываются во все регистры 51, 52, 53, 54 (Qw1, Qw2, Qw3, Qw4), а далее в такте 5 восстановленные данные QD2 (С, А, 6, 7) записываются в выходной буфер 6 и поступают на внешние выходы 13 соответствующих выходных символов Q1, Q2, …, QN.

В такте 3 третьи данные DD3 содержат все нулевые символы, для которых формируются нулевые разряды маски IМ=0000 и указателей групп символов IU=0000. В такте 4 входные данные записываются во входной регистр 2, и далее формируется единичное значение на выходе элемента ИЛИ-НЕ 7, по которому в такте 5 устанавливаются в нулевое состояние все регистры 51, 52, 53, 54 (Qw1, Qw2, Qw3, Qw4) и в единичное состояние D-триггер 10. Далее в такте 6 нулевые символы QD3 записываются в выходной буфер 6 и поступают на внешние выходы 13 соответствующих выходных символов Q1, Q2, …, QN.

В такте 4 четвертые данные DD4 содержат девять ненулевых символа (Е, D, С, В, 7, 5, 4, 3,1), которые расположены во всех группах wl - w4. В такте 5 после сжатия первые четыре ненулевые символа (начиная с младших символов) поступают в предлагаемое устройство на вход ID=5431, а также все разряды маски IM=3C5D и разряды указателей групп символов IU=0001. В разрядах указателей групп единичное значение установлено только для первой группы IU1=1, так как количество символов, не превышающее количество символов в каждой группе w=4, соответствует только одной группе w1 (в двух первых группах w1 и w2 содержится пять символов). Далее в такте 6 первые три символа записываются в первый регистр 51 (Qw1=4301) и одновременно следующие четыре ненулевые символа (с четвертого по седьмой символы) поступают в предлагаемое устройство на вход ID=CB75, а также разряды маски IМ=3С50, в которых установлены нулевые значения для младшей группы, так как соответствующие символы уже восстановлены, и разряды указателей групп символов IU=0110, так как четыре ненулевых символа расположены во второй w2 и третьей w3 группах. Поэтому в такте 7 проводится запись во второй регистр 52 (Qw2=0705) и третий регистр 53 (Qw3=CB00) и одновременно следующие два ненулевых символа (восьмой и девятый символы) поступают в предлагаемое устройство на вход ID=00ED, а также соответствующие разряды маски IМ=3000, в которых установлены нулевые значения для трех младших групп, и разряды указателей групп символов ID=1000, так как два ненулевых символа расположены только в четвертой группе. Далее в такте 8 восстановленные данные старшей группы записываются в четвертый регистр 54 (Qw4=00ED), а также в единичное состояние устанавливается D-триггер 10, так как установлено единичное значение в L-м разряде UL (IU4=1) указателей групп символов U. На следующем такте 9 восстановленные данные QD4 записываются в выходной буфер 6 и поступают на внешние выходы 13 соответствующих выходных символов Q1, Q2, …, QN.

Аналогично в такте 7 для пятых данных DD5, содержащих восемь ненулевых символов, которые расположены по два символа в группе, далее выполняется сжатие данных, восстановление за два такта по две группы и запись результата QD5 в выходной регистр 6 на такте 11.

Одновременно в такте 9 поступают шестые данные DD6, содержащие четыре ненулевых символа, расположенные только в одной третьей группе w3. Поэтому при сжатии этих данных формируются входные данные ID=CBA9, разряды маски IM=0F00 и единичные значения для всех разрядов указателей групп IU=1111, так как всего четыре ненулевых символа. Далее на такте 10 восстановленные данные записываются во все регистры 51, 52, 53, 54 (Qw1, Qw2, Qw3, Qw4), а затем на такте 12 восстановленные данные QD6 записываются в выходной буфер 6 и поступают на внешние выходы 13 соответствующих выходных символов Q1, Q2, …, QN.

Таким образом, вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство обладает регулярностью узлов и связей, при этом упрощается конструкция, и устройство соответствует заявляемому техническому результату - обеспечивает возможность восстановления сжатых данных без потерь.

Устройство для распаковки данных, содержащее шину входных данных 1, соединенную с входным регистром данных 2, выходной буфер 6, выходы которого содержат N выходных символов Q1, Q2, …, QN по k разрядов и являются внешними выходами устройства 13, многовыходной блок приоритета 3, который содержит w групп выходов S1, S2, …, Sw по N разрядов, а также внешний вход С синхронизации 11, внутреннюю шину данных D из w символов по k разрядов, внутреннюю N разрядную шину маски символов М, внутреннюю L разрядную шину указателей групп символов U (L - количество групп по w символов из k разрядов, причем N=L*w), причем все N разрядов внутренней шины маски М соединены с входами многовыходного блока приоритета 3, внешний вход синхронизации 11 соединен с входами синхронизации С входного регистра данных 2 и выходного буфера 6, отличающееся тем, что в него дополнительно введены группа из N коммутаторов данных 41, 42, …, 4N, группа из L регистров 51, 52, …, 5L с синхронным входом R установки в нулевое состояние, элемент ИЛИ-НЕ 7, первый элемент ИЛИ 8, второй элемент ИЛИ 9, D-триггер 10 с синхронным входом R установки в нулевое состояние, а также введен внешний вход R синхронной установки в нулевое состояние 12, причем шина входных данных 1 содержит группу входных разрядов данных ID из w символов по k разрядов, группу входных N разрядов маски символов IM, группу входных L разрядов указателей групп символов 1U внешний вход синхронизации 11 также соединен с входами синхронизации C регистров 51, 52, …, 5L и D-триггера 10, внешний вход 12 синхронной установки в нулевое состояние соединен с входами R синхронной установки в нулевое состояние входного регистра 2, D-триггера 10 и выходного буфера 6, а также соединен со вторым входом первого элементы ИЛИ 8, выход которого соединен с входами R синхронной установки в нулевое состояние регистров 51, 52, …, 5L, причем выходы входного регистра 2 являются соответствующими w*k разрядами внутренней шины данных D, соответствующими N разрядами внутренней шины маски символов М и соответствующими L разрядами внутренней шины указателей групп символов U, все w*k разрядов внутренней шины данных D соединены с информационными входами каждого коммутатора данных группы из N коммутаторов данных 41, 42, …, 4N, управляющие входы выборки которых соединены с соответствующими одноименными разрядами w групп выходов S1, S2, …, Sw многовыходного блока приоритета 3, выходы коммутаторов данных 41, 42, …, 4N по w групп соединены с соответствующими информационными входами Dw группы из L регистров 51, 52, …, 5L, у которых управляющие входы СЕ разрешения работы соединены с одноименными разрядами внутренней L разрядной шины указателей групп символов U, а выходы всех L регистров 51, 52, …, 5L соединены с соответствующими информационными входами выходного буфера 6, а также все L разрядов внутренней шины указателей групп символов U соединены с входами элемента ИЛИ-НЕ 7, выход которого соединен с первыми входами первого элемента ИЛИ 8 и второго элемента ИЛИ 9, второй вход которого соединен с последним L-м разрядом uL внутренней шины указателей групп символов U, а выход второго элемента ИЛИ 9 соединен с информационным D-входом D-триггера 10, выход которого соединен с входом СЕ разрешения работы выходного буфера 6.