Способ управления процессором и многопроцессорной системой

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники. Технический результат заключается в повышении скорости доступа к целевому контроллеру узлов. Технический результат достигается за счет многопроцессорной системы, где многопроцессорная система содержит: первый пул с высокоскоростным межсоединением (QPI), второй пул QPI, первую группу контроллеров узлов (NC) и вторую группу NC, причем первая группа NC подсоединена к первому пулу QPI и второму пулу QPI, вторая группа NC подсоединена к первому пулу QPI и второму пулу QPI, каждый пул QPI содержит по меньшей мере один процессор, главный процессор принадлежит первому пулу QPI или второму пулу QPI, при этом главный процессор сконфигурирован: когда NC в первой группе NC должен быть удален, управлять всеми процессорами в многопроцессорной системе, которые выполняют доступ между пулами с использованием первой группы NC, для переключения, путем изменения конфигурации маршрута, на выполнение доступа между пулами с использованием второй группы NC. 10 н. и 26 з.п. ф-лы, 6 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

[0001] Настоящее изобретение относится к области компьютеров, в частности к способу управления процессором и многопроцессорной системой.

УРОВЕНЬ ТЕХНИКИ

[0002] В системе с архитектурой неоднородного доступа к памяти (NUMA) центральный процессор (CPU) может быть взаимосвязан посредством соединительной шины для образования многопроцессорной системы. Общей соединительной шиной является протокол высокоскоростного межсоединения типа "точка-точка" (QPI).

[0003] Однако из-за ограничения ресурсов компонентов, например, из-за ограниченного количества портов взаимосвязи процессоров использование только соединительной шины может реализовать межсоединение максимум между 8 процессорами. Для реализации межсоединения между более чем 8 процессорами нужно использовать контроллер узлов (Node Controller, NC).

[0004] Фиг. 1 показывает структуру многопроцессорной системы на известном уровне техники, включающую в себя контроллер 111 узлов, контроллер 112 узлов и 8 процессоров. Процессор 121, процессор 122, процессор 123 и процессор 124 образуют пул QPI, а процессор 125, процессор 126, процессор 127 и процессор 128 образуют другой пул QPI. Процессоры в пуле QPI могут осуществлять связь друг с другом посредством шины QPI между процессорами. Для реализации связи между процессорами в разных пулах QPI нужно использовать NC.

[0005] В процессе работы системы доступ между NC выполняется с использованием одного пути, что приводит к относительно большой задержке в системе. В случае сниженной надежности NC с низкой надежностью нужно удалить и заменить. Однако в соответствии с архитектурой на фиг. 1 во время замены NC затрагивается доступ процессора к другому пулу.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0006] Варианты осуществления настоящего изобретения предлагают архитектуру многопроцессорной системы, где процессорам доступны 2 группы NC, и процессор может выбирать группу NC, которая обеспечивает наивысшую скорость доступа к целевому NC, что повышает общую эффективность системы.

[0007] В соответствии с первым аспектом вариант осуществления настоящего изобретения предоставляет процессор, который может служить в качестве главного процессора, который управляет многопроцессорной системой, где многопроцессорная система включает в себя: первый пул с высокоскоростным межсоединением (QPI), второй пул QPI, первую группу контроллеров узлов (NC) и вторую группу NC, где первая группа NC подключается к первому пулу QPI и второму пулу QPI, вторая группа NC подключается к первому пулу QPI и второму пулу QPI, каждый пул QPI включает в себя по меньшей мере один процессор, главный процессор принадлежит первому пулу QPI или второму пулу QPI, и главный процессор конфигурируется для: управления всеми процессорами в многопроцессорной системе, которые выполняют доступ между пулами с использованием первой группы NC, когда нужно удалить NC в первой группе NC, для переключения на выполнение доступа между пулами с использованием второй группы NC путем изменения конфигурации маршрута.

[0008] Применяя этот способ, можно удалять NC оперативно, что уменьшает влияние на производительность многопроцессорной системы, вызванное удалением NC.

[0009] В первом возможном виде реализации первого аспекта главный процессор, конфигурируемый для управления всеми процессорами в многопроцессорной системе, которые выполняют доступ между пулами с использованием первой группы NC, для переключения на выполнение доступа между пулами с использованием второй группы NC путем изменения конфигурации маршрута, включает в себя, в частности: главный процессор, конфигурируемый для: указания процессорам, которые выполняют доступ между пулами с использованием первой группы NC, конфигурировать записанное состояние данных в недопустимое состояние; инициирования отключения системы, чтобы конфигурировать все процессоры в многопроцессорной системе в отключенное состояние; указания процессорам, которые выполняют доступ между пулами с использованием первой группы NC, конфигурировать порт, который находится в регистре маршрутов и который обращается к процессору в другом пуле, в порт, который выполняет доступ между пулами с использованием второй группы NC; и инициирования отмены отключения системы.

[0010] Этот вид реализации предоставляет определенный вид реализации оперативного удаления NC путем изменения конфигурации маршрута процессора.

[0011] Во втором возможном виде реализации первого аспекта главный процессор дополнительно конфигурируется для: управления по меньшей мере одним процессором, который находится в многопроцессорной системе и выполняет доступ между пулами с использованием второй группы NC, после того, как удаляется удаляемый NC, а целевой NC добавляется в первую группу NC и устанавливает топологическое взаимоотношение с исходным NC в первой группе NC, для переключения на выполнение доступа между пулами с использованием первой группы NC путем изменения конфигурации маршрута.

[0012] Этот вид реализации предоставляет технологию оперативного удаления NC. Процесс добавления NC может быть независимым решением или может объединяться с первым аспектом или первым возможным видом реализации первого аспекта для образования объединенного решения.

[0013] В третьем возможном виде реализации первого аспекта главный процессор дополнительно конфигурируется для: указания по меньшей мере одному процессору, который выполняет доступ между пулами с использованием первой группы NC, конфигурировать записанное состояние данных в недопустимое состояние после того, как удаляется удаляемый NC, а целевой NC добавляется в первую группу NC; инициирования отключения системы, чтобы конфигурировать все процессоры в многопроцессорной системе в отключенное состояние; установления топологического взаимоотношения между целевым NC и исходным NC в первой группе NC; указания по меньшей мере одному процессору конфигурировать порт, который находится в регистре маршрутов и который обращается к процессору в другом пуле, в порт, который выполняет доступ между пулами с использованием второй группы NC; и инициирования отмены отключения системы.

[0014] Это решение предоставляет более подробную технологию оперативного удаления NC.

[0015] В четвертом возможном виде реализации первого аспекта главный процессор дополнительно конфигурируется для: отправки команды по меньшей мере одному процессору, который выполняет доступ между пулами с использованием второй группы NC, после того, как целевой NC добавляется в первую группу NC, и указания по меньшей мере одному процессору установить состояния данных, соответствующие M приемным процессорам между пулами в записанных состояниях данных, в недопустимое состояние, где состояния данных, записанные процессором, соответствуют в общем N приемным процессорам между пулами, и M<N; инициирования отключения системы, чтобы конфигурировать все процессоры в многопроцессорной системе в отключенное состояние; изменения конфигурации регистра маршрутов у по меньшей мере одного процессора, чтобы конфигурировать порт, который находится в регистре маршрутов и который обращается к M процессорам, в порт, который выполняет доступ между пулами с использованием первой группы NC; и отмены отключения системы после завершения изменения конфигурации регистра маршрутов.

[0016] Применяя четвертый возможный вид реализации первого аспекта, в зависимости от различных приемных узлов, некоторые процессоры могут выбираться для изменения маршрута, а маршруты оставшихся процессоров остаются без изменений.

[0017] В соответствии со вторым аспектом предоставляется процессор, который служит в качестве главного процессора, который управляет многопроцессорной системой, где многопроцессорная система включает в себя: первый пул с высокоскоростным межсоединением (QPI), второй пул QPI, первую группу контроллеров узлов (NC) и вторую группу NC, где первая группа NC подключается к первому пулу QPI и второму пулу QPI, вторая группа NC подключается к первому пулу QPI и второму пулу QPI, каждый пул QPI включает в себя по меньшей мере один процессор, главный процессор принадлежит первому пулу QPI или второму пулу QPI, и главный процессор конфигурируется для: управления всеми процессорами в многопроцессорной системе, которые выполняют доступ между пулами с использованием целевого NC, когда нужно удалить целевой NC в первой группе NC, для переключения на выполнение доступа между пулами с использованием второй группы NC путем изменения конфигурации маршрута.

[0018] Это решение может реализовать оперативное удаление NC.

[0019] В первом возможном виде реализации второго аспекта главный процессор, конфигурируемый для управления всеми процессорами в многопроцессорной системе, которые выполняют доступ между пулами с использованием целевого NC, для переключения на выполнение доступа между пулами с использованием второй группы NC путем изменения конфигурации маршрута, включает в себя, в частности: главный процессор, конфигурируемый для: указания процессорам, которые выполняют доступ между пулами с использованием целевого NC, конфигурировать записанное состояние данных в недопустимое состояние; инициирования отключения системы, чтобы конфигурировать все процессоры в многопроцессорной системе в отключенное состояние; указания оставшимся NC в первой группе NC обновить конфигурацию маршрута, чтобы изолировать целевой NC, и указания процессорам, которые выполняют доступ между пулами с использованием целевого NC, конфигурировать порт, который находится в регистре маршрутов и который обращается к процессору в другом пуле, в порт, который выполняет доступ между пулами с использованием второй группы NC; и инициирования отмены отключения системы.

[0020] В соответствии с третьим аспектом предоставляется процессор, который служит в качестве главного процессора, который управляет многопроцессорной системой, где многопроцессорная система включает в себя: первый пул с высокоскоростным межсоединением (QPI), второй пул QPI, первую группу контроллеров узлов (NC) и вторую группу NC, где первая группа NC подключается к первому пулу QPI и второму пулу QPI, вторая группа NC подключается к первому пулу QPI и второму пулу QPI, каждый пул QPI включает в себя по меньшей мере один процессор, главный процессор принадлежит первому пулу QPI или второму пулу QPI, и главный процессор конфигурируется для:

управления по меньшей мере одним процессором, который находится в первом пуле QPI и который выполняет доступ между пулами с использованием второй группы NC, когда целевой NC добавляется в первую группу NC, для переключения на выполнение доступа между пулами с использованием целевого NC путем изменения конфигурации маршрута, где целевой NC подключается к первому пулу QPI.

[0021] В первом возможном виде реализации третьего аспекта предоставляется технология добавления NC.

[0022] В первом возможном виде реализации третьего аспекта главный процессор, конфигурируемый для управления по меньшей мере одним процессором, который находится в первом пуле QPI и который выполняет доступ между пулами с использованием второй группы NC, для переключения на выполнение доступа между пулами с использованием целевого NC путем изменения конфигурации маршрута, включает в себя, в частности: главный процессор, конфигурируемый для: указания по меньшей мере одному процессору конфигурировать состояние данных в недопустимое состояние; инициирования отключения системы, чтобы конфигурировать все процессоры в многопроцессорной системе в отключенное состояние; указания целевому NC установить топологическое взаимоотношение с исходным NC в первой группе NC; указания по меньшей мере одному процессору изменить конфигурацию маршрута, чтобы изменить порт, который находится в регистре маршрутов и который обращается к процессору в другом пуле, на порт, который выполняет доступ между пулами с использованием целевого NC; и инициирования отмены отключения системы.

[0023] В первом возможном виде реализации третьего аспекта предоставляется подробная технология добавления NC.

[0024] Во втором возможном виде реализации третьего аспекта главный процессор, конфигурируемый для управления по меньшей мере одним процессором, который находится в первом пуле QPI и который выполняет доступ между пулами с использованием второй группы NC, для переключения на выполнение доступа между пулами с использованием целевого NC путем изменения конфигурации маршрута, включает в себя, в частности: главный процессор, конфигурируемый для: отправки команды по меньшей мере одному процессору, который выполняет доступ между пулами с использованием второй группы NC, и указания по меньшей мере одному процессору установить состояния данных, соответствующие M приемным процессорам между пулами в записанных состояниях данных, в недопустимое состояние, где состояния данных, записанные процессором, соответствуют в общем N приемным процессорам между пулами, и M<N; инициирования отключения системы, чтобы конфигурировать все процессоры в многопроцессорной системе в отключенное состояние; и указания по меньшей мере одному процессору изменить конфигурацию маршрута, чтобы конфигурировать порт, который находится в регистре маршрутов и который обращается к M процессорам, в порт, который выполняет доступ между пулами с использованием целевого NC.

[0025] Во втором возможном виде реализации третьего аспекта предоставляется подробная технология добавления NC для изменения маршрутов разных приемных узлов.

[0026] Настоящее изобретение дополнительно предоставляет компьютер, где компьютер включает в себя первый пул QPI, второй пул QPI, первую группу NC и вторую группу NC, и компьютер дополнительно включает в себя BIOS, где BIOS используется для хранения команд, необходимых для работы процессоров во всех вышеупомянутых аспектах, и компьютер обеспечивает технические эффекты, аналогичные вышеупомянутым аспектам.

[0027] Настоящее изобретение дополнительно предоставляет способ управления многопроцессорной системой, который применим к главному процессору во всех вышеупомянутых аспектах или вышеупомянутому компьютеру и обеспечивает аналогичные технические эффекты.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0028] Фиг. 1 - архитектурная схема многопроцессорной системы на известном уровне техники.

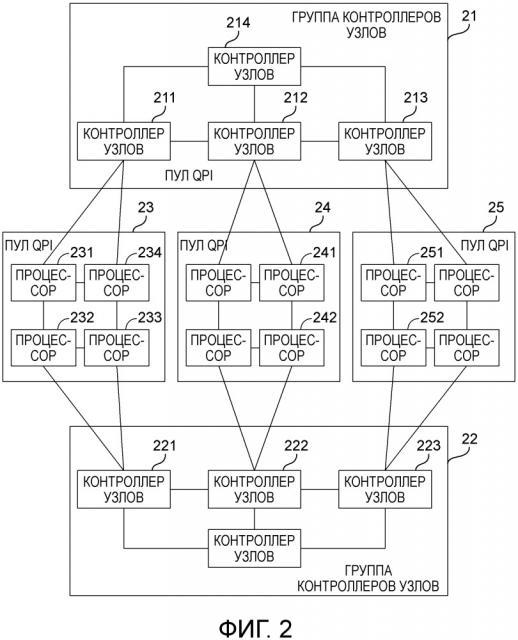

[0029] Фиг. 2 - архитектурная схема варианта осуществления многопроцессорной системы в соответствии с настоящим изобретением.

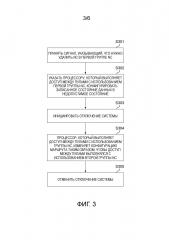

[0030] Фиг. 3 - логическая блок-схема варианта осуществления способа удаления NC в соответствии с настоящим изобретением.

[0031] Фиг. 4 - логическая блок-схема варианта осуществления способа добавления NC в соответствии с настоящим изобретением.

[0032] Фиг. 5 - логическая блок-схема другого варианта осуществления способа удаления NC в соответствии с настоящим изобретением.

[0033] Фиг. 6 - логическая блок-схема другого варианта осуществления способа добавления NC в соответствии с настоящим изобретением.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0034] Нижеследующее понятно и полностью описывает технические решения в вариантах осуществления настоящего изобретения со ссылкой на прилагаемые чертежи в вариантах осуществления настоящего изобретения. Очевидно, что описанные варианты осуществления являются лишь некоторыми, но не всеми вариантами осуществления настоящего изобретения.

[0035] В компьютере располагается многопроцессорная система, например NUMA. В многопроцессорной системе, полагаясь только на прямые соединения между процессорами, масштаб системы почти не поддается расширению, потому что количество внешних интерфейсов у процессоров ограничено. Для создания процессорной системы из большего количества процессоров разные группы процессоров обычно подключаются с использованием NC, и данные передаются между группами процессоров с использованием NC.

[0036] Группа NC также называется плоскостью NC и состоит из одного или нескольких NC. Несколько NC в одной и той же группе NC могут быть взаимосвязаны по способу полного зацепления (full mesh), кольцевой схемы или последовательного соединения. Группа процессоров также называется пулом QPI, и пул QPI состоит из одного или нескольких процессоров. Несколько процессоров в одном и том же пуле QPI подключаются с использованием шины QPI. Группа NC подключается к группе процессоров.

[0037] Процессоры в группе процессоров не только взаимосвязаны с использованием шины QPI, но также могут быть взаимосвязаны с использованием другой кэш-когерентной (Cache Coherency, CC) шины, например высокопроизводительной шины (Hyper-Transport, HT). Поэтому группа процессоров также может называться кэш-когерентным пулом. Для простоты описания варианты осуществления настоящего изобретения описываются в качестве примера с использованием пула QPI.

[0038] В вариантах осуществления один порт процессора подключается к NC, а оставшиеся порты подключаются к другим процессорам в пуле. Группа NC может перенаправлять пакет между пулами QPI, и поэтому процессоры в разных пулах QPI могут реализовать пакетную передачу с использованием группы NC.

[0039] При необходимости каждый процессор содержит несколько портов, где один из портов подключается к NC, а оставшиеся порты подключаются к процессорам в текущем пуле QPI. Например, процессор содержит 3 порта, один из портов подключается к NC, а оставшиеся два порта подключаются к соседним процессорам. Линия соединения между процессором и NC также является линией соединения между процессором и группой NC. Группа NC обеспечивает функцию перенаправления, и процессор осуществляет связь с процессорами в других пулах QPI с использованием линии, подключенной к группе NC.

[0040] В процессе использования NC надежность может уменьшаться, и даже может возникнуть сбой. Если NC в неисправном состоянии, то может быть оказано определенное влияние на полосу пропускания при обращении к процессору в многопроцессорной системе. Для повышения надежности многопроцессорной системы идеальная многопроцессорная система должна поддерживать оперативную замену NC. Рабочее состояние многопроцессорной системы контролируется с использованием управляющего программного обеспечения. Если обнаружена нестабильная работа NC, например, частота или количество раз возникновения сбоя у NC в периоде времени превышает некую пороговую величину, то NC помечается рискованным. Кроме того, перед тем как NC становится недоступным, рискованный NC заменяется путем оперативного удаления рискованного NC, а затем оперативного добавления нового NC, чтобы предотвратить критическое влияние на систему, вызванное внезапным отказом NC.

[0041] Оперативная замена относится к замене без перебоя питания и позволяет пользователю заменить соответствующую часть без выключения системы и без отключения источника питания. В частности, оперативная замена включает в себя два процесса: оперативное удаление и оперативное добавление.

[0042] В этом варианте осуществления настоящего изобретения несколько пулов QPI подключаются к одним и тем же нескольким группам NC. Конфигурация маршрута хранится в NC и в регистре процессоров, и путь передачи пакетов можно изменить путем изменения конфигурации маршрута. При операции взаимного доступа между процессорами для описания последовательности операций доступа используется транзакция. Процессор, который инициирует транзакцию доступа (отправляет запрос доступа), называется исходным процессором, а процессор, который отвечает на транзакцию (отвечает на запрос доступа), называется приемным процессором. В процессе обработки транзакций канал для передачи данных между исходным процессором и приемным процессором называется маршрутом. Направление передачи пакета данных противоположно направлению маршрута транзакции, где приемный процессор является отправителем пакета данных, а исходный процессор является приемником пакета данных. Направление передачи пакета запроса совпадает с направлением маршрута транзакции, где исходный процессор отправляет пакет запроса данных, а приемный процессор отвечает на пакет запроса данных.

[0043] Фиг. 2 - архитектурная схема в соответствии с вариантом осуществления настоящего изобретения. Пул 23 QPI, пул 24 QPI и пул 25 QPI подключаются к группе 21 NC и группе 22 NC. Любой процессор может обращаться к процессорам в других пулах QPI с использованием группы 21 NC или группы 22 NC. Тот же процессор также может обращаться к разным процессорам в других пулах с использованием разных групп NC. Упомянутый в этом варианте осуществления настоящего изобретения доступ может быть, например, считыванием данных из других процессоров в виде пакета. В частности, данные считываются из запоминающего устройства, управляемого другими процессорами.

[0044] В многопроцессорной системе один процессор служит в качестве главного процессора. Главный процессор управляет и контролирует NC и другие процессоры, и главный процессор может располагаться в любом пуле QPI. Главный процессор формирует команду управления и контроля путем выполнения программы. Программу можно получить из BIOS компьютера. BIOS подключается к многопроцессорной системе, и многопроцессорная система и BIOS являются неотъемлемыми частями компьютера.

[0045] То есть процессоры в пуле QPI могут обращаться друг к другу без использования NC. Например, на фиг. 2, если процессору 231 нужно обратиться к процессору 234, то имеется несколько необязательных маршрутов, включающих в себя: процессор 231 - процессор 232 - процессор 233 - процессор 234, процессор 231 - процессор 234 и процессор 231 - NC 211 - процессор 234. Однако процессорам в разных пулах QPI нужно обращаться друг к другу с использованием группы NC. Если процессор 231 обращается к процессору 241, то необязательным путем доступа является процессор 231 - NC 211 - NC 212 - процессор 241, или может выбираться следующий путь доступа: процессор 231 - процессор 232 - NC 221 - NC 222 - процессор 242 - процессор 241. Первый проходит через группу 21 NC, а последний проходит через группу 22 NC.

[0046] В варианте осуществления настоящего изобретения многопроцессорная система включает в себя: по меньшей мере два пула с высокоскоростным межсоединением (QPI), первую группу NC и вторую группу NC. Каждый пул QPI включает в себя по меньшей мере один процессор, и каждая группа NC включает в себя по меньшей мере один NC. Каждый NC подключается ко всем пулам QPI.

[0047] В многопроцессорной системе процессор может отправлять запрос доступа первой группе NC в соответствии с конфигурацией маршрута процессора при обращении к первому приемному процессору в другом пуле QPI, где первая группа NC используется для перенаправления запроса доступа первому приемному процессору во втором пуле QPI. Тем не менее процессор может отправлять запрос доступа первой группе NC в соответствии с конфигурацией маршрута процессора при обращении ко второму приемному процессору в другом пуле QPI, где первая группа NC используется для перенаправления запроса доступа второму приемному процессору во втором пуле QPI.

[0048] Процессор, который обращается к первому приемному процессору с использованием первой группы NC, может быть таким же или отличаться от процессора, который обращается ко второму приемному процессору с использованием второй группы NC.

[0049] Нижеследующее кратко описывает изменение, вызванное удалением и добавлением NC в систему, когда выполняется связь между процессорами, которые принадлежат разным пулам QPI.

[0050] Например, этот вариант осуществления настоящего изобретения предоставляет два решения, когда нужно удалить NC 211 в группе 21 NC. Оба способа выполняются под управлением главного процессора. Один способ состоит в переключении всех маршрутов, которые исходно проходят через группу 21 NC, на группу 22 NC, а другой способ состоит в переключении маршрутов, которые исходно проходят через NC 211, на группу 22 NC, а маршруты, которые проходят через другие NC в группе 21 NC, остаются без изменений.

[0051] Аналогичным образом также существует несколько решений, когда нужно добавить NC под управлением главного процессора, например, после того как удаляется исходный NC 211, новый NC 211 добавляется в группу 21 NC. Один способ: в зависимости от разных исходных процессоров, которые инициируют доступ между пулами, главный процессор выбирает некоторые из маршрутов, которые проходят через группу 22 NC, и переключает выбранные маршруты на группу 21 NC, а оставшиеся маршруты остаются без изменений. Другой способ: в зависимости от разных приемных процессоров, к которым обращаются между пулами, главный процессор выбирает маршруты, соответствующие некоторым приемным процессорам, из маршрутов, которые исходно проходят через группу 22 NC, и переключает выбранные маршруты на группу 21 NC, а оставшиеся маршруты остаются без изменений. Еще один способ состоит в переключении на группу 21 NC всех маршрутов, которые проходят через группу 22 NC.

[0052] Доступ между пулами означает, что процессор, к которому обращаются, и процессор, который отправляет запрос доступа, не находятся в одном пуле QPI, и в частности, адрес памяти, к которому обращаются, является адресом памяти, управляемым процессором в другом пуле QPI. Запрос доступа используется одним процессором для запроса данных у другого процессора. Следует отметить, что если запрос доступа в доступе между пулами проходит через любой NC в группе NC, то доступ между пулами считается проходящим через группу NC. То, что процессор выполняет доступ между пулами с использованием одной группы NC (или NC), означает, что в конфигурации маршрута у процессора прямо или косвенно указывается группа NC или NC. Это не обязательно означает, что в текущий момент времени существует доступ между пулами. Однако когда процессор отправляет запрос доступа между пулами, запрос доступа может проходить через группу NC или NC.

[0053] Прямое указание на NC является, например, прямым подключением к NC, на который указывают. В конфигурации маршрута процессора следующим узлом является NC, на который указывают. Когда процессор отправляет запрос доступа между пулами, в соответствии с конфигурацией маршрута процессора следующим узлом, через который проходит запрос доступа между пулами, является NC, на который указывают. Косвенное указание на NC является, например, прохождением сначала через другой узел (например, NC или процессор), а затем подключение к NC, на который указывают. Когда процессор отправляет запрос доступа между пулами, в соответствии с конфигурацией маршрута процессора запрос доступа между пулами может сначала проходить через другие узлы, а затем поступать в NC, на который указывают. Предшествующее описывает принципы прямого или косвенного указания на NC, а принципы прямого или косвенного указания на группу NC одинаковы.

Вариант 1 осуществления

[0054] Ссылаясь на фиг. 3, этот вариант осуществления настоящего изобретения предоставляет способ оперативного удаления NC. Этот способ описывается на основе архитектуры на фиг. 2.

[0055] Когда нужно удалить NC в первой группе NC, главный процессор управляет всеми процессорами в многопроцессорной системе, которые выполняют доступ между пулами с использованием первой группы NC, для переключения на выполнение доступа между пулами с использованием второй группы NC.

[0056] Предположим, что главным процессором является процессор 234 в пуле 23 QPI, а удаляемым NC является NC 211. Для простоты описания удаляемый NC 211 в этом варианте осуществления называется целевым NC, группа 21 NC называется первой группой NC, а группа 22 NC называется второй группой NC.

[0057] S301. Главный процессор принимает сигнал, указывающий, что нужно удалить NC в первой группе NC.

[0058] Для примера, когда пользователь готов удалить NC 211, пользователь может отправить главному процессору 234 команду удаления с использованием операционной системы, где команда удаления включает в себя идентификатор NC 211. Таким образом, при приеме команды удаления главный процессор 234 может определить, что удаляемый NC существует в группе 21 NC.

[0059] Для примера после обнаружения, что снизилась надежность NC 211 в группе 21 NC, процессор 234 может начать удаление NC 211. NC 211 можно удалить после того, как маршрут, который проходит через группу 21 NC, переключается на группу 22 NC, и прекращается использование группы 21 NC.

[0060] S302. Главный процессор указывает процессору, который выполняет доступ между пулами с использованием первой группы NC, конфигурировать записанное процессором состояние данных в недопустимое состояние.

[0061] Главный процессор может узнать топологическое взаимоотношение между процессорами в многопроцессорной системе, или другими словами, главный процессор знает взаимосвязи соединений между разными портами каждого процессора и другими устройствами (NC или процессором). Поэтому путем считывания информации об исходящих портах в конфигурации маршрута процессора главный процессор может узнать, является ли группа NC, используемая процессором для доступа между пулами, первой группой NC. Соответственно, если главный процессор указывает другому процессору изменить исходящий порт в конфигурации маршрута, то можно изменить путь, используемый процессором для внешнего доступа (ссылаясь на последующий этап S304). Конфигурация маршрута записывается в кэш процессора.

[0062] Например, главный процессор записывает, что: если процессору 231 нужно обратиться к процессору (например, процессору 241) в другом пуле с использованием группы 21 NC, то порт, который нужно использовать, является портом, подключенным к NC 211, среди 3 портов процессора 231; если процессору 231 нужно обратиться к процессору (например, процессору 241) в другом пуле с использованием группы 22 NC, то порт, который нужно использовать, является портом, указывающим на NC 221, среди 3 портов процессора 231, то есть портом между процессором 231 и процессором 232. Если первым является порт, сконфигурированный в настоящее время процессором 231 для обращения к другому пулу, то это означает, что процессор 231 выполняет доступ между пулами с использованием первой группы NC. В соответствии с этим способом можно получить все процессоры в многопроцессорной системе, которые выполняют доступ между пулами с использованием первой группы NC.

[0063] Например, главный процессор может записать в кэш исходящие порты, используемые каждым процессором для обращения к разным адресам памяти. После считывания кэша главного процессора главный процессор может узнать, какие процессоры используют первую группу NC для выполнения доступа между пулами. В качестве альтернативы независимое управляющее устройство может записывать такую информацию и предоставлять информацию для главного процессора.

[0064] Используя фиг. 2 в качестве примера, когда процессор 231 обращается к адресу памяти, который не находится в пуле процессора 231, используется порт, который подключается к NC 211 и который находится в процессоре 231. Процессор включает в себя ядро, агент кэша (Cache Agent, CA) и домашний агент (Home Agent, HA). CA управляет кэшем, а HA управляет запоминающим устройством. Когда требуются данные, ядро процессора сначала использует CA ядра процессора для поиска в кэше, управляемом CA, а если данные не найдены, использует HA для поиска в запоминающем устройстве, управляемом HA.

[0065] HA, который предоставляет данные, и ядро, которое отправляет запрос доступа, могут располагаться в одном процессоре или в разных процессорах. Этот вариант осуществления описывает HA, который предоставляет данные, и придает значение HA, расположенному в другом пуле QPI.

[0066] В этом варианте осуществления настоящего изобретения состояние данных процессора относится к состоянию данных, которые находятся в кэше процессора и которые получены процессором. Состояние данных записывается в кэш процессора и управляется посредством CA.

[0067] Если процессор когда-либо обращался к данным другого процессора (в частности, данные могут быть данными в запоминающем устройстве, управляемом HA другого процессора), то процессор, который инициирует доступ, может записать текущее состояние полученных данных. В характерном процессе пакетной передачи исходный процессор инициирует доступ, а приемный процессор предоставляет пакет. В частности, приемный процессор получает данные из запоминающего устройства с использованием HA приемного процессора, а затем предоставляет данные для исходного процессора. Состояние данных, записанное процессором, является состоянием данных (например, пакета), которые получены процессором, когда процессор служит в качестве исходного процессора, и состояние данных соответствует приемному процессору, к которому запрашивается доступ. В соответствии с кэш-когерентным протоколом (cache coherency protocol) исходный процессор запроса доступа после получения нужных данных записывает состояние полученных данных в свой кэш. Состояния включают в себя: эксклюзивное (Exclusive, E) состояние, недопустимое (Invalid, I) состояние, совместно используемое (Share, S) состояние и измененное (Modify, M) состояние. Эти состояния отмечаются по адресу памяти (строка кэша). Адрес памяти может дополнительно записывать адрес данных в запоминающем устройстве.

[0068] Состояние M указывает, что данные, отмеченные по адресу памяти, изменены (недействительны) исходным процессором и расходятся с исходными данными, предоставленными приемным процессором. После того как измененные данные записываются обратно в запоминающее устройство, состояние по адресу памяти можно поменять на состояние E. Состояние E указывает, что данные, отмеченные по адресу памяти, не изменены (достоверные) и согласуются с данными в запоминающем устройстве. Состояние S означает, что данные, отмеченные по адресу памяти, могут быть буферизованы несколькими процессорами, и данные во всех кэшах согласуются с данными в запоминающем устройстве. Состояние I указывает, что данные недействительны, например, другой процессор мог изменить данные, отмеченные по адресу памяти.

[0069] NC также может записывать состояния данных. Когда процессор передает пакет между пулами и когда пакет между пулами проходит через NC, NC записывает состояние данных, чтобы записанное NC состояние данных оставалось согласованным с состоянием данных, записанным исходным процессором пакета. При последующем доступе между пулами другой процессор может узнать состояние данных процессора с использованием NC, что быстрее по сравнению с практикой получения состояния данных от процессора.

[0070] В этом варианте осуществления конфигурацию маршрута у всех процессоров, которые обратились к другим пулам с использованием группы 21 NC, нужно изменить для указания на группу 22 NC, а не на группу 21 NC. Поскольку такие процессоры не служили в качестве исходного процессора для приема пакета с использованием группы 22 NC, в NC не записывается никакое соответствующее состояние данных. То есть в записи состояния у NC соответствующим состоянием данных является состояние I. Путем изменения состояния, записанного в процессорах, которые отправляют пакеты с использованием группы 21 NC, на состояние I можно сохранить согласованными состояния данных между NC и процессорами.

[0071] Необязательный вид реализации конфигурирования состояния данных, записанного процессорами, которые выполняют доступ между пулами с использованием первой группы NC, в недопустимое состояние включает в себя две части. Первая часть: Главный процессор указывает процессорам удалить данные, буферизованные процессорами, чтобы состояние M данных в процессорах поменялось на состояние I, где очистка кэша может относиться, в частности, к возврату буферизованных данных в запоминающее устройство, которое предоставляет данные. Вторая часть: Главный процессор указывает NC в первой группе NC сбросить состояние данных, записанное NC, чтобы состояние S и состояние E, записанные в NC, поменялись на состояние I, и состояние S и состояние E процессора соответственно также поменялись на состояние I. Две части операций инициируются главным процессором с использованием команд. Нижеследующее предоставляет конкретную интерпретацию.

[0072] Первая часть: Ядро процессора исполняет команду очистки кэша и, соответственно, записывает данные в измененном состоянии, записанном в процессоре, в запоминающее устройство, а затем меняет состояние данных с измененного на недопустимое. К тому же в процессе записи данных в запоминающее устройство данные могут проходить через NC в первой группе NC. NC в первой группе NC также изменяет соответствующее состояние справочника, записанное кэшем справочника в NC, с измененного на недопустимое, которое остается согласованным с записанным в процессоре состоянием справо