Патент ссср 265935

Иллюстрации

Показать всеРеферат

О Й И СА Н И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

265935

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №вЂ”

Заявлено 06.11.1968 (№ 1215947/26-9) с присоединением заявки №вЂ”

Приоритет

Кл, 21а1, 13/03

МПК Н 04l 7/02

УДК 621.394.662.2 (088.8) Комитет по делам иаобретений и открытий при Совете Министров

СССР

Опубликовано 17.111.1970. Бюллетень № 11

Дата опубликования описания 2Л 1П970

Авторы изобретения

Л. М, Рахович и А, В. Танько

Заявитель

Одесский электротехнический институт связи им. А, 1;.-",ИОХЕ1(А

УСТРОЙСТВО ДЛЯ ПОЛУЧЕНИЯ СИГНАЛОВ НАСТРОЙКИ

СИНХРОНИЗАЦИИ ГРАНИЦ ПОСЫЛОК В МНОГОКАНАЛЬНЫХ

СИСТЕМАХ СВЯЗИ С ОРТОГОНАЛЬНЫМИ

СИНУСОИДАЛЬНЫМИ СИГНАЛАМИ

Известны устройства для получения сигналов настройки синхронизации границ посылок в многоканальных системах связи с ортогональными синусоидальными сигналами, содержащие интегратор, блок сравнения напряжений, блок управления и блок, памяти номера конденсатора.

Однако известные устройства сложны по схемному решению и непригодны для использования в многоканальных системах с «гибридными» видами модуляции, например с фазовой и амплитудной модуляцией.

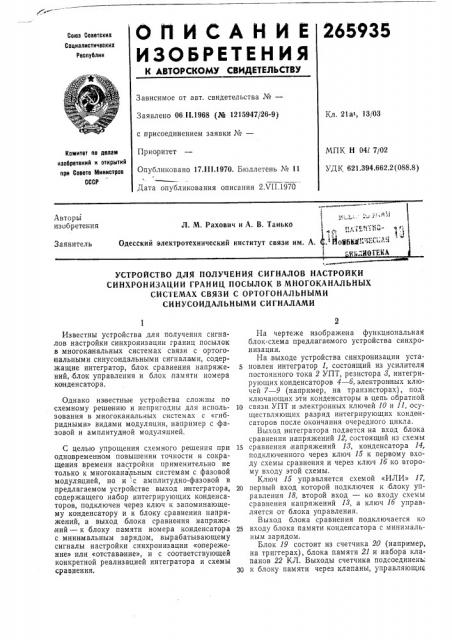

С целью упрощения схемного решения при одновременном повышении точности и сокращения времени настройки применительно не только к многоканапьным системам с фазовой модуляцией, но и с амплитудно-фазовой в предлагаемом устройстве выход интегратора, содержащего набор интегрирующих ко нденсаторов, подключен через ключ к запоминающему конденсатору и к блоку сравнения напряжений, а выход блока сравнения напряжений — к блоку памяти номера конденсатора с минимальным зарядом, вырабатывающему сигналы настройки синхронизации «опережение» или «отставание», и с соответствующей конкретной реализацией интегратора и схемы сравнения, На чертеже изображе|на функциональная блок-схема предлагаемого устройства синхро.низации и.

На .выходе устройства синхронизации устаs новлен интегратор 1, состоящий из усилителя постоянного тока 2 УПТ, резистора 8, интегрирующих конденсаторов 4 — б, электрон ных ключей 7 — 9 (например, на транзисторах), подключающих эти конденсаторы в цепь обратной

1р связи УПТ и электронных ключей 10 и 11, осуществляющих разряд интегрирующих конденсаторов после окончания очередного цикла.

Выход интегратора подается на вход блока сравнения напряжений 12, состоящий из схемы

lь сравнения напряжений 18, конденсатора 14, подключенного через ключ 15 к пер вому входу схемы сравнения и через ключ 1б ко второму входу этой схемы.

Ключ 15 управляется схемой «ИЛИ» 17, 20 первый вход которой подключен к блоку управления 18, второй вход — ко входу схемы сравнения напряжений 1у, а ключ 1б управляется от блока управления.

Выход блока сравнения подключается ко

25 входу блока памяти конденсатора с минимальным зарядом.

Блок 19 состоит из счетчика 20 (например, на триггерах), блока памяти 21 и набора клапанов 22 КЛ. Выходы счетчика подсоединень;

3р к блоку памяти через клапаны, управляющие

265935 входы которых связаны с выходом блока сравнения. Счетный и установочные входы счетчика 20, а также установочные входы и входы блока памяти 21 соединены с блоком управления.

Принцип работы устройства основан на сравнении двух отсчет ных значений сигнала, взятых на интервале ортогональности.

Устройство работает следующим образом.

Сигнал подается на вход, интегратора. Ключи

7 — 9 подсоединяют к интегратору один из конде нсаторов 4, 5 или б, в которых образуется напряжение, соответствующее величине интегралов. Так, на интервале от t> до 4+Ai замкнут ключ 7, а на интервале от / до l +Л1 замкнут ключ 8 и т. д., где t и 4 — момент начала интегрирования соответствс ., ого и второго отсчета, Л(— интервал интегрирования.

Через время Т снова замыкается ключ 7, который замкнут в течение промежутка от

4+T до t,+T+Ì, затем замыкается ключ 8 и т. д. При этом на выходе и нтегратора получаются напряжения, соответствующие значениям напряжения Х>, Х и т. д. (Х, — суммы интегралов) .

В схеме сравнения определяется наименьшее Х„„„значение Х, .

Определение Х„„„производится следующим образом. Сначала в конденсагор записывается значение Х„поступающее из интегратора в момент t +At+Т благодаря замыканию ключа 15 сигналом из блока управления, проходящим через схему «ИЛИ» 17.

Следующее значение Х, поступающее из интегратора в момент 4+11+ 1, сравнивается с напряжением Х„хранящимся в конденсаторе, благодаря замыканию в этот момент ключа 15 импульсом из блока управления. Если

Xq(X>, то на выходе схемы сравнения напряжения появляется сигнал, .поступающий в блок памяти Х„„„и через схему «ИЛИ» 17 на управляющий вход ключа 15, который замыкается, и значение напряжения Х> записывается .в конденсаторе. Если же Х,)Х„то в конденсаторе остается прежнее значение напряжения.

Напряжения значения Х. и т. д. обрабатываются в блоке сравнения аналогично. Определение номера конденсатора с напряжением

Х„„„в блоке 19 происходит следующим образом.

К началу каждого никла сравнения, т. е. к моменту 1 +А/ —, T счетчик находится в нулевом положении, а в блок памяти записана единица.

Счетчик продвигается на единицу при подключении к схеме сравнения очередного конденсатора интегратора. Если окажется, что напряжение на подключенном конденсаторе меньше предыдущего, то блок сравнения выдает импульс, отпирающий клапаны, и положение счетчика перезаписывается в блок памяти.

15 го

Таким образом, в конце цикла сравнения в блоке памяти окажется зафиксирова нным номер конденсатора интегратора с минимальным зарядом.

Настройка синхронизации по сигналам предлагаемого устройства производится следующим образом. Начало интегрирования канальных сигналов в приемнике совпадает с началом интегрирования в конденсаторе, 5. Если в блок памяти записано число, отличное от значения «два» (порядкового номера среднего в наборе конденсатора), то блок выдает сигнал подстройки синхронизации границ посылок

«запаздывания» или «опережения» в блок управления в зависимости от X,„„ . Если X„„„ меньше «двух». то выдается сигнал «опережение», по и йро пу синхронизация установит более позднее начало интегрирования путем сдвига счетной схемы в блоке управления на соответствующее число, шагов назад. Если

Х,„„больше «двух», то происходит обратный процесс.

Количество и нтегрирующих конденсаторов можно взять любым, но не малым, причем, чем их больше, тем точнее можно установить границы посылок.

При любом количестве интегрирующих конденсаторов время подстройки всегда остается одинаковым и равным примерно длительности двух посылок, так как по номеру, зафиксированному в блоке памяти в конце одного цикла однозначно, устанавливается направление и число шагов подстройки, которая производится в блоке управления.

Предмет изобр ете н ия

1. Устройство для получения сигналов настройки синхронизации границ посылок в многоканальных системах связи с ортогональными синусоидальными сигналами, содержащее интегратор, блок сравнения напряжений, блок управления и блок памяти номера конденсатора, отличающееся тем, что, с целью упрощения схемного решения при одновременном повышении точности и сокращении времени настройки применительно не только к многоканальным системам с фазовой модуляцией, но и с амплитудно-фазовой модуляцией, выход интегратора подключен через ключ к запоминающему конденсатору и к блоку сравнения напряжений, а выход последнего соединен с блоком памяти номера конденсатора с ми нимальным зарядом, имеющим выходы для сигналов настройки синхронизации «опережение» или

«отставание».

2. Устройство по п. 1, отличающееся тем, что интегратор содержит усилитель:постоянного тока с набором интегрирующих конденсаторов, подключаемых в цепь обратной связи через ключи, соединенным по цепям управления . блоком управления.

3. Устройство по п. 1, отличающееся тем, что блок сравнения напряжений содержит схему сравнения с запоминающим конденсатором, 265935

Составитель Л. Рубинчик

Техред Т. П. Курилко Корректор Л. И. Гаврилова

Редактор Т. И. Морозова

Заказ 1655/4 Тираж 480 Подписное

ЦНИИПИ Коми1ета по делам изобретений и открьппй при Совете Министров СССР

Москва Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 подключаемым к ее второму входу ключом, а выход схемы сравнения соединен непосредственно со входом блока памяти номера конденсатора и через схемы «ИЛИ» — с управляющим входом ключа подключения выхода интегратора к запоминающему конденсатору.