Команда и логическая схема для сортировки и выгрузки команд сохранения

Иллюстрации

Показать всеГруппа изобретений относится к логическим схемам обработки и может быть использована для осуществления логических, математических функциональных операций. Техническим результатом является повышение пропускной способности и улучшение производительности. Процессор содержит логическую схему для исполнения потока команд с измененным порядком. Поток команд делят на множество нитей и их команды и команды в потоках упорядочивают в соответствии с программным порядком (PO). Процессор дополнительно содержит логическую схему для идентификации самой старой, неотправленной команды в потоке команд и записи ее соответствующего значения PO как указателя исполненной команды, для идентификации наиболее недавно зафиксированной команды сохранения в потоке команд и для записи ее соответствующего значения РО в качестве указателя фиксации команд сохранения указателя поиска со значением РО, меньшим указателя исполняемой команды, для идентификации первого набора команд сохранения в буфере команд сохранения со значениями РО, меньшими указателя поиска, и подходящих для фиксации, для оценки, больше ли первый набор команд сохранения количества портов считывания буфера команд сохранения, и для регулировки указателя поиска. 3 н. и 17 з.п. ф-лы, 34 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение касается области логических схем обработки, микропроцессоров и связанной архитектуры набора команд, которые при исполнении процессором или другой логической схемой обработки осуществляют логические, математические или другие функциональные операции.

Уровень техники

Многопроцессорные системы становятся все более обычными системами. Приложения многопроцессорных систем включают в себя динамическое разбиение на области вплоть до настольных вычислений. Для того чтобы воспользоваться преимуществами многопроцессорных система исполняемый код может быть разделен на множество цепочек для исполнения различными обрабатывающими объектами. Каждая цепочка может быть исполнена параллельно другой. Более того, для увеличения использования обрабатывающего объекта может быть применен измененный порядок исполнения команд. При измененном порядке исполнения, команды могут быть исполнены тогда, когда станет доступен вход, нужный для таких команд. Таким образом, команда, которая появилась позже в последовательности кода может быть исполнена до команды, появившейся в последовательности кода раньше.

Краткое описание чертежей

Варианты осуществления изобретения показаны в качестве примера и не ограничены фиг. с приложенных чертежей:

фиг. 1А - вид, показывающий структурную схему примера вычислительной системы, выполненной с процессором, который может содержать блоки исполнения для исполнения команды, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 1В - вид, показывающий систему обработки данных, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 1С - вид, показывающий другие варианты осуществления системы обработки данных для выполнения операций сравнения текстовых строк;

фиг. 2 - вид, показывающий структурную схему микроархитектуры для процессора, которая может содержать логические схемы для выполнения команд, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 3А - вид, показывающий различные представления типа данных «упакованные данные» в мультимедийных регистрах, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 3В - вид, показывающий возможные форматы хранения данных в регистре, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 3С - вид, показывающий различные представления типа данных «упакованные данные» со знаком и без знака в мультимедийных регистрах, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 3D - вид, показывающий один вариант осуществления формата кодирования операций;

фиг. 3E - вид, показывающий другой возможный формат кодирования операций, содержащий сорок и более битов, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 3F - вид, показывающий еще один возможный формат кодирования операций, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 4A - вид, показывающий структурную схему, иллюстрирующую конвейер с исполнением команд по очереди и конвейер с измененным порядком исполнения/выдачи команд, со ступенью переименования регистров, в соответствии с вариантами осуществления изобретения;

фиг. 4В - вид, показывающий структурную схему, иллюстрирующую архитектуру ядра с исполнением команд по очереди и подлежащую вхождению в процессор логическую схему с измененным порядком исполнения/выдачи команд и логическую схему переименования регистров, в соответствии с вариантами осуществления изобретения;

фиг. 5А - вид, показывающий структурную схему процессора, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 5В - вид, показывающий структурную схему одного примера реализации ядра, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 6 - вид, показывающий структурную схему одной системы, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 7 - вид, показывающий структурную схему второй системы, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 8 - вид, показывающий структурную схему третьей системы, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 9 - вид, показывающий структурную схему системы-на-кристалле, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 10 - вид, показывающий процессор, содержащий центральный обрабатывающий блок и блок обработки графики, который может выполнить, по меньшей мере, одну команду, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 11 - вид, показывающий структурную схему, иллюстрирующую развитие IP-ядер, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 12 - вид, показывающий, как команда первого типа может быть эмулирована процессором другого типа, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 13 - вид, показывающий структурную схему, иллюстрирующую использование программного устройства преобразования команд для преобразования двоичных команд исходного набора команд в двоичные команды целевого набора команд, в соответствии с вариантами осуществления изобретения;

фиг. 14 - вид, показывающий структурную схему одной архитектуры набора команд процессора, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 15 - вид, более подробно показывающий структурную схему одной архитектуры набора команд процессора, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 16 - вид, показывающий структурную схему конвейера исполнения для процессора, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 17 - вид, показывающий структурную схему электронного устройства для использования процессора, в соответствии с вариантами осуществления настоящего изобретения;

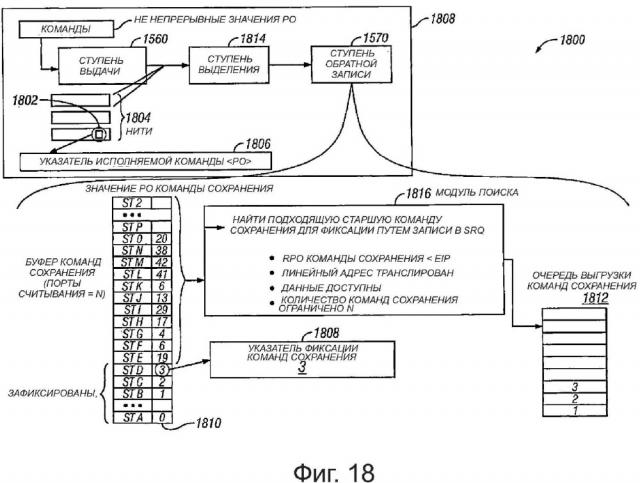

фиг. 18 - вид, показывающий пример системы для выгрузки и сортировки команд сохранения, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 19 - вид, показывающий ограничения, накладываемые на работу модуля поиска, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 20 - вид, показывающий пример работы модуля поиска с учетом ограничений, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 21А, 21В и 21C - вид, показывающий пример работы модуля поиска, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 22 - вид, показывающий пример работы модуля поиска по предсказанию или установке указателей поиска, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 23 - вид, показывающий пример варианта осуществления способа поиска и упорядочивания команд сохранения, в соответствии с вариантами осуществления настоящего изобретения.

Подробное описание изобретения

Далее описана команда и логическая схема обработки, для сортировки и выгрузки команд сохранения в процессоре или со связью с процессором, виртуальным процессором, пакетом, компьютерной системой или другим устройством обработки. Такое устройство обработки может содержать процессор с измененным порядком исполнения команд. Более того, такое устройство обработки может содержать многопоточный процессор с измененным порядком исполнением команд. Кроме того, сортировка и выгрузка команд сохранения может быть выполнена из неупорядоченного буфера, такого как буфер команд сохранения. В последующем описании, для обеспечения более глубокого понимания вариантов осуществления настоящего изобретения изложено большое количество конкретных деталей, таких как логическая схема обработки, типы процессоров, микроархитектурные условия, события, механизмы реализации и подобное. Тем не менее, специалистам в рассматриваемой области следует понимать, что варианты осуществления изобретения могут быть реализованы без подобных конкретных деталей. Дополнительно, некоторые хорошо известные структуры, схемы и подобное не показаны подробно, чтобы не создавать ненужные помехи пониманию вариантов осуществления настоящего изобретения.

Хотя приведенные ниже варианты осуществления изобретения описаны со ссылкой на один процессор, другие варианты осуществления изобретения применимы к другим типам интегральных схем и логических устройств. Аналогичные технологии и идеи вариантов осуществления настоящего изобретения могут быть применены в других типах схем или полупроводниковых устройств, которые могут получить пользу от более высокой пропускной способности конвейера и улучшенной производительности. Идеи вариантов осуществления настоящего изобретения применимы в любом процессоре или машине, которые осуществляют манипуляции с данными. Тем не менее, варианты осуществления изобретения не ограничены процессорами или машинами, которые выполняют операции с 512-битовыми, 256-битовыми, 128-битовыми, 64-битовыми, 32-битовыми или 16-битовыми данными, и могут быть применены в любом процессоре и машине, в которых могут быть выполнены манипуляции с данными или управление данными. Кроме того, в последующем описании приведены примеры и с иллюстративными целями на приложенных чертежах показаны различные примеры. Тем не менее, эти примеры не должны рассматриваться как ограничения, так как они приведены как примеры вариантов осуществления настоящего изобретения, а не для предоставления исчерпывающего списка всех возможных реализаций вариантов осуществления настоящего изобретения.

Хотя в приведенных ниже примерах описана обработка команд и их распределение в случае блоков исполнения и логических схем, другие варианты осуществления настоящего изобретения могут быть реализованы с помощью данных или команд, которые сохранены на считываемом машиной, материальном носителе и которые, при их выполнении машиной, побуждают машину выполнять функции, согласующиеся, по меньшей мере, с одним вариантом осуществления изобретения. В одном варианте осуществления изобретения функции, связанные с вариантами осуществления настоящего изобретения, реализованы в исполнимых машиной командах. Команды могут быть использованы для того, чтобы побудить процессор общего назначения или процессор специального назначения, который может быть запрограммирован этими командами, выполнить этапы настоящего изобретения. Варианты осуществления настоящего изобретения могут быть предоставлены как компьютерный программный продукт или программное обеспечение, которое может содержать считываемой машиной или компьютером носитель, на котором сохранены команды, которые можно использовать для программирования компьютера (или другого электронного устройства) с целью выполнения одной или нескольких операций, соответствующих вариантам осуществления настоящего изобретения. Более того, этапы вариантов осуществления настоящего изобретения могут быть выполнены с помощью специальных аппаратных компонентов, которые содержат логическую схему фиксированного назначения для выполнения этих этапов, или с помощью любой комбинации программируемых компонентов компьютера и аппаратных компонентов фиксированного назначения.

Команды, используемые для программирования логической схемы для выполнения вариантов осуществления настоящего изобретения, могут храниться в памяти системы, такой как DRAM, кэш-память, флеш-память или другое запоминающее устройство. Более того, команды могут быть распределены по сети или распределены с помощью других считываемых компьютером носителей. Таким образом, считываемый машиной носитель может являться любым механизмом для хранения или передачи информации в форме, считываемой машиной (например, компьютером), такой как, помимо прочего, гибкие диски, оптические диски, компакт-диски (CD-ROM) постоянного запоминающего устройства и магнитооптические диски, постоянное запоминающее устройство (ROM), оперативное запоминающее устройство (RAM), стираемое программируемое постоянное запоминающее устройство (EPROM), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM), магнитные или оптические карты, флеш-память или материальное, считываемое машиной запоминающее устройство, используемое при передаче информации по сети Интернет с помощью электрических, оптических, акустических или других форм распространяющихся сигналов (например, несущих волн, инфракрасных сигналов, цифровых сигналов и так далее). Соответственно, считываемый машиной носитель информации может содержать любой тип материального, считываемого компьютером носителя, подходящего для хранения или передачи электронных команд или информации в форме, считываемой машиной (например, компьютером).

Конструкция может проходить различные ступени от создания до моделирования и изготовления. Данные, представляющие конструкцию, могут представлять конструкцию различными способами. Во-первых, что может быть полезно при моделировании, аппаратное обеспечение может быть представлено с использованием языка описания аппаратного обеспечения или другого языка функционального описания. Кроме того, на некоторых ступенях процесса конструирования может быть изготовлена модель уровня схемы с логическими элементами и/или элементами-транзисторами. Более того, конструкции, на некоторой ступени, могут достичь уровня данных, представляющих физическое размещение различных устройств в модели аппаратного обеспечения. В случаях, когда используют некоторые технологии изготовления полупроводников, данные, представляющие модель аппаратного обеспечения, могут быть данными, определяющими наличие или отсутствие различных признаков на различных уровнях маски для масок, используемых для изготовления интегральной схемы. В любом представлении конструкции, данные могут быть сохранены в любой форме на считываемом машиной носителе. Память или магнитный или оптический накопитель, такой как диск, может быть считываемым машиной носителем для хранения информации, переданной с помощью оптической или электрической волны, модулированной или другим образом выработанной для передачи такой информации. Когда передают электрическую несущую волну, указывающую или несущую код или конструкцию, таким образом, что выполняют копирование, буферизацию или ретрансляцию электрического сигнала, может быть сделана новая копия. Таким образом, поставщик связи или поставщик доступа к сети может сохранять на материальном, считываемом машиной носителе, по меньшей мере, временно, изделие, такое как информация, закодированная в несущей волне и реализующая технологии вариантов осуществления настоящего изобретения.

В современных процессорах, для обработки и исполнения разного рода кода и команд может быть использовано большое количество разных блоков исполнения. Некоторые команды могут завершаться быстрее, а другие могут требовать для завершения некоторого количества тактовых циклов. Чем больше пропускная способность для команд, тем больше общая производительность процессора. Таким образом, предпочтительно, чтобы как можно большее количество команд исполнялось как можно быстрее. Тем не менее, могут присутствовать определенные команды, обладающие большей сложностью и требующие большего с точки зрения времени исполнения и ресурсов процессора, такие как команды с плавающей запятой, операции загрузки/сохранения, перемещения данных и так далее.

По мере использования большего количества компьютерных систем в интернет-приложениях, текстовых и мультимедийных приложениях, со временем была введена поддержка в виде дополнительного процессора. В одном варианте осуществления изобретения набор команд может быть связан с одной или несколькими архитектурами компьютера, содержащими типы данных, команды, архитектуру регистров, режимы адресации, архитектуру памяти, обработку прерываний и исключений и внешний ввод и вывод.

В одном варианте осуществления изобретения архитектура (ISA) набора команд может быть реализована одной или несколькими микроархитектурами, которые могут содержать логическую схему процессора и схемы, используемые для реализации одного или нескольких наборов команд. Соответственно, процессоры с различными микроархитектурами могут совместно использовать, по меньшей мере, часть общего набора команд. Например, процессоры Intel® Pentium 4, процессоры Intel® Core™ и процессоры компании Advanced Micro Devices, Inc., Саннивейл (Sunnyvale), Калифорния, реализуют практически идентичные версии набора х86 команд (с некоторыми расширениями, которые были добавлены в более новые версии), но обладают различными внутренними конструкциями. Аналогично, процессоры, разработанные другими компаниями-разработчиками процессоров, такими как ARM Holdings, Ltd., MIPS, или их лицензиаты или соразработчики, могут совместно использовать, по меньшей мере, часть общего набора команд, но могут обладать другими конструкциями. Например, одна и та же архитектура регистров из ISA может быть реализована различными путями в разных микроархитектурах, с использованием новых или хорошо известных технологий, в том числе специальных физических регистров, одного или нескольких динамических выделяемых физических регистров с использованием механизма переименования регистров (то есть, с использованием Таблицы (RAT) псевдонимов регистров, буфера (ROB) переупорядочивания и файла регистров выгрузки). В одном варианте осуществления изобретения регистры могут содержать один или несколько регистров, архитектур регистров, файлов регистров или других наборов регистров, которые могут как адресоваться, так и не адресоваться программистом.

Команда может подразумевать один или несколько форматов команд. В одном варианте осуществления изобретения формат команды может указывать различные поля (количество битов, расположение битов и так далее) для определения, помимо прочего, подлежащей выполнению операции и операндов, над которыми выполняют эту операцию. В еще одном варианте осуществления изобретения некоторые форматы команд могут быть дополнительно определены шаблонами команд (или подформатами). Например, шаблоны команды заданного формата команды могут быть определены так, что содержат разные подмножества полей формата команды и/или определены так, чтобы содержать заданное поле, интерпретируемое по-другому. В одном варианте осуществления изобретения команда может быть выражена с использованием некоторого формата команды (и, если определено, в одном из шаблонов команды для этого формата команды) и определяет или указывает операцию и операнды, над которыми будут выполнять эту операцию.

Научные, финансовые, автоматической векторизации общего назначения, RMS (распознавание, извлечение информации из данных и синтез) и визуальные и мультимедийные приложения (например, 2D/3D графика, обработка изображений, сжатие/распаковка видео, алгоритмы распознавания голоса и манипуляции звуком) могут требовать выполнения той же операции для большого количества элементов данных. В одном варианте осуществления изобретения тип команд (SIMD) с одним потоком команд и несколькими потоками данных представляет собой тип команд, который побуждает процессор выполнять операцию с множеством элементов данных. Технология SIMD может быть использована в процессорах, которые могут логически делить биты в регистре на некоторое количество элементов данных фиксированного размера или элементов данных переменного размера, каждый из которых представляет отдельное значение. Например, в одном варианте осуществления изобретения биты в 64-битовом регистре могут быть организованы как операнд-источник, содержащий четыре отдельных 16-битовых элемента данных, каждый из которых представляет отдельное 16-битовое значение. Этот тип данных может быть назван типом «упакованные» данные или типом «векторные» данные, и операнды этого типа данных могут называться операндами упакованных данных или векторными операндами. В одном варианте осуществления изобретения элемент упакованных данных или вектор может быть последовательностью элементов упакованных данных, сохраненной в одном регистре, и операнд упакованных данных или векторный операнд может быть операндом-источником или операндом-назначением SIMD команды (или «команды упакованных данных» или «векторной команды»). В одном варианте осуществления изобретения SIMD команда определяет одну векторную операцию, подлежащую выполнению для двух векторных операндов-источников с целью выработки векторного операнда-назначения (также называемого результирующим векторным операндом) такого же или другого размера, с таким же или другим количеством элементов данных и с таким же или другим порядком элементов данных.

Технология SIMD, такая, как использованная в процессорах Intel® Core™ с набором команд, содержащим команды x86, MMX™, потоковые SIMD расширения (SSE), SSE2, SSE3, SSE4.1 и SSE4.2, процессорах ARM, таких как семейство процессоров ARM Cortex®, набор команд которых содержит векторные команды (VFP) с плавающей запятой и/или команды NEON, и процессорах MIPS, таких как семейство процессоров Loongson, разработанные Институтом вычислительной технологии (ICT) китайской Академии наук, позволила значительно улучшить производительность приложений (Core™ и MMX™ являются зарегистрированными торговыми марками или торговыми марками компании Intel Corporation, Санта-Клара (Santa Clara), Калифорния).

В одном варианте осуществления изобретения регистры/данные назначения и источника могут быть общими терминами, представляющими источник и назначение соответствующих данных или операции. В некоторых вариантах осуществления изобретения они могут быть реализованы с помощью регистров, памяти или других областей хранения, обладающих названиями или функциями, отличающимися от упомянутых. Например, в одном варианте осуществления изобретения «DEST1» может быть регистром временного хранения или другой областью хранения, а «SRC1» и «SRC2» могут быть первым и вторым регистром-источником для хранения или другой областью хранения и так далее. В других вариантах осуществления изобретения две или несколько SRC и DEST областей хранения могут соответствовать разным элементам хранения данных в одной области хранения (например, SIMD регистр). В одном варианте осуществления изобретения один из регистров-источников также может выступать как регистр-назначение, например, благодаря обратной записи результата операции, выполненной с первыми и вторыми исходными данными, в один из двух регистров-источников, служащих в качестве регистров-назначений.

На фиг. 1А показана структурная схема примера вычислительной системы, выполненной с процессором, который может содержать блоки исполнения для исполнения команды, в соответствии с вариантами осуществления настоящего изобретения. Система 100 может содержать компонент, такой как процессор 102, для применения блоков исполнения, содержащих логическую схему для выполнения алгоритмов по обработке данных, в соответствии с настоящим изобретением, например, в соответствии с описанным в настоящем документе вариантом осуществления изобретения. Система 100 может быть представителем систем обработки, основанных на микропроцессорах PENTIUM® III, PENTIUM® 4, Xeon™, Itanium®, XScale™ и/или StrongARM™ компании Intel Corporation, Санта-Клара, Калифорния, хотя также могут быть использованы другие системы (в том числе PC с другими микропроцессорами, инженерные рабочие станции, телевизионные приставки и подобное). В одном варианте осуществления изобретения пример системы 100 может исполнять версию операционной системы WINDOWS™ компании Microsoft Corporation, Редмонд (Redmond), Вашингтон, хотя также могут быть использованы другие операционные системы (например, UNIX и Linux), встроенное программное обеспечение и/или графические интерфейсы пользователя. Таким образом, варианты осуществления настоящего изобретения не ограничены какой-либо конкретной комбинацией аппаратной схемы и программного обеспечения.

Варианты осуществления изобретения не ограничены компьютерными системами. Варианты осуществления настоящего изобретения могут быть использованы в других устройствах, таких как карманные устройства и встроенные приложения. Некоторыми примерами карманных устройств являются сотовые телефоны, устройства интернет-протокола, цифровые фотокамеры, персональные цифровые помощники (PDA) и карманные PC. Встроенными приложениями могут являться микроконтроллер, цифровой сигнальный процессор (DSP), система на микросхеме, сетевые компьютеры (NetPC), телевизионные приставки, сетевые концентраторы, коммутаторы глобальной вычислительной сети (WAN) или любая другая система, которая может выполнить одну или несколько команд в соответствии, по меньшей мере, в одним вариантом осуществления изобретения.

Компьютерная система 100 может содержать процессор 102, который может содержать один или несколько блоков 108 исполнения для выполнения алгоритма с целью исполнения, по меньшей мере, одной команды в соответствии с одним вариантом осуществления настоящего изобретения. Один вариант осуществления изобретения может быть описан в контексте однопроцессорной настольной или серверной системы, но другие варианты осуществления изобретения могут содержать многопроцессорную систему. Система 100 может быть примером «блочной» архитектуры системы. Система 100 может содержать процессор 102 для обработки сигналов данных. Процессор 102 может содержать микропроцессор (CISC) со сложным набором команд, микропроцессор (RISC) с сокращенным набором команд, микропроцессор (VLIW) с очень длинным командным словом, процессор, реализующий комбинации наборов команд, или любое другое процессорное устройство, такое как, например, цифровой сигнальный процессор. В одном варианте осуществления изобретения процессор 102 может быть связан с шиной 110 процессора, которая может передавать сигналы данных между процессором 102 и другими компонентами в системе 100. Элементы системы 100 могут выполнять обычные функции, хорошо известные специалистам в рассматриваемой области.

В одном варианте осуществления изобретения процессор 102 может содержать внутреннюю кэш-память 104 уровня 1 (L1). В зависимости от архитектуры, процессор 102 может содержать одну внутреннюю кэш-память или несколько уровней внутренней кэш-памяти. В другом варианте осуществления изобретения кэш-память может быть внешней по отношению к процессору 102. Другие варианты осуществления изобретения могут также содержать комбинацию как внутренних, так и внешних кэш-памятей, в зависимости от конкретной реализации и потребностей. Файл 106 регистров может хранить данные различных типов в различных регистрах, в том числе регистрах целых чисел, регистрах чисел с плавающей запятой, регистрах состояния и регистре указателей команд.

Блок 108 исполнения, содержащий логическую схему для выполнения операций с целыми числами и числами с плавающей запятой, также расположен в процессоре 102. Процессор 102 также может содержать ROM микрокода (ucode), в котором хранят микрокод для определенных макрокоманд. В одном варианте осуществления изобретения блок 108 исполнения может содержать логическую схему для обработки набора 109 команд для упакованных данных. Благодаря содержанию набора 109 команд для упакованных данных в наборе команд процессора 102 общего назначения, вместе с связанной схемой по исполнению команд, могут быть выполнены операции, используемые многими мультимедийными приложениями, с использованием упакованных данных в процессоре 102 общего назначения. Таким образом, многие мультимедийные приложения могут быть ускорены и исполнены более эффективно путем использования полной ширины шины данных процессора для выполнения операций с упакованными данными. Это может исключить потребность в переносе более мелких блоков данных по шине данных процессора с целью выполнения одной или нескольких операций с одним элементом данных за один раз.

Варианты осуществления блока 108 исполнения также могут быть использованы в микроконтроллерах, встроенных процессорах, графических устройствах, DSP и других типах логических схем. Система 100 может содержать память 120. Память 120 может быть реализована как динамическое оперативное запоминающее устройство (DRAM), статическое оперативное запоминающее устройство (SRAM), устройство флеш-памяти или другое устройство памяти. Память 120 может хранить команды и/или данные, представленные сигналами данных, которые могут быть исполнены процессором 102.

Микросхема 116 системной логики может быть связана с шиной 110 процессора и памятью 120. Микросхема 116 системной логики может содержать контроллер-концентратор (MCH) памяти. Процессор 102 может взаимодействовать с MCH 116 с помощью шины 110 процессора. MCH 116 может обеспечивать широкополосный путь 118 памяти к памяти 120 для хранения команд и данных и для хранения графических команд, данных и структур. MCH 116 может направлять сигналы данных между процессором 102, памятью 120 и другими компонентами в системе 100 и передавать сигналы данных между шиной 110 процессора, памятью 120 и вводом/выводом 122 системы. В некоторых вариантах осуществления изобретения микросхема 116 системной логики может предоставлять графический порт для связи с графическим контроллером 112. MCH 116 может быть соединен с памятью 120 с помощью интерфейса 118 памяти. Графическая карта 112 может быть связана с MCH 116 с помощью соединения 114 ускоренного графического порта (AGP).

Система 100 может использовать запатентованную шину 122 интерфейса концентратора для связи MCH 116 c контроллером-концентратором 130 (ICH) ввода-вывода. В одном варианте осуществления изобретения ICH 130 может обеспечивать прямые соединения с некоторыми устройствами ввода/вывода с помощью локальной шины ввода/вывода. Локальная шина ввода/вывода может содержать высокоскоростную шину ввода/вывода для соединения периферийных устройств с памятью 120, набором микросхем и процессором 102. Примерами могут являться контроллер звука, аппаратно реализованный программный концентратор 128 (флеш BIOS), устройство 126 беспроводной приемо-передачи, запоминающее устройство 124 для данных, существующий контроллер ввода/вывода, содержащий интерфейсы ввода данных пользователем и клавиатуры, последовательный порт расширения, такой как универсальная последовательная шина (USB) и сетевой контроллер 134. Запоминающее устройство 124 для данных может содержать накопитель на жестких дисках, накопитель на гибких дисках, устройство CD-ROM, устройство флеш-памяти или другое запоминающее устройство большой емкости.

В другом варианте осуществления системы, команда, соответствующая одному варианту осуществления изобретения, может быть использована с системой на микросхеме. Один вариант осуществления системы на микросхеме содержит процессор и память. Память для одной такой системы может содержать флеш-память. Флеш-память может быть расположена на том же кристалле, что и процессор и другие компоненты системы. Кроме того, в системе на микросхеме также могут быть расположены другие логические блоки, такие как контроллер памяти или графический контроллер.

На фиг. 1В показана система 140 обработки данных, в которой реализованы принципы вариантов осуществления настоящего изобретения. Специалисту в рассматриваемой области ясно, что описанные в настоящем документе варианты осуществления изобретения могут работать с альтернативными системами обработки, без выхода за границы объема патентования вариантов осуществления изобретения.

Компьютерная система 140 содержит обрабатывающее ядро 159 для выполнения, по меньшей мере, одной команды, в соответствии с одним вариантом осуществления изобретения. В одном варианте осуществления изобретения обрабатывающее ядро 159 представляет собой обрабатывающий блок с архитектурой любого типа, в том числе, помимо прочего, архитектурой типа CISC, RISC или VLIW. Обрабатывающее ядро 159 также может быть изготовлено с помощью одной или нескольких технологий обработки и может быть представлено на считываемом машиной носителе с достаточностью степенью детальности, может подходить для облегчения указанного изготовления.

Обрабатывающее ядро 159 содержит блок 142 исполнения, набор 145 файлов регистров и декодер 144. Обрабатывающее ядро 159 также может содержать дополнительную схему (не показана), которая может быть необязательной для понимания вариантов осуществления настоящего изобретения. Блок 142 исполнения может исполнять команды, принятые обрабатывающим ядром 159. Помимо выполнения типовых команд процессора, блок 142 исполнения может выполнять команды набора 143 команд для упакованных данных с целью выполнения операций над данными, представленными в форматах упакованных данных. Набор 143 команд для упакованных данных может содержать команды для выполнения вариантов осуществления изобретения и другие упакованные команды. Блок 142 исполнения может быть связан с файлом 145 регистров с помощью внутренней шины. Файл 145 регистров может представлять собой область хранения в обрабатывающем ядре 159 для хранения информации, в том числе данных. Как упомянуто выше, ясно, что область хранения может хранить упакованные данные, которые могут не быть критическими. Блок 142 исполнения может быть связан с декодером 144. Декодер 144 может декодировать команды, принятые обрабатывающим ядром 159, в сигналы управления и/или точки входа микрокода. В ответ на эти сигналы управления и/или точки входа микрокода, блок 142 исполнения выполняет соответствующие операции. В одном варианте осуществления изобретения декодер может интерпретировать код операции команды, который будет указывать, какую выполнять операцию с соответствующими данными, указанными в команде.

Обрабатывающее ядро 159 может быть связано с шиной 141 для обмена информацией с различными другими устройствами системы, которые могут содержать, помимо прочего, например, контроллер 146 синхронного динамического оперативного запоминающего устройства (SDRAM), контроллер 147 статичного оперативного запоминающего устройства (SRAM), интерфейс 148 пакетной флеш-памяти, контроллер 149 карты Международной ассоциации производителей карт памяти для персональных компьютеров (PCMCIA)/Сompact flash (CF), контроллер 150 жидкокристаллического дисплея (LCD), контроллер 151 прямого доступа (DMA) к памяти и интерфейс 152 альтернативного ведущего устройства шины. В одном варианте осуществления изобретения система 140 обработки данных также может содержать мост 154 ввода/вывода для связи с различными устройствами ввода/вывода с помощью шины 153 ввода/вывода. Такие устройства ввода/вывода могут содержать, помимо прочего, например, универсальное асинхронное устройство 155 (UART) приема/передачи, универсальную последовательную шину 156 (USB), UART 157 беспроводной технологии Bluetooth и интерфейс 158 расширения ввода/вывода.

Один вариант осуществления системы 140 обработки данных обеспечивает мобильную, сетевую и/или беспроводную связь и обрабатывающее ядро 159, которое может выполнять SIMD операции, в том числе операцию сравнения текстовых строк. Обрабатывающее ядро 159 может быть запрограммировано с помощью различных звуковых алгоритмов, видео алгоритмов, алгоритмов обработки изображений и алгоритмов связи, содержащих дискретные преобразования, такие как преобразование Уолша-Адамара, быстрое преобразование (FFT) Фурье, дискретное косинусное преобразование (DCT) и их соответствующие обратные преобразования; технологий сжатия/распаковки, такие как преобразование цветового пространства, оценка движения при кодировании видео или компенсация движения при декодировании видео; и функций (MODEM) модуляции/демодуляции, таких как импульсно-кодовая модуляция (PCT).

На фиг. 1С показаны другие варианты осуществления системы обработки данных, которая выполняет SIMD операции сравнения текстовых строк. В одном варианте осуществления изобретения система 160 обработки данных может содержать основной процессор 166, SIMD сопроцессор 161, кэш-память 167 и систему 168 ввода/вывода. Система 168 ввода/вывода может, при желании, быть связана с беспроводным интерфейсом 169. SIMD сопроцессор 161 может выполнять операции, содержащие команды, в соответствии с одним вариантом осуществления изобретения. В одном варианте осуществления изобретения обрабатывающее ядро 170 может быть изготовлено с помощью одной или нескольких технологий обработки и может быть представлено на считываемом машиной носителе с д