Аналогово-цифровой преобразователь сигналов

Иллюстрации

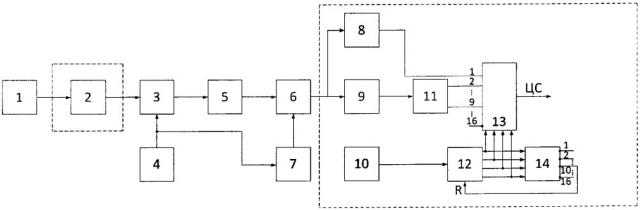

Показать всеИзобретение относится к области передачи цифровых сигналов и может быть использовано для аналогово-цифрового преобразования. Техническим результатом является увеличение частотной эффективности цифрового сигнала, уменьшение шумов квантования, упрощение структуры АЦП. Устройство содержит источник аналогового сигнала, делитель полосы частот аналогового сигнала, дискретизатор по времени разделенного аналогового сигнала, генераторы импульсов, компрессор уровня отсчетов, расширитель импульсов, блок задержки по времени, однополупериодный выпрямитель, двухполупериодный выпрямитель, кодер модуля отсчетов, счетчик импульсов, мультиплексор, дешифратор. 1 ил.

Реферат

Область техники, к которой относится изобретение

Изобретение относится к области передачи цифровых сигналов.

Уровень техники

Известны аналогово-цифровые преобразователи (АЦП), описанные в различных источниках:

1. Шмытинский В.В., Глушко В.П., Казанский Н.А. Многоканальная связь на железнодорожном транспорте. - М.: ГОИ, 2008.

2. Шмытинский В.В., Котов В.К., Здоровцов И.А. Цифровые системы передачи информации на железнодорожном транспорте. - М.: Транспорт, 1995. - С. 72-81.

3. Патент РФ на ПМ №114247. АЦП речевого сигнала / Волков А.А., О.Е. Журавлев, В.А. Кузюков. Приоритет от 07.10.2011.

По технической сущности наиболее близким к данному изобретению является устройство, описанное в первом источнике, который по этой причине и принимается за его прототип. В остальных источниках раскрыты аналоги изобретения.

АЦП-прототип содержит, как обычно, три операции: дискретизацию аналогового сигнала по времени, квантование отсчетов по уровню и кодирование каждого компрессированного отсчета восемью двоичными разрядами, которые называются кодовым словом, а все перечисленные операции вместе называются импульсно-кодовой модуляцией (ИКМ).

Особенностью АЦП-прототипа (ИКМ-30) является кодирование квантованных отсчетов по методу взвешивания с неравномерным квантованием уровней отсчетов, для чего кодер имеет нелинейную квазилогарифмическую характеристику, объединяющую процесс квантования и кодирования отсчетов, то есть в нем сосредоточены основные процессы АЦП с учетом того, что на его вход поступают отсчеты дискретизированного по времени аналогового сигнала (АИМ-2)

Кодер состоит из компаратора К, цифрового восьмиразрядного регистра (ЦР), устройства преобразования сигналов управления (УПСУ), двух формирователей эталонных сигналов (ФЭС), устройства коммутации ФЭС (УКФ).

Цифровой регистр с логикой управления записывает и хранит информацию, полученную от компрессора К по цепи обратной связи, в соответствии с которой формируются сигналы управления работой ФЭС. УПСУ преобразует семиразрядный код, поступающий с выхода ЦР, в сигналы управления ключами ФЭС. Устройство УКФ пропускает сигналы управления от УПСУ на входы одного из ФЭС в зависимости от знака сигнала.

В методе взвешивания кодера для определения уровня квантования отсчета используются 11 эталонов для обеспечения неравномерного квантования по уровню, плавная логарифмическая кривая заменяется ломаной линией, состоящей из 16 сегментов по 8 для положительной и отрицательной областей изменения сигнала. Восьмью разрядами (кодовым словом) записывается каждый квантованный отсчет. Всего уровней квантования 28=256. Если отсчет попадает между соседними квантованными уровнями, то он округляется до ближайшего, отчего вносится погрешность в уровень сигнала, которая называется шумом квантования. Погрешность квантования не превосходит половины разницы между соседними отсчетами. Так как аналоговый речевой сигнал (PC) знакопеременный, то и дискретизированный по времени аналоговый сигнал будет знакопеременным (двухполярным) и поэтому кроме модуля отсчета необходимо передавать и его знак. В ИКМ-30 его передают в первом разряде кодового слова, а на передачу модуля отсчета остается только 7 разрядов, отчего шумы квантования увеличиваются в 2 раза. Для исключения этого в ИКМ-30 используют неравномерное квантование по уровню: нулевой и первый сегменты имеют одинаковые и минимальные интервалы квантования, как и при восьми разрядах квантования, а в остальных сегментах интервалы удваиваются по отношению к предыдущему. В этом случае и шумы квантования увеличиваются, но отношение мощности сигнала отсчета к мощности шума квантования остается приблизительно таким же, как и при восьмиразрядном квантовании.

Основным недостатком прототипа является сложность АЦП, что отрицательно сказывается на его надежности, большой уровень шумов квантования, сложность записи кода отсчета: первый разряд - знак, 2-4 - номер сегмента, куда попадает отсчет, 5-8 - формируют линейное квантование внутри сегмента, куда попадает отсчет.

Раскрытие изобретения

Техническим результатом изобретения является устранение указанных недостатков за счет введения делителя полосы частот в два раза аналогового сигнала, позволившего ввести девятый разряд в кодовое слово для записи знака отсчета, а 8 разрядов остаются для записи его модуля, отчего шумы квантования не возрастают, а полоса частот цифрового сигнала значительно сокращается за счет указанного деления.

Сущность изобретения состоит в том, что в аналогово-цифровой преобразователь (АЦП) сигналов, состоящий из последовательно включенных источника аналоговых сигналов (ИАС), дискретизатора аналоговых сигналов по времени, компрессора уровней отсчетов аналогового сигнала, расширителя отсчетов (АИМ-2), кодера, а также из блока задержки по времени и генератора импульсов, выход которого подключен ко второму входу дискретизатора по времени и параллельно через блок задержки ко второму входу расширителя импульсов, в него дополнительно введены делитель полосы частот аналогового сигнала в два раза, однополупериодный выпрямитель, двухполупериодный выпрямитель, мультиплексор, второй генератор импульсов, счетчик импульсов, дешифратор, причем, через делитель полосы частот в два раза соединяется выход ИАС с входом дискретизатора по времени; двухполупериодный выпрямитель подключен между выходом расширителя импульсов и входом кодера, а однополупериодный выпрямитель соединяет выход расширителя импульсов с первым входом контакта мультиплексора, а выходы восьмиразрядного параллельного кода кодера подключены соответственно к восьми входам контактов мультиплексора, в котором осуществляется их временное уплотнение, а к адресным входам которого подключены четыре параллельных выхода счетчика импульсов с введенным генератором на его входе; чтобы перевести единицу с девятого выхода дешифратора на первый и осуществить временное уплотнение только девяти разрядов в мультиплексоре, его десятый выход подключен к R входу счетчика импульсов.

Существенным отличием изобретения является введенный в прототип делитель полосы частот непрерывного речевого сигнала (PC) в два раза согласно патенту №2259632 «Способ деления полосы частот передаваемого сигнала и устройство для его осуществления». / А.А. Волков. Приоритет от 24.03.2004, позволяющий значительно сократить полосу частот цифрового сигнала (ЦС) и ввести девятый разряд в кодовом слове для замены неравномерного квантования равномерным и тем самым уменьшить шаг квантования, повысив качество цифровой передачи.

Краткое описание чертежей

Изобретение иллюстрируется чертежом, где представлена структурная схема предлагаемого АЦП, который состоит из источника аналогового сигнала 1, делителя полосы частот аналогового сигнала 2, дискретизатора по времени разделенного аналогового сигнала 3, генераторов импульсов 4,10, компрессора уровня отсчетов 5, расширителя импульсов (АИМ-2) 6, блока задержки по времени 7, однополупериодного выпрямителя 8, двухполупериодного выпрямителя 9, кодера модуля отсчетов 11, счетчика импульсов 12, мультиплексора 13, дешифратора 14. Введенные элементы обведены пунктирными линиями

Осуществление изобретения

Работа схемы происходит следующим образом.

Аналоговый речевой сигнал (PC) с блока 1 поступает на вход блока 2, где происходит деление его полосы частот в два раза, и максимальная его частота вместо 3,4 кГц становится равной 1,7 кГц. Сигнал с блока 2 поступает на один вход дискретизатора 3, на второй вход которого подаются импульсы с частотой следования 4 кГц вместо стандартных 8 кГц согласно теореме Котельникова. С выхода дискретизатора двухполярные импульсы компрессируются по уровню в блоке 5, после чего они поступают на один вход расширителя импульсов (АИМ-2) 6, на второй вход которого подаются импульсы с генератора 4 через блок задержки 7. С выхода блока 6 двухполярные прямоугольные импульсы длительностью τ поступают на вход однополупериодного выпрямителя 8 и параллельно на вход двухполупериодного выпрямителя 9. Блок 8 формирует знак отсчета в виде 1 или 0, который подается непосредственно на вход первого контакта мультиплексора 13. Двухполупериодный выпрямитель 9 формирует модуль отсчетов, который преобразуется в цифровой сигнал параллельного кода в блоке 11, после чего его разряды поступают на другие восемь контактов мультиплексора 13. С выхода генератора 10 сигнал поступает на вход счетчика 12, формирующего четыре параллельных импульса, которые подаются на адресные входы мультиплексора 13 и параллельно на вход дешифратора 14. В мультиплексоре 13 осуществляется временное уплотнение входных импульсов. Так как в данном устройстве введен девятый разряд, то 10-й выход дешифратора подключен к R входу счетчика 12 для перевода единицы с девятого его выхода на первый и работе мультиплексора 13 только с девятью разрядами.

Полоса частот цифрового сигнала согласно учебнику Зюко А.Г и др. «Теория передачи сигналов» М.: Радио и связь. 1986 г. - С. 251 выражается формулой Δƒцс=nΔƒас, где n=8 - число разрядов в кодовом слове. Полоса частот аналогового сигнала Δƒас=3,4-0,3=3,1 кГц, поэтому при n=8 и отсутствии деления Δƒцс=8⋅3,1=24,8 кГц. Согласно изобретению, при числе разрядов n=9 и разделению полосы PC в два раза Δƒцс=9⋅1,55=13,95<24,8 кГц, т.е меньше в 1,8 раза.

Технико-экономическим эффектом изобретения является повышение частотной эффективности цифрового сигнала в 1,8 раза, уменьшение шумов квантования, упрощение схемы и структуры цифрового сигнала.

Аналогово-цифровой преобразователь (АЦП) сигналов, состоящий из последовательно включенных источника аналоговых сигналов (ИАС), дискретизатора аналоговых сигналов по времени, компрессора уровней отсчетов аналогового сигнала, расширителя отсчетов (АИМ-2), кодера, а также из блока задержки по времени и генератора импульсов, выход которого подключен ко второму входу дискретизатора по времени и параллельно через блок задержки ко второму входу расширителя импульсов, отличающийся тем, что в него дополнительно введены делитель полосы частот аналогового сигнала в два раза, однополупериодный выпрямитель, двухполупериодный выпрямитель, мультиплексор, второй генератор импульсов, счетчик импульсов, дешифратор, причем, через делитель полосы частот в два раза соединяется выход ИАС с входом дискретизатора по времени; двухполупериодный выпрямитель подключен между выходом расширителя импульсов и входом кодера, а однополупериодный выпрямитель соединяет выход расширителя импульсов с первым входом контакта мультиплексора, а выходы восьмиразрядного параллельного кода кодера подключены соответственно к восьми входам контактов мультиплексора, в котором осуществляется их временное уплотнение, а к адресным входам которого подключены четыре параллельных выхода счетчика импульсов с введенным генератором на его входе; чтобы перевести единицу с девятого выхода дешифратора на первый и осуществить временное уплотнение только девяти разрядов в мультиплексоре, его десятый выход подключен к R входу счетчика импульсов.