Многопортовая ячейка оперативного запоминающего устройства

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в увеличении диапазона выходного напряжения ячейки до уровня питающего напряжения при сохранении повышенной сбоеустойчивости, увеличении нагрузочной способности ячейки и напряжения выходного сигнала. Ячейка оперативного запоминающего устройства содержит три последовательно соединенных инвертора, а также первый проходной ключ записи данных для записи данных в ячейку с первой входной разрядной шины, второй проходной ключ записи данных для записи данных в ячейку со второй входной разрядной шины, комплементарный проходной ключ для передачи данных из ячейки на первую выходную шину, комплементарный проходной ключ для передачи данных из ячейки на вторую выходную шину, комплементарный проходной ключ перезаписи, управляемый четвертым инвертором и четырехвходовой схемой 2И-2ИЛИ-НЕ. 2 ил.

Реферат

Изобретение относится к области микроэлектроники и может быть использовано в ячейках памяти статического оперативного запоминающего устройства (ОЗУ) специализированных полупроводниковых интегральных схем.

Наиболее распространенные ячейки ОЗУ используют в качестве запоминающего элемента триггер, образованный двумя инверторами и соединенный с входными и выходными разрядными шинами проходными ключами на основе транзисторов n-типа или р-типа. Количество разрядных шин и их направленность могут меняться. Так, в ячейке (патент США №673156, МПК G11C 11/412; G11C 7/10; G11C 8/16, опубл. 04.05.2004 г.) используется две входные и две выходные разрядные шины, каждая из которых соединена с запоминающим элементом через проходной ключ. Ячейка обладает малой занимаемой площадью в составе интегральной схемы, низким потреблением и высоким быстродействием. Однако из-за состязательности сигналов в триггере в режиме записи существует вероятность потери данных во время операции чтения и обязательное условие предзаряда шин данных перед чтением.

В патенте США №4833648 (МПК G11C 11/41; G11C 8/16, опубл. 23.05.1989 г.) в ОЗУ в запоминающий элемент (триггер) введена дополнительная обратная связь с проходным ключом между входом первого инвертора и выходом второго инвертора. Проходной ключ замыкается во время операции чтения, подтверждая ранее записанные данные, и размыкается во время операции записи. По сравнению с шеститранзисторной ячейкой преимуществом данной схемы является отсутствие состязательности в момент записи между новыми и старыми данными, недостатком - необходимость введения новой шины управления проходным ключом. Для чтения данных на выходе ячейки используются биполярные транзисторы. Таким образом, для реализации памяти на основе описанной ячейки необходимо наличие Би-КМОП технологии.

В двухпортовой ячейке (патент США №6992947, МПК G11C 8/00; G11C 8/16; H03K 19/177, опубл. 31.01.2006 г.) используются проходные ключи для записи данных, управляемые сигналами выбора столбца и строки, и проходные ключи для чтения данных, управляемые сигналом выбора строки. Между запоминающим элементом ячейки (триггером) и проходными ключами для чтения подключены транзисторы. Двухкоординатная выборка по строке и столбцу во время операции записи исключает побочное считывание всей строки, свойственное шеститранзисторной ячейке. Запоминающий элемент ячейки памяти изолирован от влияния выходной шины данных во время операции чтения. Наличие состязательности во время записи между старыми и новыми данными является недостатком указанной ячейки.

В ячейке, описанной в заявке США №20090086541 (МПК G11C 16/06, опубл. 02.04.2009 г.), применено разнесение входной и выходной шин данных. Во время операции записи данные усиливаются входным инвертором непосредственно в ячейке и через комплементарный проходной ключи передаются в триггер. Для чтения используется выходной инвертор с третьим состоянием, управляемый сигналом чтения. Благодаря этому запоминающий элемент изолирован от влияния выходной сигнальной шины, диапазон выходного сигнала соответствует напряжению питания схемы. Недостатком схемы является наличие состязательности между старыми и новыми данными во время операции записи.

Наиболее близким по совокупности существенных признаков (прототипом) изобретения является техническое решение, изложенное в патенте РФ №2507611 (МПК G11C 11/40, опубл. 20.09.2012 г.). Ячейка состоит из пар n-типа и р-типа МОП транзисторов, соединенных между собой, с шиной источника питания, адресными и разрядными шинами. Указанная ячейка является двухпортовой и обладает повышенной сбоеустойчивостью, однако диапазон ее выходного напряжения ниже напряжения питания, из-за чего требуется применение специальных схем усиления.

Существенными признаками прототипа, совпадающими с признаками заявляемого изобретения, являются: наличие трех последовательно соединенных инверторов; причем вход первого инвертора связан с первой входной шиной данных через первый проходной ключ записи данных, состоящий из двух последовательно включенных транзисторов, затворы которых управляются первой адресной шиной записи и первой адресной шиной выбора столбца; выход первого инвертора соединен с входом второго инвертора; выход второго инвертора соединен с входом первого инвертора через комплементарный проходной ключ перезаписи, вход третьего инвертора соединен с выходом второго инвертора, выход третьего инвертора соединен с первой выходной разрядной шиной.

Воздействие определенных внешних факторов, в частности тяжелых заряженных частиц, на запоминающую ячейку оперативного запоминающего устройства (ОЗУ) комплементарной металл-оксид-полупроводниковой (КМОП) структуры, что может приводить к сбою, несанкционированному изменению данных.

Технической проблемой является увеличение количества разрядных шин до двух входных и двух выходных, увеличение количества абонентов устройства с сохранением высоких эксплуатационных характеристик. Технический результат заключается в улучшении выходных характеристик, а именно: в увеличении диапазона выходного напряжения ячейки до уровня питающего напряжения при сохранении повышенной сбоеустойчивости, также увеличивается нагрузочная способность ячейки, увеличивается напряжение выходного сигнала. Во время операции считывания используются стандартные цифровые элементы, что исключает необходимость использования специальных схем усиления сигнала.

Для достижения вышеуказанных технических результатов ячейка оперативного запоминающего устройства выполнена содержащей три последовательно соединенных инвертора; вход первого инвертора соединен первой входной шиной данных через первый проходной ключ записи данных; вход первого инвертора соединен со второй входной шиной данных через второй проходной ключ записи данных; выход первого инвертора соединен с входом второго инвертора; выход второго инвертора соединен с входом первого инвертора через комплементарный проходной ключ перезаписи, один затвор которого управляется выходным сигналом четырехвходовой схемы 2И-2ИЛИ-НЕ, второй затвор ключа перезаписи управляется выходным сигналом четырехвходовой схемы 2И-2ИЛИ-НЕ через четвертый инвертор, при этом входами схемы 2И-2ИЛИ-НЕ являются адресные входы записи и выбора столбца обоих портов; вход третьего инвертора соединен с выходом второго инвертора, выход третьего инвертора соединен с первой выходной разрядной шиной через третий комплементарный проходной ключ, управляемый первой адресной шиной чтения данных и ее инверсией, и соединен со второй выходной разрядной шиной через четвертый комплементарный проходной ключ, управляемый второй адресной шиной чтения данных и ее инверсией; причем первый проходной ключ записи данных выполнен из двух последовательно включенных транзисторов, затворы которых управляются первой адресной шиной записи и первой адресной шиной выбора столбца, второй проходной ключ записи данных выполнен из двух последовательно включенных транзисторов, затворы которых управляются второй адресной шиной записи и второй адресной шиной выбора столбца.

От прототипа предлагаемое устройство отличается тем, что вход первого инвертора соединен со второй входной шиной данных через второй проходной ключ записи данных, состоящий из двух последовательно включенных транзисторов, затворы которых управляются второй адресной шиной записи и второй адресной шиной выбора столбца; в комплементарном проходном ключе перезаписи, один затвор управляется выходным сигналом четырехвходовой схемы 2И-2ИЛИ-НЕ, второй затвор ключа перезаписи управляется выходным сигналом четырехвходовой схемы 2И-2ИЛИ-НЕ через четвертый инвертор, при этом входами схемы 2И-2ИЛИ-НЕ являются адресные входы записи и выбора столбца обоих портов; третий комплементарный проходной ключ управляется первой адресной шиной чтения данных и ее инверсией, и соединен со второй выходной разрядной шиной через четвертый комплементарный проходной ключ, управляемый второй адресной шиной чтения данных и ее инверсией.

Вышеуказанные технические результаты достигаются тем, что в ячейке адресные сигналы записи и выбора столбца обоих портов через управляющую схему замыкают и размыкают комплементарный проходной ключ перезаписи данных, при этом третий (выходной) инвертор соединен через комплементарный проходной ключ с первой выходной разрядной шиной и через второй комплементарный проходной ключ со второй выходной разрядной шиной.

Изобретение поясняется следующими материалами:

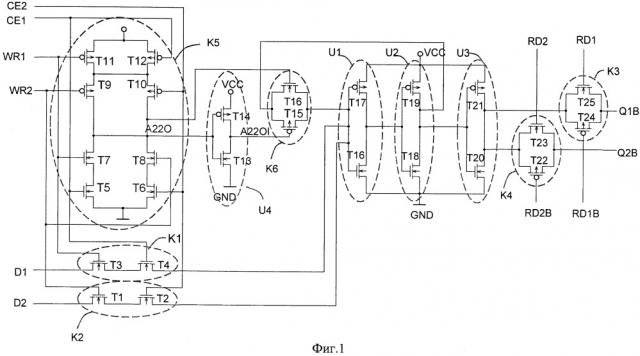

Фиг. 1 - принципиальная схема ячейки оперативного запоминающего устройства.

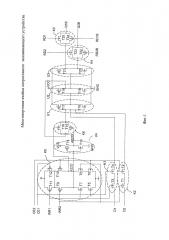

Фиг. 2 - таблица истинности

Устройство содержит последовательно соединенные первый инвертор U1 (транзисторы Т16 и Т17), второй инвертор U2 (транзисторы Т18 и Т19, образующие элемент памяти (триггер), третий инвертор U3 (транзисторы Т20 и Т21), а также первый проходной ключ записи данных (К1) для записи данных в ячейку с первой входной разрядной шины (D1), второй проходной ключ записи данных (К2) для записи данных в ячейку со второй входной разрядной шины (D2), комплементарный проходной ключ (К3) для передачи данных из ячейки на первую выходную шину (Q1B), комплементарный проходной ключ (К4) для передачи данных из ячейки на вторую выходную шину (Q2B), комплементарный проходной ключ перезаписи (К6), управляемый четвертым инвертором (U4) и четырехвходовой схемой 2И-2ИЛИ-НЕ (К5) (фиг. 1).

Первый, второй и третий инверторы U1, U2, U3 включены между шиной питания (VCC) и шиной земли (GND). Вход первого инвертора U1 соединен через комплементарный проходной ключ перезаписи (К6) с выходом второго инвертора (U2), через первый проходной ключ записи данных (К1) с первой входной разрядной шиной (D1) и через второй проходной ключ (К2) со второй входной разрядной шиной (D2). Выход первого инвертора (U1) соединен с входом второго инвертора (U2). Выход второго инвертора (U2) соединен с входом инвертора (U3). Выход третьего инвертора (U3) через второй проходной ключ (К2) соединен с выходной разрядной шиной (Q1B) и через комплементарный проходной ключ (К3) соединен с выходной разрядной шиной (Q2B).

Первый проходной ключ записи данных (К1) состоит из последовательно соединенных транзистора (Т3) n-типа и транзистора (Т4) п-типа, при этом затвор транзистора (Т4) соединен с первым адресным сигналом записи (WR1), затвор транзистора (Т3) соединен с первым адресным сигналом выбора столбца (СЕ1).

Второй проходной ключ (К2) состоит из последовательно соединенных транзистора (Т1) n-типа и транзистора (Т2) n-типа, при этом затвор транзистора (Т1) соединен со вторым адресным сигналом записи (WR2), затвор транзистора (Т2) соединен со вторым адресным сигналом выбора столбца (СЕ2).

Третий комплементарный проходной ключ (К3) образован параллельно включенными транзистором (Т25) n-типа и транзистором (Т24) р-типа, при этом затвор транзистора (Т25) соединен с адресным сигналом чтения (RD1), затвор транзистора (Т24) соединен с инверсным адресным сигналом чтения (RD1B).

Четвертый комплементарный проходной ключ (К4) образован параллельно включенными транзистором (Т23) n-типа и транзистором (Т22) р-типа, при этом затвор транзистора (Т23) соединен с адресным сигналом чтения (RD2), затвор транзистора (Т22) соединен с инверсным адресным сигналом чтения (RD2B).

Входами схемы 2И-2ИЛИ-НЕ (К5) являются адресные входы записи (WR1, WR2) и выбора столбца (СЕ1, СЕ2). Выходной сигнал (A22OI) схемы 2И-2ИЛИ-НЕ (К5) принимает значения в соответствии с таблицей истинности (фигура 2).

Четвертый инвертор (U4) образован транзисторами (Т13) и (Т14) и предназначен для управления комплементарным проходным ключом перезаписи (К6). Вход четвертого инвертора (U4) принимает выходной сигнал (A22OI) схемы 2И-2ИЛИ-НЕ (К5).

Комплементарный проходной ключ перезаписи (Кб) образован параллельно включенными транзистором (Т16) n-типа и транзистором (Т15) р-типа, при этом затвор транзистора (Т16) управляется сигналом (A22OI), затвор транзистора (Т15) соединен с выходом (А220) четвертого инвертора (U4).

Устройство работает следующим образом. В режиме хранения данных в ячейке ОЗУ выходы первого и второго инверторов (U1) и (U2) находятся в парафазном состоянии. Комплементарный проходной ключ перезаписи (Кб) замкнут и исполняет роль вносящего задержку элемента, обеспечивая защиту от одиночных сбоев. Входные разрядные шины могут находиться в активном высоком/низком логическом уровне или в высокоимпедансном состоянии. Выходные разрядные шины могут находиться в любом состоянии.

В режиме записи в ячейку ОЗУ данных с первой входной шины (D1) на ней формируется активный высокий/низкий логический уровень. На первый адресный вход записи (WR1) и вход выбора столбца (СЕ1) подается высокий логический уровень. Во избежание конфликтов на входах (WR2) и (СЕ2) должен быть сформирован низкий логический уровень. Данные с входной разрядной шины (D1) через первый проходной ключ записи данных (К1) поступают на вход первого инвертора (U1). При этом комплементарный проходной ключ перезаписи (К6) разрывает обратную связь триггера. Как только на один из адресных входов записи (WR1) или выбора столбца (СЕ1) подается низкий логический уровень, комплементарный проходной ключ перезаписи (К6) подключает обратную связь триггера, первый проходной ключ записи данных (К1) закрывается, наступает состояние хранения.

Режим записи данных с входной шины (D2) аналогичен записи с шины (D1). В этом случае на шине (D2) формируется активный высокий/низкий логический уровень. На первый адресный вход записи (WR2) и вход выбора столбца (СЕ2) подается высокий логический уровень. Во избежание конфликтов на входах (WR1) и (СЕ1) должен быть сформирован низкий логический уровень. Данные с входной разрядной шины (D2) через второй проходной ключ записи данных (К2) поступают на вход первого инвертора (U1). При этом комплементарный проходной ключ перезаписи (К6) разрывает обратную связь триггера. Как только на один из адресных входов записи (WR2) или выбора столбца (СЕ2) подается низкий логический уровень, комплементарный проходной ключ перезаписи (К6) подключает обратную связь триггера, второй проходной ключ записи данных (К2) закрывается, наступает состояние хранения.

В режиме чтения данных из ячейки ОЗУ на шину (Q1B) на адресный сигнал чтения (RD1) подается высокий логический уровень, на адресный сигнал чтения (RD1B) подается низкий логический уровень. Данные из триггера через третий инвертор (U3) и комплементарный проходной ключ (К3) поступают на выходную разрядную шину (Q1B). Предварительная зарядка выходной разрядной шины не требуется.

Аналогично осуществляется считывание данных на шину (Q2B). На адресный сигнал чтения (RD2) подается высокий логический уровень, на адресный сигнал чтения (RD2B) подается низкий логический уровень. Данные из триггера через третий инвертор (U3) и комплементарный проходной ключ (К3) поступают на выходную разрядную шину (Q2B).

Применение комплементарных выходных ключей (К3) и (К4) и развязывающего усилителя в виде третьего инвертора (U3) позволяет осуществить неразрушающее считывание и увеличить мощность и уровень выходного сигнала.

В режиме чтения данные могут передаваться как на одну из двух выходных разрядных шин, так и на обе шины одновременно.

Ячейка оперативного запоминающего устройства, содержащая три последовательно соединенных инвертора; вход первого инвертора соединен первой входной шиной данных через первый проходной ключ записи данных; вход первого инвертора соединен со второй входной шиной данных через второй проходной ключ записи данных; выход первого инвертора соединен с входом второго инвертора; выход второго инвертора соединен с входом первого инвертора через комплементарный проходной ключ перезаписи, один затвор которого управляется выходным сигналом четырехвходовой схемы 2И-2ИЛИ-НЕ, второй затвор ключа перезаписи управляется выходным сигналом четырехвходовой схемы 2И-2ИЛИ-НЕ через четвертый инвертор, при этом входами схемы 2И-2ИЛИ-НЕ являются адресные входы записи и выбора столбца обоих портов; вход третьего инвертора соединен с выходом второго инвертора, выход третьего инвертора соединен с первой выходной разрядной шиной через третий комплементарный проходной ключ, управляемый первой адресной шиной чтения данных и ее инверсией, и соединен со второй выходной разрядной шиной через четвертый комплементарный проходной ключ, управляемый второй адресной шиной чтения данных и ее инверсией; причем первый проходной ключ записи данных выполнен из двух последовательно включенных транзисторов, затворы которых управляются первой адресной шиной записи и первой адресной шиной выбора столбца, второй проходной ключ записи данных выполнен из двух последовательно включенных транзисторов, затворы которых управляются второй адресной шиной записи и второй адресной шиной выбора столбца.