Устройство для моделирования фазоповоротного устройства в энергетических системах

Иллюстрации

Показать всеИзобретение относится к области обработки данных, а именно к моделирующим устройствам, и может быть использовано при моделировании фазоповоротного устройства и его конструктивных элементов в составе энергетических систем. Техническим результатом является обеспечение в реальном времени воспроизведения процессов функционирования фазоповоротного устройства и его конструктивных элементов в нормальных, аварийных и послеаварийных режимах. Устройство содержит центральный процессор, процессор коммутации, процессор аналого-цифрового преобразования, блок многоканального аналого-цифрового преобразования, блоки моделирования продольно-поперечных коммутаций, блок моделирования шунтового трансформатора, блок моделирования сериесного трансформатора, блоки моделирования реакторов и блок моделирования тиристорного коммутатора. 5 ил.

Реферат

Изобретение относится к области обработки данных, а именно к моделирующим устройствам и может быть использовано при моделировании фазоповоротного устройства и его конструктивных элементов в составе энергетических систем.

Известно устройство для моделирования фазоповоротного устройства [М.Г. Асташев, М.А. Новиков, Д.И. Панфилов, П.А. Рашитов, М.И. Федорова Упрощенная аналитическая модель для исследования неполнофазных режимов работы фазоповоротного устройства с тиристорным коммутатором // Известия Российской академии наук. Энергетика. - 2014. - №1. - С. 91-104], выбранное в качестве прототипа, которое содержит блок моделирования трехфазного сериесного трансформатора, вторичные обмотки которого выполнены со средним выводом и вставлены в рассечку фаз высоковольтной линии электропередачи, а первичные обмотки соединены по схеме треугольник, узлы соединения обмоток которого подключены к высоковольтным выводам блока моделирования трехфазного высоковольтного коммутатора. Низковольтные выводы всех фаз блока моделирования коммутатора соединены по схеме звезда. Входные выводы каждой фазы блока моделирования коммутатора подключены к вторичной обмотке соответствующей фазы блока моделирования трехфазного шунтового трансформатора, первичные обмотки которого высоковольтными выводами подключены к средним выводам вторичных обмоток блока моделирования сериесного трансформатора, а низковольтными выводами соединены по схеме звезда и заземлены. Вторичная обмотка каждой фазы блока моделирования шунтового трансформатора выполнена в виде четырех гальванически развязанных секций. Каждая фаза блока моделирования трехфазного высоковольтного коммутатора выполнена в виде четырех последовательно соединенных тиристорных мостов с двунаправленными высоковольтными тиристорами в каждом плече. Входы тиристорных мостов каждой фазы блока моделирования высоковольтного коммутатора подключены к выводам одноименных секций вторичной обмотки соответствующей фазы блока моделирования шунтового трансформатора. Высоковольтные выводы последовательностей тиристорных мостов каждой фазы блока моделирования трехфазного коммутатора подключены к узлам соединения двух других фаз схемы треугольника, выполненной из первичных обмоток блока моделирования сериесного трансформатора. Все четыре секции вторичной обмотки каждой фазы блока моделирования шунтового трансформатора имеют разные коэффициенты трансформации и соответственно имеют разное число витков. Тиристорные мосты выполнены на напряжение соответствующей секции, к которой они подключены. Одноименные секции вторичной обмотки каждой фазы блока моделирования шунтового трансформатора выполнены с одинаковым коэффициентом трансформации.

С помощью этого устройство нельзя управлять параметрами блоков моделирования шунтового и сериесного трансформаторов, а также блока моделирования трехфазного полупроводникового коммутатора, что не позволяет моделировать фазоповоротное устройство с учетом влияния внешних факторов на параметры его конструктивных элементов. Кроме того, отсутствует возможность моделирования анормальных режимов и процессов функционирования фазоповоротного устройства и его конструктивных элементов, в том числе использования устройства в средствах моделирования крупных энергетических систем из-за ограничений физического моделирования, определяемых критериями подобия [Веников В.А. Теория подобия и моделирования (применительно к задачам электроэнергетики). Изд. 2, доп. и перераб. 1976. - С. 93-120].

Технической проблемой, на решение которой направлено предложенное изобретение, является создание устройства для моделирования фазоповоротного устройства в энергетических системах, позволяющего моделировать процессы функционирования фазоповоротного устройства, его конструктивных элементов в энергетических системах.

Предложенное устройство для моделирования фазоповоротного устройства в энергетических системах, также как в прототипе содержит блок моделирования трехфазного сериесного трансформатора, первичные обмотки которого соединены по схеме треугольник, блок моделирования трехфазного высоковольтного коммутатора, низковольтные выводы всех фаз которого соединены по схеме звезда, а входные выводы каждой фазы подключены ко вторичной обмотке соответствующей фазы блока моделирования трехфазного шунтового трансформатора, первичные обмотки которого низковольтными выводами соединены по схеме звезда и заземлены, а вторичная обмотка каждой фазы выполнена в виде четырех гальванически развязанных секций, каждая секция вторичной обмотки каждой фазы блока моделирования шунтового трансформатора выполнена с разными коэффициентами трансформации и соответственно с разным числом витков, одноименные секции вторичной обмотки каждой фазы блока моделирования шунтового трансформатора выполнены с одинаковым коэффициентом трансформации.

Согласно изобретению устройство дополнительно содержит десять блоков моделирования продольно-поперечных коммутаций, которые соединены с цифровыми выходами процессора коммутации, два блока моделирования реактора, центральный процессор, который подключен к компьютеру/серверу, процессору коммутации и процессору аналого-цифрового преобразования, который соединен с блоком многоканального аналого-цифрового преобразования. Первым входом/выходом устройства является вход/выход первого блока моделирования продольно-поперечных коммутаций, который соединен со вторым блоком моделирования продольно-поперечных коммутаций. Вторым входом/выходом устройства является вход/выход десятого блока моделирования продольно-поперечных коммутаций. Блок моделирования шунтового трансформатора содержит блоки моделирования фазы А, фазы В и фазы С шунтового трансформатора, цифровые входы которых подключены к центральному процессору, блок формирования напряжений шунтового трансформатора, подключенный к цифровому входу процессора коммутации. Аналоговые выходы блока моделирования фазы А шунтового трансформатора соединены с входами первого преобразователя напряжение-ток, первого и второго преобразователей напряжение-ток N-ой гальванически развязной секции шунтового трансформатора, где N=1, 2, 3, 4, и с входами блока многоканального аналого-цифрового преобразования. Аналоговые выходы блока моделирования фазы В шунтового трансформатора соединены с входами второго преобразователя напряжение-ток, третьего и четвертого преобразователей напряжение-ток N-ой секции и с входами блока многоканального аналого-цифрового преобразования. Аналоговые выходы блока моделирования фазы С шунтового трансформатора подключены к входам третьего преобразователя напряжение-ток, пятого и шестого преобразователей напряжение-ток N-ой секции и к входам блока многоканального аналого-цифрового преобразования. Аналоговые входы блоков моделирования фаз А, В и С шунтового трансформатора соединены с выходами блока формирования напряжений шунтового трансформатора, выходы которого соединены с входами блока многоканального аналого-цифрового преобразования. Выходы первого, второго, и третьего преобразователей напряжение-ток подключены к первому блоку моделирования продольно-поперечных коммутаций и к блоку формирования напряжений шунтового трансформатора. Выходы первого, третьего и пятого, преобразователей напряжение-ток N-ой секции связаны с третьим и четвертым блоками моделирования продольно-поперечных коммутаций и с блоком формирования напряжений шунтового трансформатора. Выходы второго, четвертого и шестого преобразователей напряжение-ток N-ой секции соединены с пятым блоком моделирования продольно-поперечных коммутаций и с блоком формирования напряжений шунтового трансформатора. Каждый блок моделирования реактора содержит блоки моделирования фаз А, В и С реактора, цифровые входы которых подключены к центральному процессору. Аналоговые выходы блока моделирования фазы А реактора соединены с входами четвертого и пятого преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования. Аналоговые выходы блока моделирования фазы В реактора связаны с входами шестого и седьмого преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования. Аналоговые выходы блока моделирования фазы С реактора соединены с входами восьмого и девятого преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования. Выход четвертого преобразователя напряжение-ток подключен к фазе А третьего блока моделирования продольно-поперечных коммутаций и к блоку моделирования фазы А реактора. Выход пятого преобразователя напряжение-ток соединен с фазой А шестого блока моделирования продольно-поперечных коммутаций и с блоком моделирования фазы А реактора. Выход шестого преобразователя напряжение-ток подключен к фазе В третьего блока моделирования продольно-поперечных коммутаций и к блоку моделирования фазы В реактора. Выход седьмого преобразователя напряжение-ток соединен с фазой В шестого блока моделирования продольно-поперечных коммутаций и с блоком моделирования фазы В реактора. Выход восьмого преобразователя напряжение-ток подключен к фазе С третьего блока моделирования продольно-поперечных коммутаций и к блоку моделирования фазы С реактора. Выход девятого преобразователя напряжение-ток соединен с фазой С шестого блока моделирования продольно-поперечных коммутаций и с блоком моделирования фазы С реактора.

Блок моделирования тиристорного коммутатора содержит блоки моделирования тиристорных мостов фаз А, В, С, выполненные одинаково. Блок моделирования тиристорного моста фазы А содержит первый, второй, третий, четвертый блоки цифроуправляемых аналоговых ключей и первый, второй, третий, четвертый блоки цифроуправляемых аналоговых ключей N-ой секции. Первый и второй блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой А четвертого и шестого блоков моделирования продольно-поперечных коммутаций. Третий и четвертый блоки цифроуправляемых аналоговых ключей связаны между собой и с фазой А пятого блока моделирования продольно-поперечных коммутаций. Первый и третий блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой А седьмого и восьмого блоков моделирования продольно-поперечных коммутаций. Второй и четвертый блоки цифроуправляемых аналоговых ключей соединены между собой и с первым и третьим блоками цифроуправляемых аналоговых ключей N-ой секции. Первый и второй блоки цифроуправляемых аналоговых ключей N-ой секции связаны между собой и с фазой А четвертого и шестого блоков моделирования продольно-поперечных коммутаций. Третий и четвертый блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и с фазой А пятого блока моделирования продольно-поперечных коммутаций. В блоке моделирования тиристорного моста фазы В первый и второй блоки цифроуправляемых аналоговых ключей связаны между собой и с фазой В четвертого и шестого блоков моделирования продольно-поперечных коммутаций. Третий и четвертый блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой В пятого блока моделирования продольно-поперечных коммутаций. Первый и третий блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой В седьмого и восьмого блоков моделирования продольно-поперечных коммутаций. Первый и второй блоки цифроуправляемых аналоговых ключей N-ой секции связаны между собой и с фазой В четвертого и шестого блоков моделирования продольно-поперечных коммутаций. Третий и четвертый блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и с фазой В пятого блока моделирования продольно-поперечных коммутаций. В блоке моделирования тиристорного моста фазы С первый и второй блоки цифроуправляемых аналоговых ключей связаны между собой и с фазой С четвертого и шестого блоков моделирования продольно-поперечных коммутаций. Третий и четвертый блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой С пятого блока моделирования продольно-поперечных коммутаций. Первый и третий блоки цифроуправляемых аналоговых ключей связаны между собой и с фазой С седьмого и восьмого блоков моделирования продольно-поперечных коммутаций. Первый и второй блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и с фазой С четвертого и шестого блоков моделирования продольно-поперечных коммутаций. Третий и четвертый блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и с фазой С пятого блока моделирования продольно-поперечных коммутаций. Второй и четвертый блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и со вторым и четвертым блоками цифроуправляемых аналоговых ключей N-ой секции блоков моделирования тиристорных мостов фаз В и С.

К процессору коммутации подключены первый, второй, третий, четвертый блоки цифроуправляемых аналоговых ключей и первый, второй, третий, четвертый блоки цифроуправляемых аналоговых ключей N-ой секции блоков моделирования тиристорных мостов фаз А, В, С.

Блок моделирования сериесного трансформатора содержит блоки моделирования фаз А, В и С сериесного трансформатора, цифровые входы которых подключены к центральному процессору. Цифровой вход блока формирования напряжений сериесного трансформатора подключен к процессору коммутации. Аналоговые выходы блока моделирования фазы А сериесного трансформатора соединены с входами десятого, одиннадцатого, двенадцатого преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования. Аналоговые выходы блока моделирования фазы В сериесного трансформатора подключены к входам тринадцатого, четырнадцатого, пятнадцатого преобразователей напряжение-ток и к входам блока многоканального аналого-цифрового преобразования. Аналоговые выходы блока моделирования фазы С сериесного трансформатора соединены с входами шестнадцатого, семнадцатого, восемнадцатого преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования. Аналоговые входы блоков моделирования фаз А, В и С сериесного трансформатора связаны с выходами блока формирования напряжений сериесного трансформатора, выходы которого соединены с входами блока многоканального аналого-цифрового преобразования. Выходы десятого, тринадцатого, шестнадцатого преобразователей напряжение-ток подключены к восьмому и девятому блокам моделирования продольно-поперечных коммутаций и к блоку формирования напряжений сериесного трансформатора. Выходы одиннадцатого, четырнадцатого, семнадцатого преобразователей напряжение-ток соединены со вторым блоком моделирования продольно-поперечных коммутаций и с блоком формирования напряжений сериесного трансформатора. Выходы двенадцатого, пятнадцатого, восемнадцатого преобразователей напряжение-ток связаны с десятым блоком моделирования продольно-поперечных коммутаций и с блоком формирования напряжений сериесного трансформатора.

Использование блоков моделирования продольно-поперечных коммутаций в предложенном устройстве обеспечивает всевозможные продольные и поперечные трехфазные коммутации, включая пофазные, а также соединение моделируемых конструктивных элементов фазоповоротного устройства. Блоки моделирования фаз реакторов, шунтового и сериесного трансформаторов позволяют воспроизвести квазиустановившиеся и переходные процессы в конструктивных элементах устройства в режиме реального времени и на неограниченно интервале. Преобразователи напряжение-ток осуществляют преобразование математических переменных фазных токов моделируемых конструктивных элементов фазоповоротного устройства в соответствующие им модельные физические токи и обеспечивают естественное взаимодействие конструктивных элементов и устройства в целом в реальном времени и в составе крупных энергетических систем. Связь центрального процессора с блоками моделирования фаз реакторов, шунтового и сериесного трансформаторов позволяет изменять параметры моделируемых конструктивных элементов предложенного устройства.

Таким образом, устройство моделирования фазоповоротного устройства, по сравнению с прототипом, обеспечивает более полное и достоверное воспроизведение в реальном времени непрерывного спектра нормальных и анормальных процессов функционирования фазоповоротного устройства и его конструктивных элементах с их изменяемыми и автоматически управляемыми параметрами.

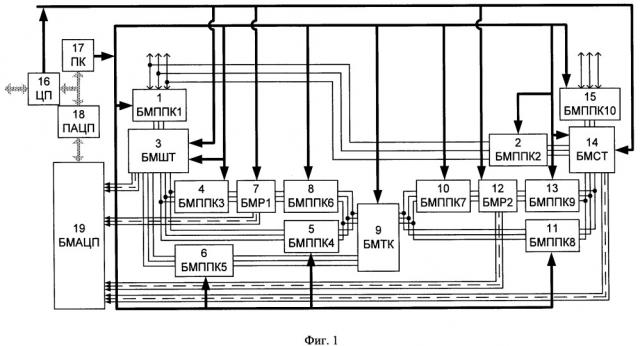

На фиг. 1 представлена структурная схема устройства для моделирования фазоповоротного устройства в энергетических системах.

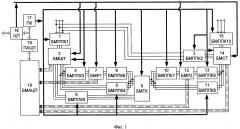

На фиг. 2 изображена структурная схема блока моделирования шунтового трансформатора 3 (БМШТ).

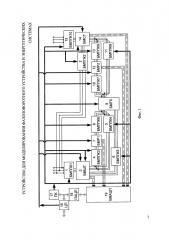

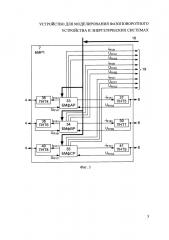

На фиг. 3 показана структурная схема блока моделирования реактора 7 (БМР1).

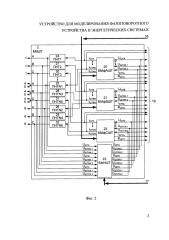

На фиг. 4 изображена структурная схема блока моделирования тиристорного коммутатора 9 (БМТК).

На фиг. 5 представлена структурная схема блока моделирования сериесного трансформатора 14 (БМСТ).

Устройство для моделирования фазоповоротного устройства в энергетических системах (фиг. 1) содержит первый 1 (БМППК1) блок моделирования продольно-поперечных коммутаций, который соединен со вторым 2 (БМППК2) блоком моделирования продольно-поперечных коммутаций. Вход/выход первого 1 (БМППК1) блока моделирования продольно-поперечных коммутаций является первым входом/выходом устройства. Второй вход первого 1 (БМППК1) блока моделирования продольно-поперечных коммутаций соединен с первым входом блока моделирования шунтового трансформатора 3 (БМШТ), второй вход которого связан с третьим 4 (БМППК3) и четвертым 5 (БМППК4) блоками моделирования продольно-поперечных коммутаций. Третий вход блока моделирования шунтового трансформатора 3 (БМШТ) соединен с пятым 6 (БМППК5) блоком моделирования продольно-поперечных коммутаций.

Второй вход третьего 4 (БМППК3) блока моделирования продольно-поперечных коммутаций подключен к первому блоку моделирования реактора 7 (БМР1), который соединен с шестым 8 (БМППК6) блоком моделирования продольно-поперечных коммутаций.

Вторые входы четвертого 5 (БМППК4) и шестого 8 (БМППК6) блоков моделирования продольно-поперечных коммутаций соединены между собой и с первым входом блока моделирования тиристорного коммутатора 9 (БМТК), второй вход которого соединен со вторым входом пятого 6 (БМППК5) блока моделирования продольно-поперечных коммутаций.

Третий вход блока моделирования тиристорного коммутатора 9 (БМТК) связан с седьмым 10 (БМППК7) и восьмым 11 (БМППК8) блоками моделирования продольно-поперечных коммутаций. Второй вход седьмого 10 (БМППК7) блока моделирования продольно-поперечных коммутаций соединен со вторым блоком моделирования реактора 12 (БМР2), который подключен к девятому 13 (БМППК9) блоку моделирования продольно-поперечных коммутаций.

Вторые входы восьмого 11 (БМППК8) и девятого 13 (БМППК9) блоков моделирования продольно-поперечных коммутаций соединены между собой и с первым входом блока моделирования сериесного трансформатора 14 (БМСТ), второй вход которого соединен со вторым входом второго 2 (БМППК2) блока моделирования продольно-поперечных коммутаций.

Третий вход блока моделирования сериесного трансформатора 14 (БМСТ) соединен с десятым 15 (БМППК10) блоком моделирования продольно-поперечных коммутаций, второй вход которого является вторым трехфазным входом/выходом устройства.

Цифровые входы управления параметрами блока моделирования шунтового трансформатора 3 (БМШТ), блоков моделирования реакторов 7 (БМР1) и 12 (БМР2), блока моделирования сериесного трансформатора 14 (БМСТ) подключены к цифровым выходам центрального процессора 16 (ЦП), который подключен к компьютеру/серверу. Центральный процессор 16 (ЦП), процессор коммутации 17 (ПК) и процессор аналого-цифрового преобразования 18 (ПАЦП) соединены между собой.

Процессор аналого-цифрового преобразования 18 (ПАЦП) соединен с блоком многоканального аналого-цифрового преобразования 19 (БМАЦП).

Цифровые входы управления параметрами блоков моделирования продольно-поперечных коммутаций 1 (БМППК1), 2 (БМППК2), 4 (БМППК3), 5 (БМППК4), 6 (БМППК5), 8 (БМППК6), 10 (БМППК7), 11 (БМППК8), 13 (БМППК9), и 15 (БМППК10), блока моделирования шунтового трансформатора 3 (БМШТ), блока моделирования тиристорного коммутатора 9 (БМТК) и блока моделирования сериесного трансформатора 14 (БМСТ) соединены с цифровыми выходами процессора коммутации 17 (ПК).

Аналоговые входы блока многоканального аналого-цифрового преобразования 19 (БМАЦП) соединены с блоками моделирования шунтового трансформатора 3 (БМШТ), блоками моделирования реакторов 7 (БМР1) и 12 (БМР2) и блоком моделирования сериесного трансформатора 14 (БМСТ).

Оба входа/выхода устройства моделирования фазоповоротного устройства, соединения между блоками моделирования продольно-поперечных коммутаций 1 (БМППК1), 2 (БМППК2), 4 (БМППК3), 5 (БМППК4), 6 (БМППК5), 8 (БМППК6), 10 (БМППК7), 11 (БМППК8), 13 (БМППК9), 15 (БМППК10), блока моделирования шунтового трансформатора 3 (БМШТ), блока моделирования тиристорного коммутатора 9 (БМТК), блока моделирования сериесного трансформатора 14 (БМСТ) и блоков моделирования реакторов 7 (БМР1) и 12 (БМР2) имеют трехфазную структуру.

Блок моделирования шунтового трансформатора 3 (БМШТ) (фиг. 2) содержит блоки моделирования фаз А, В и С шунтового трансформатора 20 (БМфАШТ), 21 (БМфВШТ) и 22 (БМфСШТ), цифровые входы которых подключены к центральному процессору 16 (ЦП).

Блок формирования напряжений шунтового трансформатора 23 (БФНШТ) через цифровой вход подключен к процессору коммутации 17 (ПК).

Аналоговые выходы блока моделирования фазы А шунтового трансформатора 20 (БМфАШТ) соединены с входами первого 24 (ПНТ1) преобразователя напряжение-ток, первого 25 (ПНТN1) и второго 26 (ПНТN2) преобразователей напряжение-ток N-ой гальванически развязной секции шунтового трансформатора, где N=1, 2, 3, 4, и с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Аналоговые выходы блока моделирования фазы В шунтового трансформатора 21 (БМфВШТ) соединены с входами второго 27 (ПНТ2) преобразователя напряжение-ток, третьего 28 (ПНТN3) и четвертого 29 (ПHTN4) преобразователей напряжение-ток N-ой секции и с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Аналоговые выходы блока моделирования фазы С шунтового трансформатора 22 (БМфСШТ) соединены с входами третьего 30 (ПНТ3) преобразователя напряжение-ток, пятого 31 (ПНТN5) и шестого 32 (ПHTN6) преобразователей напряжение-ток N-ой секции и с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Аналоговые входы блоков моделирования фаз А, В и С шунтового трансформатора 20 (БМфАШТ), 21 (БМфВШТ) и 22 (БМфСШТ) соединены с выходами блока формирования напряжений шунтового трансформатора 23 (БФНШТ), выходы которого соединены с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Выходы преобразователей напряжение-ток 24 (ПНТ1), 27 (ПНТ2), 30 (ПНТ3), которые являются первыми входами/выходами блока моделирования шунтового трансформатора 3 (БМШТ), соединены с первым 1 (БМППК1) блоком моделирования продольно-поперечных коммутаций и с блоком формирования напряжений шунтового трансформатора 23 (БФНШТ).

Выходы преобразователей напряжение-ток 25 (ПНТN1), 28 (ПНТN3), 31 (ПНТN5), которые являются вторыми входами/выходами блока моделирования шунтового трансформатора 3 (БМШТ), соединены с третьим 4 (БМППК3) и четвертым 5 (БМППК4) блоками моделирования продольно-поперечных коммутаций и с блоком формирования напряжений шунтового трансформатора 23 (БФНШТ).

Выходы преобразователей напряжение-ток 26 (ПНТN2), 29 (ПНТN4), 32 (ПНТN6), которые являются третьими входами/выходами блока моделирования шунтового трансформатора 3 (БМШТ), соединены с пятым 6 (БМППК5) блоком моделирования продольно-поперечных коммутаций и с блоком формирования напряжений шунтового трансформатора 23 (БФНШТ).

Первый блок моделирования реактора 7 (БМР1) (фиг. 3) содержит блоки моделирования фаз А, В и С реактора 33 (БМфАР), 34 (БМфВР) и 35 (БМфСР), цифровые входы которых подключены к центральному процессору 16 (ЦП).

Аналоговые выходы блока моделирования фазы А реактора 33 (БМфАР) соединены с входами четвертого 36 (ПНТ4) и пятого 37 (ПНТ5) преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Аналоговые выходы блока моделирования фазы В реактора 34 (БМфВР) соединены с входами шестого 38 (ПНТ6) и седьмого 39 (ПНТ7) преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Аналоговые выходы блока моделирования фазы С реактора 35 (БМфСР) соединены с входами восьмого 40 (ПНТ8) и девятого 41 (ПНТ9) преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Выход четвертого 36 (ПНТ4) преобразователя напряжение-ток соединен с фазой А третьего 4 (БМППК3) блока моделирования продольно-поперечных коммутаций и с блоком моделирования фазы А реактора 33 (БМфАР).

Выход пятого 37 (ПНТ5) преобразователя напряжение-ток соединен с фазой А шестого 8 (БМППК6) блока моделирования продольно-поперечных коммутаций и с блоком моделирования фазы А реактора 33 (БМфАР).

Выход шестого 38 (ПНТ6) преобразователя напряжение-ток соединен с фазой В третьего 4 (БМППК3) блока моделирования продольно-поперечных коммутаций и с блоком моделирования фазы В реактора 34 (БМфВР).

Выход седьмого 39 (ПНТ7) преобразователя напряжение-ток соединен с фазой В шестого 8 (БМППК6) блока моделирования продольно-поперечных коммутаций и с блоком моделирования фазы В реактора 34 (БМфВР).

Выход восьмого 40 (ПНТ8) преобразователя напряжение-ток соединен с фазой С третьего 4 (БМППК3) блока моделирования продольно-поперечных коммутаций и с блоком моделирования фазы С реактора 35 (БМфСР).

Выход девятого 41 (ПНТ9) преобразователя напряжение-ток соединен с фазой С шестого 8 (БМППК6) блока моделирования продольно-поперечных коммутаций и с блоком моделирования фазы С реактора 35 (БМфСР).

Первый и второй блоки моделирования ректора 7 (БМР1) и 12 (БМР2) выполнены одинаково.

Блок моделирования тиристорного коммутатора 9 (БМТК) (фиг. 4) содержит блоки моделирования тиристорных мостов фаз А 42 (БМТМфА), В 43 (БМТМфВ) и С 44 (БМТМфС), которые выполнены одинаково.

Блок моделирования тиристорного моста фазы А 42 (БМТМфА) содержит первый 45 (БЦАК1), 46 второй (БЦАК2), третий 47 (БЦАК3), четвертый 48 (БЦАК4) блоки цифроуправляемых аналоговых ключей, а также первый 49 (БЦАКN1), второй 50 (БЦАКN2), третий 51 (БЦАКN3), четвертый 52 (БЦАКN4), блоки цифроуправляемых аналоговых ключей N-секции, которые подключены к процессору коммутации 17 (ПК).

Первый 45 (БЦАК1) и второй 46 (БЦАК2) блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой А четвертого 5 (БМППК4) и шестого 8 (БМППК6) блоков моделирования продольно-поперечных коммутаций.

Третий 47 (БЦАК3) и четвертый 48 (БЦАК4) блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой А пятого 6 (БМППК5) блока моделирования продольно-поперечных коммутаций.

Первый 45 (БЦАК1) и третий 47 (БЦАК3) блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой А седьмого 10 (БМППК7) и восьмого 11 (БМППК8) блоков моделирования продольно-поперечных коммутаций.

Второй 46 (БЦАК2) и четвертый 48 (БЦАК4) блоки цифроуправляемых аналоговых ключей соединены между собой и с первым 49 (БЦАКN1) и третьим 51 (БЦАКN3) блоками цифроуправляемых аналоговых ключей N-ой секции.

Первый 49 (БЦАКN1) и второй 50 (БЦАКN2) блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и с фазой А четвертого 5 (БМППК4) и шестого 8 (БМППК6) блоков моделирования продольно-поперечных коммутаций.

Третий 51 (БЦАКN3) и четвертый 52 (БЦАКN4) блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и с фазой А пятого 6 (БМППК5) блока моделирования продольно-поперечных коммутаций.

В блоке моделирования тиристорного моста фазы В 43 (БМТМфВ) первый 45 (БЦАК1) и второй 46 (БЦАК2) блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой В четвертого 5 (БМППК4) и шестого 8 (БМППК6) блоков моделирования продольно-поперечных коммутаций. Третий 47 (БЦАК3) и четвертый 48 (БЦАК4) блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой В пятого 6 (БМППК5) блока моделирования продольно-поперечных коммутаций. Первый 45 (БЦАК1) и третий 47 (БЦАК3) блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой В седьмого 10 (БМППК7) и восьмого 11 (БМППК8) блоков моделирования продольно-поперечных коммутаций. Первый 49 (БЦАКN1) и второй 50 (БЦАКN2) блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и с фазой В четвертого 5 (БМППК4) и шестого 8 (БМППК6) блоков моделирования продольно-поперечных коммутаций. Третий 51 (БЦАКN3) и четвертый 52 (БЦАКN4) блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и с фазой В пятого 6 (БМППК5) блока моделирования продольно-поперечных коммутаций.

В блоке моделирования тиристорного моста фазы С 44 (БМТМфС) первый 45 (БЦАК1) и второй 46 (БЦАК2) блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой С четвертого 5 (БМППК4) и шестого 8 (БМППК6) блоков моделирования продольно-поперечных коммутаций. Третий 47 (БЦАК3) и четвертый 48 (БЦАК4) блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой С пятого 6 (БМППК5) блока моделирования продольно-поперечных коммутаций. Первый 45 (БЦАК1) и третий 47 (БЦАК3) блоки цифроуправляемых аналоговых ключей соединены между собой и с фазой С седьмого 10 (БМППК7) и восьмого 11 (БМППК8) блоков моделирования продольно-поперечных коммутаций. Первый 49 (БЦАКN1) и второй 50 (БЦАКN2) блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и с фазой С четвертого 5 (БМППК4) и шестого 8 (БМППК6) блоков моделирования продольно-поперечных коммутаций. Третий 51 (БЦАКN3) и четвертый 52 (БЦАКN4) блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и с фазой С пятого 6 (БМППК5) блока моделирования продольно-поперечных коммутаций.

Второй 50 (БЦАКN2) и четвертый 52 (БЦАКN4) блоки цифроуправляемых аналоговых ключей N-ой секции соединены между собой и со вторым 50 (БЦАКN2) и четвертым 52 (БЦАКN4) блоками цифроуправляемых аналоговых ключей N-ой секции блоков моделирования тиристорных мостов фаз В 43 (БМТМфВ) и С 44 (БМТМфС).

Блок моделирования сериесного трансформатора 14 (БМСТ) (фиг. 5) содержит блоки моделирования фаз А, В и С сериесного трансформатора 53 (БМфАСТ), 54 (БМфВСТ) и 55 (БМфССТ), цифровые входы которых подключены к центральному процессору 16 (ЦП).

Цифровой вход блока формирования напряжений сериесного трансформатора 56 (БФНСТ) подключен к процессору коммутации 17 (ПК).

Аналоговые выходы блока моделирования фазы А сериесного трансформатора 53 (БМфАСТ) соединены с входами десятого 57 (ПНТ10), одиннадцатого 58 (ПНТ11), двенадцатого 59 (ПНТ12) преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Аналоговые выходы блока моделирования фазы В сериесного трансформатора 54 (БМфВСТ) соединены с входами тринадцатого 60 (ПНТ13), четырнадцатого 61 (ПНТ14), пятнадцатого 62 (ПНТ15) преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Аналоговые выходы блока моделирования фазы С сериесного трансформатора 55 (БМфССТ) соединены с входами шестнадцатого 63 (ПНТ16), семнадцатого 64 (ПНТ17), восемнадцатого 65 (ПНТ18) преобразователей напряжение-ток и с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Аналоговые входы блоков моделирования фаз А, В и С сериесного трансформатора 53 (БМфАСТ), 54 (БМфВСТ) и 55 (БМфССТ) соединены с выходами блока формирования напряжений сериесного трансформатора 56 (БФНСТ), выходы которого соединены с входами блока многоканального аналого-цифрового преобразования 19 (БМАЦП).

Выходы десятого 57 (ПНТ10), тринадцатого 60 (ПНТ13), шестнадцатого 63 (ПНТ16) преобразователей напряжение-ток, которые являются первыми трехфазными входами/выходами блока моделирования сериесного трансформатора 14 (БМСТ), соединены с восьмым 11 (БМППК8) и девятым 13 (БМППК9) блоками моделирования продольно-поперечных коммутаций и с блоком формирования напряжений сериесного трансформатора 56 (БФНСТ).

Выходы одиннадцатого 58 (ПНТ11), четырнадцатого 61 (ПНТ14), семнадцатого 64 (ПНТ17) преобразователей напряжение-ток, которые являются вторыми трехфазными входами/выходами блока моделирования сериесного трансформатора 14 (БМСТ), соединены со вторым блоком моделирования продольно-поперечных коммутаций 2 (БМППК2) и с блоком формирования напряжений сериесного трансформатора 56 (БФНСТ).

Выходы двенадцатого 59 (ПНТ12), пятнадцатого 62 (ПНТ15), восемнадцатого 65 (ПНТ18) преобразователей напряжение-ток, которые являются третьими трехфазными входами/выходами блока моделирования сериесного трансформатора 14 (БМСТ), соединены с десятым блоком моделирования продольно-поперечных коммутаций 15 (БМППК10) и с блоком формирования напряжений сериесного трансформатора 56 (БФНСТ).

Блоки моделирования продольно-поперечных коммутаций 1 (БМППК1), 2 (БМППК2), 4 (БМППК3), 5 (БМППК4), 6 (БМППК5), 8 (БМППК6), 10 (БМППК7), 11 (БМППК8), 13 (БМППК9) и 15 (БМППК10), блоки цифроуправляемых аналоговых ключей 45 (БЦАК1), 46 (БЦАК2), 47 (БЦАК3), 48 (БЦАК4), 49 (БЦАКN1), 50 (БЦАКN2), 51 (БЦАКN3), 52 (БЦАКN4) реализованы с помощью интегральных микросхем цифроуправляемых униполярных аналоговых ключей типа МАХ4661ЕАЕ.

Блок многоканального аналого-цифрового преобразования 19 (БМАЦП) реализован с помощью интегральных аналого-цифровых преобразователей МАХ1324 СОМ 3.

Блоки моделирования фаз А, В и С шунтового трансформатора 20 (БМфАШТ), 21 (БМфВШТ), 22 (БМфСШТ), блоки моделирования фаз А, В и С реактора 33 (БМфАР), 34 (БМфВР), 35 (БМфСР), блоки моделирования фаз А, В и С сериесного трансформатора 53 (БМфАСТ), 54 (БМфВСТ), 55 (БМфССТ) реализованы с помощью интегральных микроэлектронных цифро-аналоговых преобразователей AD534KDZ и операционных усилителей типа OP2177ARZ-REEL7.

Блоки формирования напряжения 23 (БФНШТ) и 56 (БФНСТ) реализованы с помощью серийных интегральных микросхем цифроуправляемых униполярных аналоговых ключей МАХ4661ЕАЕ и операционных усилителей OP2177ARZ-REEL7.

Преобразователи напряжение-ток 24 (ПНТ1), 25 (ПНТN1), 26 (ПНТN2), 27 (ПНТ2), 28 (ПНТN3), 29 (ПНТN4), 30 (ПНТ3), 31 (ПНТN5), 32 (ПНТN6), 36 (ПНТ4), 37 (ПНТ5), 38 (ПНТ6), 39 (ПНТ7), 40 (ПНТ8), 41 (ПНТ9), 57 (ПНТ10), 58 (ПНТ11), 59 (ПНТ12), 60 (ПНТ13), 61 (ПНТ14), 62 (ПНТ15), 63 (ПНТ16), 64 (ПНТ17), 65 (ПНТ18) реализованы с помощью интегральных микросхем AD5443YRMZ.

Устройство для моделирования фазоповоротного устройства в энергетических системах работает следующим образом.

При подаче напряжения питания из базы данных центрального процессора 16 (ЦП) или из базы данных персонального компьютера/сервера электрические сигналы в цифровом виде, характеризующие параметры конструктивных элементов моделируемого фазоповоротного устройства, передают и записывают в регистры памяти цифро-аналоговых преобразователей блоков моделирования фаз А, В и С шунтового трансформатора 20 (БМфАШТ), 21 (БМфВШТ), 22 (БМфСШТ), блоков моделирования фаз А, В и С реактора 33 (БМфАР), 34 (БМфВР), 35 (БМфСР) и блоков моделирования фаз А, В и С сериесного трансформатора 53 (БМфАСТ), 54 (БМфВСТ), 55 (БМфССТ).

В тоже время из базы данных процессора коммутации 17 (ПК) соответствующие электрические сигналы в цифровом виде подают на управляющие входы цифроуправляемых аналоговых ключей блоков моделирования продольно-поперечных коммутаций 1 (БМППК1), 2 (БМППК2), 4 (БМППК3), 5 (БМППК4), 6 (БМППК5), 8 (БМППК6), 10 (БМППК7), 11 (БМППК8), 13 (БМППК9) и 15 (БМППК10), определяя их состояние.

Электрические сигналы в цифровом виде, формируемые в процессоре коммутации 17 (ПК), согласно алгоритму управления, подают в блок моделирования тиристорного коммутатора 9 (БМТК) на управляющие входы блоков цифроуправляемых аналоговых ключей 45 (БЦАК1), 46 (БЦАК2), 47 (БЦАК3), 48 (БЦАК4), 49 (БЦАКN1), 50 (БЦАКN2), 51 (БЦАКN3), 52 (БЦАКN4) блока моделирования тиристорного моста фазы А (БМТМфА) и аналогичных блоков цифроуправляемых аналоговых ключей блоков моделирования тиристорных мостов фаз В 43 (БМТМфВ) и С 44 (БМТМфС).

В зависимости от включенного или отключенного состояния цифроуправляемых аналоговых ключей блоков моделирования продольно-попере