Расширение согласующего протокола для индикации состояния транзакции

Иллюстрации

Показать всеИзобретение относится к технологиям сетевой связи. Технический результат заключается в повышении скорости передачи данных. Предложен машиночитаемый информационный носитель, на котором записаны программные команды для реализации согласующего протокола. Устройство обработки данных считывает программные команды для принуждения устройства обработки данных к осуществлению способа, содержащего: отправку запроса на данные к удаленному процессору, получение процессором ответа от удаленного процессора, причем ответ включает в себя состояние транзакции удаленной транзакции на удаленном процессоре, и добавление процессором состояния транзакции удаленной транзакции на удаленном процессоре в таблицу отслеживания взаимного вмешательства локальных транзакций. 3 н. и 14 з.п. ф-лы, 18 ил., 4 табл.

Реферат

Уровень техники

В общем, настоящее изобретение относится к протоколам запросов и ответов и, прежде всего, к расширению согласующего протокола для индикации состояния транзакции.

Для удовлетворения растущих потребностей в рабочей нагрузке продолжает значительно возрастать число ядер центрального процессора (ЦП) на микросхеме и число присоединенных к совместно используемой памяти ядер ЦП. Растущее число ЦП, взаимодействующих при обработке одной рабочей нагрузки налагает значительные требования на масштабируемость программного обеспечения; например, защищенные традиционными семафорами совместно используемые очереди или структуры данных становятся горячими точками и приводят к подлинейным n-вариантным кривым масштабирования. Традиционно этому противостояли посредством реализации мелкомодульной блокировки в программном обеспечении, и с помощью межсоединений с малым запаздыванием/высокой пропускной способностью в аппаратных средствах. Реализация мелкомодульной блокировки для улучшения масштабируемости программного обеспечения может быть очень сложной и подверженной ошибкам, а при современных частотах ЦП, запаздывания аппаратных межсоединений ограничиваются физическими размерами микросхем и систем, а также скоростью света.

Была введена аппаратная транзакционная память (НТМ, или в этом обсуждении, просто ТМ), в которой называемая транзакцией группа команд, при рассмотрении со стороны других центральных процессоров (ЦП) и подсистемы ввода-вывода, воздействует элементарным способом на структуру данных в памяти (элементарная операция также известна в другой литературе как блокированная многопоточная или преобразованная в последовательную форму). Транзакция выполняется в оптимистичном варианте без получения блокировки, но возможным также является возникновение необходимости в прекращении и в повторном выполнении транзакции, если операция выполняющейся транзакции на ячейке памяти находится в противоречии с другой операцией на той же самой ячейке памяти. Ранее были предложены реализации программной транзакционной памяти для поддержки программной транзакционной памяти (ТМ).

Сущность изобретения

Варианты осуществления включают в себя способ, систему и машиночитаемый информационный носитель для реализации согласующего протокола. Запрос на данные отправляется к удаленному процессору. Процессор получает ответ от удаленного процессора, и ответ имеет состояние транзакции, свойственное удаленной транзакции на удаленном процессоре. Процессор добавляет состояние удаленной транзакции на удаленном процессоре в таблицу отслеживания взаимного вмешательства локальных транзакций. Состояние удаленной транзакции добавляется к транзакционному диагностическому блоку

Краткое описание нескольких видов на чертежах

Рассматриваемый в качестве вариантов осуществления объект изобретения, прежде всего, указан и недвусмысленно заявлен в пунктах формулы изобретения в конце технического описания. Упомянутые ранее и другие признаки и

преимущества вариантов осуществления являются очевидными из последующего подробного описания, рассматриваемого совместно с сопровождающими чертежами, на которых:

Фиг. 1 изображает схематическую блок-диаграмму типового окружения транзакционной памяти для множественных процессоров (ЦП)/ядер согласно варианту осуществления,

Фиг. 2 изображает схематическую блок-диаграмму, показывающую транзакционный процессор согласно варианту осуществления,

Фиг. 3 изображает схематическую блок-диаграмму типовых компонентов транзакционного процессора (ЦП), показанных на фиг. 1 и 2, согласно варианту осуществления,

Фиг. 4 изображает схематическую блок-диаграмму компьютерной системы, имеющей компоненты, подобные многопроцессорным системам, показанным на фиг. 1-3, для предоставления запросов и ответов в аппаратном окружении транзакционной памяти согласно варианту осуществления,

Фиг. 5 изображает типовые протокольные запрос и ответ согласно варианту осуществления,

Фиг. 6 изображает образцовый протокольный запрос согласно варианту осуществления,

Фиг. 7 изображает блок-схему генерации протокольного запроса посредством процессора, создающего запрос на данные согласно варианту осуществления,

Фиг. 8 изображает блок-схему обработки запроса посредством приемного/удаленного процессора, который принимает запрос и отправляет ответ согласно варианту осуществления,

Фиг. 9 изображает блок-схему, показывающую обработку транзакции посредством процессора согласно варианту осуществления,

Фиг. 10 изображает протокольный запрос и новый протокольный ответ согласно варианту осуществления,

Фиг. 11 изображает протокольный запрос на запись и новый ответ согласно варианту осуществления,

Фиг. 12 изображает блок-схему, показывающую обработку согласующего запроса посредством приемного/удаленного процессора, который принимает запрос согласно варианту осуществления,

Фиг. 13 изображает блок-схему, показывающую создание протокольного запроса и его обработку посредством запрашивающего процессора согласно варианту осуществления,

Фиг. 14 изображает блок-схему, показывающую обработку транзакции посредством процессора согласно варианту осуществления,

Фиг. 15 изображает блок-схему, показывающую, как процессор отвечает на индикацию вмешательства в накопительной таблице локального отслеживания взаимного вмешательства транзакций согласно варианту осуществления,

Фиг. 16 изображает блок-схему, показывающую, как процессор отвечает на индикацию вмешательства в накопительной таблице локального отслеживания взаимного вмешательства транзакций согласно варианту осуществления,

Фиг. 17 изображает способ обработки согласующего протокола согласно варианту осуществления, и

Фиг. 18 изображает машиночитаемый носитель согласно варианту осуществления.

Подробное описание

Многопроцессорные системы используют согласующие протоколы для поддержания взаимосогласованности между всеми кэшами в системе распределенной общей памяти. Когда делают запрос на данные от конкретного кэша, этот кэш выдает данные и обновляет свое состояние таким образом, что он более не имеет данных или, что данные не содержатся исключительно в нем. Если процессор находится в процессе транзакционного выполнения, и от его кэша запрашиваются данные, которые являются частью транзакции, то процессор прекращает транзакцию и отправляет данные.

Отсутствует какая-либо информация о том, вызвал ли запрос прекращение другой транзакции. В некоторых случаях является желательным уведомление исходного инициатора запроса о воздействии запроса на другую транзакцию для предоставления обратной связи и для предоставления формирователю инициатора запроса возможности адаптации его выполнения, например обнаружения сценариев динамической взаимоблокировки, а также адресации к другим понижающим производительность сценариям.

Согласно варианту осуществления согласующий протокол расширяется для включения в него дополнительной информации по состоянию транзакции. Когда процессор находится в процессе транзакционного выполнения, согласующий запрос может вызвать прекращение этого выполнения, например вследствие того, что данные являются частью транзакционного набора значений для считывания или записи, и обнаруживается конфликт. Согласующий протокольный запрос расширяется за счет дополнительной информации о том, что получающий согласующий запрос процессор прервал транзакцию во время транзакционного выполнения согласно вариантам осуществления.

Работа «Архитектура системы команд Power ISA™ версия 2.07» (Power ISA™ Version 2.07), опубликованная 22 мая 2013 от IBM® и включенная в настоящий документ путем отсылки в полном объеме, предлагает типовую архитектуру системы команд (ISA) компьютера с сокращенной системой команд (RISC). Кроме того, руководство «Принципы работы Z-архитектуры» (z/Architecture Principles of Operation SA22-7832-09) (август 2012) от IBM®, включенное в настоящий документ путем отсылки в полном объеме, предлагает типовую архитектуру системы команд для CISC (компьютера со сложной системой команд).

Исторически, компьютерная система или процессор имели только единственный процессор (иначе, обрабатывающий блок или центральный процессор). Процессор включает в себя процессор команд (IPU), устройство обработки ветвлений, устройство управления памятью и т.п. Такие процессоры были способны к единовременному выполнению единственного программного потока. Были разработаны операционные системы, способные работать с разделением времени процессора посредством диспетчеризации подлежащей выполнению на процессоре программы в течение некоторого промежутка времени и последующей диспетчеризации подлежащей выполнению на процессоре другой программы в течение другого промежутка времени. По мере развития технологии, к процессору зачастую добавлялись кэши подсистемы памяти, а также комплексная динамическая трансляция адресов, включающая в себя ассоциативные буферы трансляции (TLB). IPU, как таковой, зачастую упоминается как процессор. По мере продолжения развития технологии, весь процессор мог быть упакован на единственном полупроводниковом чипе или кристалле; такой процессор называют микропроцессором. Затем были разработаны процессоры, которые содержали несколько IPU; такие процессоры зачастую называют многопроцессорными системами. Каждый такой процессор многопроцессорной компьютерной системы (процессор) может включать в себя отдельные или совместно используемые кэши, интерфейсы памяти, системную шину, механизм преобразования адресов и т.п. Виртуальная машина и эмуляторы архитектуры системы команд (ISA) добавили к процессору уровень программного обеспечения, который предоставил виртуальной машине множественные «виртуальные процессоры» (иначе, процессоры) посредством разделенного по времени использования единственного IPU в единственном аппаратном процессоре. По мере дальнейшего развития технологии были разработаны многопоточные процессоры, обеспечивающие единственному аппаратному процессору, имеющему единственный многопоточный IPU, возможность одновременного выполнения потоков различных программ; тем самым каждый поток многопоточного процессора представляется операционной системе в качестве процессора. По мере дальнейшего развития технологии стало возможным размещение множественных процессоров (каждый из которых имеет IPU) на единственном полупроводниковом чипе или кристалле. Эти процессоры называют ядрами процессора или просто ядрами. Тем самым такие термины, например, как процессор, центральный процессор, обрабатывающее устройство, микропроцессор, сердцевина, ядро процессора, поток процессора и поток зачастую используют взаимозаменяемым образом. Аспекты вариантов осуществления настоящего документа могут быть осуществлены посредством произвольных процессоров, включающих в себя указанные выше, без отступления от представленных в настоящем документе принципов. Когда в настоящем документе используется термин «поток» или «процессорный поток», подразумевается, что особое преимущество варианта осуществления может быть реализовано в процессорном потоке.

Выполнение транзакции в вариантах осуществления на основе процессоров Intel®

В руководстве «Справочник по программированию расширений системы команд архитектуры Intel®» (Intel® Architecture Instruction Set Extensions Programming Reference), от февраля 2012, включенном в настоящий документ путем отсылки в полном объеме, в главе 8 указано, помимо прочего, что в многопоточных применениях преимущество увеличения числа ядер ЦП может быть использовано для достижения более высокой производительности. Однако разработка многопоточных применений требует от программистов понимания и принятия во внимание совместного использования данных в среде множественных потоков. Доступ к совместно используемым данным обычно требует применения механизмов синхронизации. Такие механизмы синхронизации используют для обеспечения обновления множественными потоками совместно используемых данных посредством преобразования в последовательную форму операций, которые применяют к совместно используемым данным, зачастую с помощью критической секции, которая защищена блокировкой. Поскольку преобразование в последовательную форму ограничивает параллелизм, программисты пытаются ограничить издержки вследствие синхронизации.

Расширения транзакционной синхронизации Intel® (Intel® Transactional Synchronization Extensions) (Intel® TSX) позволяют процессору динамически выявлять необходимость преобразования потоков в последовательную форму посредством защищенных блокировкой критических секций, и выполнять такое преобразование в последовательную форму только при наличии необходимости. Это позволяет процессору обнаруживать и использовать параллелизм, который скрыт при применении вследствие динамически ненужной синхронизации. С помощью Intel TSX задаваемые программистами области кода (также называемые «транзакционными областями» или просто «транзакциями») выполняются транзакционным способом. Если транзакционное выполнение завершается успешно, то все операции с памятью, выполненные в пределах транзакционной области, представляются произошедшими мгновенно при рассмотрении с позиции других процессоров. Процессор делает осуществляемые в пределах транзакционной области операции с памятью выполняемой транзакции видимыми для других процессоров только в том случае, когда происходит успешная фиксация, то есть, когда выполнение транзакции успешно завершается.

Этот способ зачастую называют элементарной фиксацией.

Intel TSX вводит два программных интерфейса для задания областей кода для транзакционного выполнения. Аппаратное исключение блокировок (Hardware Lock Elision) (HLE) представляет собой обратно совместимое расширение системы команд (содержат префиксы XACQUIRE и XRELEASE) для задания транзакционных областей. Ограниченная транзакционная память (Restricted Transactional Memory) (RTM) представляет собой новый интерфейс системы команд для программистов (содержит команды XBEGIN, XEND и XABORT) для описания транзакционных областей более гибким способом, нежели это возможно с помощью HLE. HLE подходит для программистов, которые предпочитают обратную совместимость обычной модели программирования взаимного исключения и хотят выполнять оснащенное HLE программное обеспечение на устаревшем оборудовании, но также хотят использовать преимущества возможности нового исключения блокировок на аппаратных средствах с поддержкой HLE. RTM подходит для программистов, которые предпочитают гибкий интерфейс аппаратным средствам транзакционного выполнения. Кроме того, Intel TSX также вводит команду XTEST. Эта команда позволяет программному обеспечению запрашивать, осуществляет ли логический процессор транзакционным способом выполнение в транзакционной области, заданной посредством HLE или RTM.

Поскольку успешное транзакционное выполнение обеспечивает элементарную фиксацию, процессор выполняет область кода в оптимистическом варианте без явной синхронизации. Если синхронизация была ненужной для этого конкретного выполнения, выполнение может быть зафиксировано без какого-либо межпоточного преобразования в последовательную форму. Если процессор не способен к элементарной фиксации, то оптимистическое выполнение терпит неудачу. Когда это происходит, процессор откатывает выполнение назад; данный процесс называют прекращением транзакции. При прекращении транзакции процессор сбрасывает все обновления, выполненные в используемой транзакцией области памяти, восстанавливает архитектурное состояние до вида, соответствующего полному отсутствию какого-либо оптимистического выполнения, и возобновляет выполнение нетранзакционным способом.

Процессор может выполнять прекращение транзакции по многим причинам. Первая причина прекращения транзакции проистекает из конфликтных доступов к памяти между выполняющим транзакционным способом логическим процессором и другим логическим процессором. Такие конфликтные доступы к памяти могут нарушить успешное транзакционное выполнение. Считываемые из транзакционной области адреса памяти составляют считываемый набор транзакционной области, а записываемые в пределах транзакционной области адреса составляют записываемый набор транзакционной области. Intel TSX поддерживает считываемые и записываемые наборы на уровне детализации, соответствующем строке кэша. Конфликтный доступ к памяти происходит в том случае, когда другой логический процессор или считывает ячейку памяти, которая является частью записываемого набора транзакционной области, или записывает в ячейку памяти, которая является частью либо считываемого, либо записываемого набора транзакционной области. Конфликтный доступ обычно означает, что для этой области кода требуется преобразование в последовательную форму. Поскольку Intel TSX обнаруживает конфликты данных на соответствующем строке кэша уровне детализации, несвязанные местоположения данных, размещенные в той же самой строке кэша, обнаруживаются как конфликты, которые приводят к прекращениям транзакций. Прекращения транзакций могут также произойти вследствие ограниченности транзакционных ресурсов. Например, объем данных, к которому получают доступ в области, может превысить заданную для конкретной реализации производительность. Кроме того, прекращения транзакций могут вызывать некоторые команды и системные события. Частые прекращения транзакций приводят к возникновению непродуктивных циклов и к снижению эффективности.

Аппаратное исключение блокировок

Аппаратное исключение блокировок (HLE) предоставляет обратно совместимый интерфейс системы команд для использования программистами транзакционного выполнения. HLE вводит две новые командные префиксные рекомендации: XACQUIRE и XRELEASE.

В рамках HLE программист добавляет префикс XACQUIRE перед командой, которая используется для получения, защищающей критическую секцию блокировки. Процессор обрабатывает префикс в качестве рекомендации к пропусканию записи, связанной с операцией получения блокировки. Несмотря на то, что получение блокировки имеет ассоциированную с блокировкой операцию записи, процессор не добавляет адрес блокировки к записываемому набору транзакционной области, равно он не делает к блокировке каких-либо запросов на запись. Вместо этого адрес блокировки добавляется к считываемому набору. Логический процессор входит в процесс транзакционного выполнения. Если блокировка была доступной перед получением командой префикса XACQUIRE, то все другие процессоры продолжают впоследствии рассматривать блокировку как доступную. Поскольку функционирующий транзакционным способом логический процессор не добавляет адрес блокировки к его записываемому набору и не выполняет видимых извне операций записи в блокировке, другие логические процессоры могут считывать блокировку без создания конфликта данных. Это позволяет другим логическим процессорам также вводить и одновременно выполнять защищенную блокировкой критическую секцию. Процессор автоматически обнаруживает любые конфликты данных, которые происходят в процессе транзакционного выполнения и, при необходимости, выполняет прекращение транзакции.

Хотя пропускающий процессор не выполняет каких-либо внешних операций записи в блокировке, аппаратные средства обеспечивают программный порядок операций на блокировке. Когда пропускающий процессор как таковой считывает значение блокировки в критической секции, это представляется, как если процессор получает блокировку, то есть считывание возвращает непропущенное значение. Такое поведение позволяет выполнению HLE быть функционально эквивалентным выполнению без префиксов HLE.

Префикс XRELEASE может быть добавлен перед командой, которая используется для разблокирования защищающей критическую секцию блокировки. Разблокирование блокировки включает в себя производство записи в блокировке. Если команда должна восстановить значение блокировки к значению, которое блокировка имела до снабжения префиксом XACQUIRE операции получения блокировки на той же самой блокировке, то процессор пропускает внешний запрос на запись, связанный с разблокированием блокировки, и не добавляет адрес блокировки к записываемому набору. В этом случае процессор пытается фиксировать процесс транзакционного выполнения.

С помощью HLE в случае, когда множественные потоки выполняют защищенные одной блокировкой критические секции, но не выполняют каких-либо конфликтующих операций на данных друг друга, потоки могут выполняться одновременно и без преобразования в последовательную форму. Несмотря на то, что программное обеспечение использует операции получения блокировки на общей блокировке, аппаратные средства распознают это, пропускают блокировку и выполняют критические секции на двух потоках, не требуя какой-либо коммуникации через блокировку, если такая коммуникация оказывается динамически ненужной.

Если процессор оказывается неспособен к выполнению области транзакционным способом, процессор выполняет область нетранзакционным способом и без пропускания. Оснащенное HLE программное обеспечение имеет те же самые гарантии прогресса продвижения, что и базовое, основанное на блокировках выполнение без HLE. Для успешного выполнения, HLE блокировка и код критической секции должны следовать определенным рекомендациям. Эти рекомендации затрагивают только производительность; отказ в следовании этим рекомендациям не приведет к функциональному отказу. Аппаратные средства без поддержки HLE игнорируют префиксные рекомендации XACQUIRE и XRELEASE и не выполняют какого-либо пропускания, поскольку эти префиксы соответствуют префиксам REPNE/REPE IA-32, которые игнорируются на командах, где являются допустимыми XACQUIRE и XRELEASE. Важно отметить, что HLE является совместимым с существующей, основанной на блокировках моделью программирования. Неправильное использование рекомендаций не вызывает функциональных ошибок, хотя оно может выявить уже имеющиеся в коде скрытые ошибки.

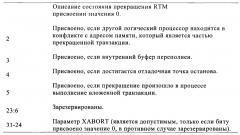

Ограниченная транзакционная память (RTM) предоставляет гибкий программный интерфейс для транзакционного выполнения. RTM предоставляет программистам три новые команды XBEGIN, XEND и XABORT для запуска, фиксирования и прекращения транзакционного выполнения.

Программист использует команду XBEGIN для задания начала транзакционной области кода, а команду XEND - для задания окончания транзакционной области кода. Если область RTM не могла быть успешно выполненной транзакционным способом, то команда XBEGIN принимает операнд, который предоставляет относительное смещение к возвратному адресу команды.

Процессор может прервать транзакционное выполнение RTM по нескольким причинам. Во многих случаях аппаратные средства автоматически обнаруживают условия транзакционного прекращения и перезапускают выполнение от возвратного адреса команды с архитектурным состоянием, соответствующим имеющемуся при запуске команды XBEGIN, и с регистром ЕАХ, обновленным для описания состояния прекращения.

Команда XABORT позволяет программистам явным образом прекращать выполнение области RTM. Команда XABORT принимает 8-разрядный текущий аргумент, который загружен в регистр ЕАХ и, таким образом, является доступным программному обеспечению после прекращения RTM. Команды RTM не имеют каких-либо ассоциированных с ними ячеек памяти для хранения данных. В то время как аппаратные средства не предоставляют гарантий относительно того, будет ли область RTM когда-либо успешно зафиксирована транзакционным способом, большинство следующих рекомендуемым директивам транзакций, как ожидается, успешно фиксируются транзакционным способом. Однако программисты должны всегда предоставлять альтернативную кодовую последовательность на возвратной ветви для гарантирования прогресса продвижения.

Это может быть столь же простым, как получение блокировки и выполнение заданной области кода нетранзакционным способом. Кроме того, транзакция, которая всегда прекращается на данной реализации, может завершиться транзакционным способом при последующей реализации. Поэтому программисты должны обеспечивать функциональное тестирование ветвей кода для транзакционной области и альтернативной кодовой последовательности.

Обнаружение поддержки HLE

Процессор поддерживает выполнение HLE, если CPUID.07H.EBX.HLE [bit 4] = 1. Однако приложение может использовать префиксы HLE (XACQUIRE и XRELEASE) без проверки наличия поддержки HLE процессором. Процессоры без поддержки HLE игнорируют эти префиксы и выполнят код без вхождения в процесс транзакционного выполнения.

Обнаружение поддержки RTM

Процессор поддерживает выполнение RTM, если CPUID.07H.EBX.RTM [bit 11] = 1. Приложение должно проверить наличие поддержки RTM процессором до использования команд RTM (XBEGIN, XEND, XABORT). Эти команды генерируют исключительное состояние #UD, когда используются на процессоре, который не поддерживает RTM.

Обнаружение команды XTEST

Процессор поддерживает команду XTEST, если он поддерживает HLE или RTM. Приложение должно проверить каждую из этих функциональных меток перед использованием команды XTEST. Эта команда генерирует исключительное состояние #UD, когда используется на процессоре, который не поддерживает HLE или RTM.

Запрос состояния транзакционного выполнения

Команда XTEST может быть использована для выявления транзакционного состояния заданной посредством HLE или RTM транзакционной области. Замечание: в то время как префиксы HLE игнорируются на процессорах, которые не поддерживают HLE, команда XTEST генерирует исключительное состояние #UD, когда используется на процессорах, которые не поддерживают HLE или RTM.

Требования для блокировок HLE

Для успешной фиксации выполнения HLE транзакционным способом блокировка должна удовлетворять конкретным требованиям, а доступ к блокировке должен следовать конкретным рекомендациям.

Снабженная префиксом XRELEASE команда должна восстанавливать значение пропущенной блокировки к значению, которое она имела перед получением блокировки. Это позволяет аппаратным средствам безопасно пропускать блокировки без добавления их к записываемому набору. Размер данных и адрес данных разблокирования блокировки (снабженной префиксом XRELEASE) команды должны соответствовать таковым для команды получения блокировки (снабженной префиксом XACQUIRE), и блокировка не должна пересекать границу строки кэша.

Программное обеспечение не должно записывать в пропущенную блокировку в транзакционной области HLE с помощью какой-либо иной команды, кроме снабженной префиксом XRELEASE команды, в противном случае такая запись может вызвать прекращение транзакции. Кроме того, рекурсивные блокировки (при которых поток многократно получает ту же самую блокировку без предварительного разблокирования блокировки) также могут вызывать прекращение транзакции. Следует обратить внимание на то, что программное обеспечение способно отслеживать результат пропущенного получения блокировки в критической секции. Такая операция считывания возвращает значение записи к блокировке.

Процессор автоматически обнаруживает нарушения этих рекомендаций и безопасно переходит к нетранзакционному выполнению без пропускания. Поскольку Intel TSX обнаруживает конфликты на уровне детализации строки кэша, записи в данных, расположенные на той же самой строке кэша, что и пропущенная блокировка, могут быть обнаружены как конфликты по данным посредством других логических процессоров, пропускающих ту же самую блокировку.

Транзакционное вложение

Как HLE, так и RTM поддерживают вложенные транзакционные области. Однако прекращение транзакции восстанавливает состояние операции, которая запустила транзакционное выполнение: либо наиболее удаленной снабженной префиксом XACQUIRE пригодной к выполнению в HLE команды, либо наиболее удаленной команды XBEGIN. Процессор обрабатывает все вложенные транзакции как одну транзакцию.

Вложение и исключение HLE

Программисты могут вкладывать области HLE вплоть до реализации заданной глубины MAX_HLE_NEST_COUNT. Каждый логический процессор отслеживает отсчет вложений внутренним образом, но этот отсчет является недоступным для программного обеспечения. Снабженная префиксом XACQUIRE пригодная к выполнению в HLE команда дает приращение отсчету вложений, а снабженная префиксом XRELEASE пригодная к выполнению в HLE команда уменьшает его значение. Логический процессор входит в процесс транзакционного выполнения, когда отсчет вложений переходит от ноля до единицы. Логический процессор пытается произвести фиксацию только при достижении отсчетом вложений нулевого значения. Прекращение транзакции может произойти при превышении отсчетом вложений значения MAX_HLE_NEST_COUNT.

В дополнение к поддержке вложенных областей HLE процессор также может пропускать множественные вложенные блокировки. Процессор отслеживает блокировку для пропускания, начинающуюся со снабженной префиксом XACQUIRE пригодной к выполнению в HLE команды для этой блокировки, и оканчивающуюся снабженной префиксом XRELEASE пригодной к выполнению в HLE командой для той же самой блокировки. Процессор способен в любой момент отслеживать число блокировок до значения MAX_HLE_ELIDED_LOCKS. Например, если реализация поддерживает MAX_HLE_ELIDED_LOCKS со значением два и, если программист вкладывает три идентифицированные в HLE критические секции (посредством выполнения снабженной префиксом XACQUIRE пригодной к выполнению в HLE команды на трех различных блокировках без выполнения вмешательства снабженной префиксом XRELEASE пригодной к выполнению в HLE команды на какой-либо из блокировок), то первые две блокировки пропускаются, а третья не пропускается (но добавляется к записываемому набору транзакции). Тем не менее, выполнение и далее продолжится транзакционным способом. После того, как был встречен префикс XRELEASE для одной из числа двух пропущенных блокировок, пропускается последующая блокировка, полученная посредством снабженной префиксом XACQUIRE пригодной к выполнению в HLE команды.

Процессор пытается фиксировать выполнение HLE, когда все пропущенные пары XACQUIRE и XRELEASE оказываются сопряженными, когда отсчет вложений принимает нулевое значение, а блокировки удовлетворяют требованиям. Если выполнение не может получить фиксацию элементарным образом, то выполнение переходит к нетранзакционному выполнению без пропускания, как если бы у первой команды не было префикса XACQUIRE.

Вложение RTM

Программисты могут вложить области RTM вплоть до специфичного для реализации значения MAX_RTM_NEST_COUNT. Логический процессор отслеживает отсчет вложений внутренним образом, но этот отсчет является недоступным для программного обеспечения. Команда XBEGIN дает приращение отсчету вложений, а команда XEND уменьшает значение отсчета вложений. Логический процессор пытается произвести фиксацию только при достижении отсчетом вложений нулевого значения. Прекращение транзакции происходит при превышении отсчетом вложений значения MAX_RTM_NEST_COUNT.

Вложение HLE и RTM

HLE и RTM предоставляют два альтернативных программных интерфейса для обеспечения общей функциональной способности транзакционного выполнения. Протекание процесса обработки транзакций является специфичным для конкретной реализации в том случае, когда HLE и RTM вкладываются друг в друга, например HLE в RTM или RTM в HLE. Однако во всех случаях, реализация должна содержать семантику HLE и RTM. Реализация может избрать игнорирование рекомендаций HLE при использовании в областях RTM, а также может вызывать прекращение транзакции при использовании команд RTM в областях HLE. В последнем случае переход от транзакционного к нетранзакционному выполнению происходит беспрепятственно, поскольку процессор повторно выполняет область HLE, фактически не делая пропускания, а затем выполняет команды RTM.

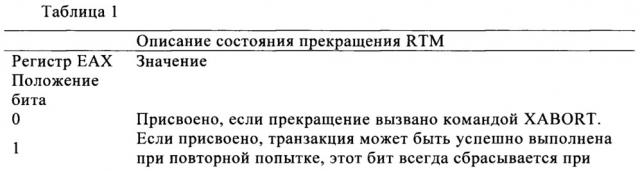

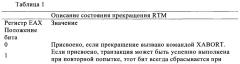

Описание состояния прекращения

RTM использует регистр ЕАХ для сообщения о состоянии прекращения программному обеспечению. После прекращения RTM регистр ЕАХ имеет следующее описание.

Состояние прекращения ЕАХ для RTM предоставляет только причины прекращений. Как таковое оно не кодирует, произошло ли прекращение или фиксация для области RTM. Значение ЕАХ может быть равно 0 после прекращения RTM. Например, команда CPUID, при использовании ее в области RTM, вызывает прекращение транзакции и может не удовлетворять требованиям по присваиванию значений каким-либо битам ЕАХ. Это может привести к значению ЕАХ равному 0.

Упорядочивание памяти RTM

Успешная фиксация RTM принуждает все операции с памятью в области RTM представляться выполняемыми элементарным образом. Успешно зафиксированная область RTM, состоящая из XBEGIN, сопровождаемого XEND, даже без операций с памятью в области RTM, имеет ту же самую упорядочивающую семантику, что и снабженная префиксом LOCK команда. Команда XBEGIN не имеет ограждающей семантики. Однако если выполнение RTM прекращается, то все обновления памяти изнутри области RTM отбрасываются и делаются невидимыми для какого-либо другого логического процессора.

Поддержка оснащенного RTM отладчика

По умолчанию, любое исключительное состояние отладки в области RTM вызывает прекращение транзакции и перенаправляет поток управления к возвратному адресу команды при восстановлении архитектурного состояния и присвоении биту 4 в ЕАХ значения. Однако архитектура RTM предоставляет дополнительную возможность для позволения отладчикам программного обеспечения прекращения выполнения на исключительных состояниях отладки.

Если бит 11 из DR7 и бит 15 из IA3_2DEBUGCTL_MSR оба имеют значение 1, любое прекращение RTM вследствие исключительного состояния отладки (#DB) или исключительного состояния точки прекращения (#ВР) вызывает выполнение отката и перезапуск от команды XBEGIN вместо возвратного адреса. В этом сценарии регистр ЕАХ также восстанавливается в прошлом состоянии на точке команды XBEGIN.

Соображения по программированию

Ожидается, что типичные отождествляемые программистами области успешно выполняются транзакционным способом и фиксируются. Однако Intel TSX не предоставляет какой-либо гарантии на это. Транзакционное выполнение может быть прервано по нескольким причинам. Для использования в полной мере транзакционных возможностей программисты должны следовать определенным рекомендациям для повышения вероятности успешной фиксации их транзакционного выполнения.

В настоящем разделе обсуждаются различные события, которые могут вызвать прекращения транзакций.

Архитектура обеспечивает, что обновления, выполненные в пределах транзакции, которая впоследствии прекращает выполнение, никогда не становятся видимыми. Только зафиксированные транзакционные выполнения инициируют обновление архитектурного состояния. Прекращения транзакций никогда не вызывают функциональных отказов, но сказываются только на производительности.

Соображения относительно команд

Программисты могут безопасно использовать любую команду в транзакции (HLE или RTM) и могут использовать транзакции на любом уровне полномочий. Однако некоторые команды всегда прекращают транзакционное выполнение и вызывают беспрепятственный и безопасный переход выполнения на нетранзакционную ветвь.

Intel TSX позволяет использование наиболее распространенных команд внутри транзакций без вызывания прекращений. Последующие операции в транзакции обычно не вызывают прекращение:

• Операции на регистре указателя команд, регистрах общего назначения (GPR) и метках состояния (CF, SF, PF, AF и ZF), а также

• Операции на регистрах ХММ и YMM и регистре MXCSR.

Тем не менее, программисты должны проявлять осторожность при объединении в транзакционной области операций SSE и AVX. Объединение команд SSE, получающих доступ к регистрам ХММ, и команд AVX, получающих доступ к регистрам YMM, может послужить причиной прекращения транзакций. Программисты могут использовать в транзакциях снабженные префиксами REP/REPNE строковые операции.

Тем не менее, длинные строки могут вызывать прекращения. Кроме того, использование команд CFD и STD может вызывать прекращения, если они изменяют значение метки DF. Тем не менее, если значение DF равняется 1, то команда STD не вызыва