Самонастраивающееся цифровое сглаживающее устройство

Иллюстрации

Показать всеИзобретение относится к области автоматики и вычислительной техники. Технический результат – обеспечение автоматического выбора величины степени сглаживания числа задействованных каналов сглаживания, обратно пропорциональной скорости медианы процесса. Самонастраивающееся цифровое сглаживающее устройство состоит из блока сглаживания из m=64 последовательно соединенных каналов, регистра и мультиплексора; субблока расчета скорости медианы процесса (МП) из буфера регистровой памяти, блока инвертора и сумматора; субблока подсчета приращений скорости МП, содержащего два регистра хранения текущей и предыдущей дискрет скорости МП, компаратора, трех элементов И и 4-разрядного счетчика приращений; схемы тактирования субблока подсчета приращений; субблока выбора степени сглаживания по скорости МП, содержащего компаратор, регистр сдвига, 4-разрядный счетчик, блока инверторов, двухвходового и трехвходового элементов И; узла тактирования субблока выбора степени сглаживания, содержащего элемент задержки, трехвходовый элемент ИЛИ, триггер, генератор импульсов и элемент И; субблока коррекции степени сглаживания при снижении скорости МП, содержащего триггер, два элемента И, 7-разрядный счетчик и инвертор. 6 ил., 3 табл.

Реферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сглаживания стационарных и нестационарных случайных процессов.

Известно многоканальное цифровое сглаживающее устройство (а.с. СССР №686034, МПК G06F 15/32, бюл. №34, 1979), содержащее m последовательно соединенных каналов с параллельным накапливающим сумматором в каждом и формирователь тактов. Устройство функционально ограничено.

Наиболее близким по технической сущности к заявляемому устройству является, выбранное в качестве прототипа, многоканальное цифровое сглаживающее устройство (а.с. СССР №748417, МПК G06F 15/32, бюл. №26, 1980), содержащее формирователь тактов и m последовательно соединенных каналов, каждый из которых содержит комбинационный сумматор и регистр. Устройство также функционально ограничено.

Сглаживаемый входной дискретный сигнал, обычно аддитивной структуры, включает в себя флуктуации, шумы, помехи и выделяемую детерминированную основу (медиану) случайного процесса. Последняя может иметь широкий спектр изменения по скорости: от постоянной или медленно меняющейся до высокой. В аналогах и прототипе для повышения точности (эффективности) сглаживания, т.е. минимизации среднеквадратического отклонения (СКО), задают достаточно большое фиксированное число каналов сглаживания m (см. фиг. 4). Однако, если на вход устройства поступает нестационарная быстро меняющаяся дискретная последовательность (например, почти скачок), то на выходе устройства, в силу интегрирующего характера его работы, возникает фазовый сдвиг Δt (запаздывание) выходных дискрет, искажающий реальный ход изменения медианы процесса (см. Магданов Г.С. Об одном частном случае реализации оператора экспоненциального сглаживания/ СО АН СССР, Автометрия, №5, 1982, с. 85), причем Δt=mT, где Т - цикл работы устройства.

С увеличением числа (m) задействованных каналов сглаживания, т.е. повышения качества фильтрации случайных помех, увеличивается фазовый сдвиг и, как следствие (см. фиг. 5), снижается реакция устройства на изменение скорости медианы процесса (МП). Таким образом, степень сглаживания и реакция устройства на рост (или снижение) скорости МП являются противоречащими друг другу требованиями (см. Чуев Ю.В. «Прогнозирование количественных характеристик процессов» / «СР», 1975, гл. 4, с. 145-149).

Техническая задача для предлагаемого устройства заключается в автоматическом выборе величины степени сглаживания m (числа задействованных каналов сглаживания) обратно пропорциональной скорости медианы процесса, т.е. для стационарных и медленно меняющихся процессов степень сглаживания должна быть достаточно высокой, а для динамичных (быстро меняющихся) процессов ее следует выбирать минимальной.

Поэтому, в самонастраивающееся цифровое сглаживающее устройство, в состав которого входят: блок сглаживания, содержащий мультиплексор, регистр адреса и m=64 последовательно соединенных каналов, каждый из которых состоит из сумматора и регистра, выходы m=1, 2, 4, 8, 16, 32 и 64-го каналов заведены на информационные входы мультиплексора, адресный вход которого подключен к выходу регистра адреса, выход блока сглаживания является информационным выходом (уn), а вход первого канала - информационным входом (хn) устройства; субблок расчета скорости медианы процесса (МП), содержащий буфер регистровой памяти (предыстории входного дискретного процесса), блок инверторов, сумматор и схему формирования абсолютного значения скорости МП из блока инверторов и мультиплексора, выход которого является информационным выходом субблока; субблок подсчета приращений скорости процесса, содержащий два последовательно соединенных регистра хранения текущей y'n[(wT)] и предыдущей у'n[(w-l)T)] дискреты скорости МП, компаратор, два элемента И, 4-х разрядный счетчик приращений и третий элемент И; схема тактирования субблока подсчета приращений, содержащая элемент задержки, триггер, элемент И и регистр сдвига, для решения поставленной задачи введены субблок выбора степени сглаживания по скорости медианы процесса, содержащий компаратор, регистр сдвига, 4-х разрядный счетчик, блок инверторов, двухвходовой и трехвходовой элементы И; узел тактирования субблока выбора степени сглаживания, содержащий элемент задержки, трехвходовой элемент ИЛИ, триггер, генератор импульсов и элемент И; субблок коррекции степени сглаживания на отрицательной динамике (при снижении) скорости МП, содержащий триггер, первый элемент И, 7-ми разрядный счетчик, второй элемент И и инвертор, причем вход установки в «1» триггера субблока коррекции соединен с выходом третьего элемента И субблока подсчета приращений, а прямой выход триггера через инвертор заведен на третий вход трехвходового элемента И субблока выбора степени сглаживания, в котором на младший (первый) разряд регистра сдвига заведен высокий уровень логической «1», шина сдвига регистра, счетный вход счетчика, первый вход двухвходового элемента И и второй вход трехвходового элемента И подключены к выходу элемента И узла тактирования, шина установки в «0» счетчика и шина записи «1» в регистр сдвига соединены с тактирующим входом устройства, выход счетчика через блок инверторов заведен на вход регистра адреса блока сглаживания, а выход 4-го разряда счетчика - на второй вход двухвходового элемента И, выход которого соединен с шиной сброса в «0» регистра адреса блока сглаживания и со вторым входом элемента ИЛИ узла тактирования, шина записи в регистре адреса блока сглаживания подключена к первому входу элемента ИЛИ узла тактирования и к выходу трехвходового элемента И субблока выбора степени сглаживания, выход регистра сдвига которого подсоединен к первому (А) информационному входу компаратора с монтажным сдвигом на один разряд вправо (в сторону младших разрядов), второй (В) информационный вход компаратора, монтажно сдвинутый на (М) разрядов вправо (в сторону младших разрядов), подключен к выходу субблока расчета скорости МП, а управляющий выход соотношения (А>В) компаратора соединен с первым входом первого трехвходового элемента И субблока.

Сущность изобретения поясняется чертежами, на которых изображены: фиг. 1 - блок-схема предлагаемого устройства; фиг. 2 - блок-схема одного канала блока сглаживания; фиг. 3 - схема формирования абсолютного значения скорости МП; фиг. 4 - метрологическая характеристика (эффективность) блока сглаживания на m=64 канала; фиг. 5 - реакция (фазовый сдвиг, запаздывание) устройства на скачок МП; фиг. 6 - пример оценки фазового сдвига (запаздывания) выходной дискреты устройства для разных скоростей медианы входного процесса; приложение 1 и 2 - результаты моделирования работы устройства на ЭВМ при обработке нестационарных случайных процессов.

Известны формулы численного дифференцирования для равноотстоящих точек, выраженные через значения функции в этих точках (Демидович Б.П. и Марон И.А. Основы вычислительной математики. М., «ФМ», 1960, гл. XV, § 4, стр. 573), в частности, для трех точек имеем следующую формулу центральной производной:

где уп, Уп-1, Уп-2 - соответственно, первая (текущая), вторая и третья (конечная) расчетные точки (ординаты) буфера хранения предыстории входной сглаженной дискретной последовательности.

В численном анализе - это система равноотстоящих точек с шагом h, переходя в реальный масштаб времени и выбирая две точки (ординаты) буфера предыстории (текущую и конечную) получим следующую модификацию формулы вычисления скорости медианы сглаживаемого случайного процесса:

где Н=2h - временной интервал замера скорости; уп и уп-Н - текущая и конечная ординаты буфера предыстории; Н=NT, где N - количество регистров в буфере, Т - цикл работы устройства.

Устройство содержит (см. фиг. 1) блок сглаживания 1, состоящий из многоканального сглаживающего устройства 2 (см. авт. св. СССР №748417, кл. G06F 15/32, бюл. №26, 1980) каскадной структуры с m=64 последовательно соединенными каналами 3 (см. фиг. 2), каждый из которых содержит сумматор 4 и регистр 5, мультиплексора 6 и регистра 7 хранения адреса (к) числа задействованных каналов сглаживания m=2k; субблок 8 расчета скорости медианы процесса, содержащий буфер регистровой памяти предыстории процесса из N последовательно соединенных регистров 9, блок инверторов 10, сумматор 11 и схему 12 формирования абсолютного значения скорости (|у'п|) из блока инверторов 13 и мультиплексора 14; субблок 15 выбора степени сглаживания (m) по скорости медианы процесса, содержащий компаратор 16, регистр сдвига 17, счетчик 18, блок инверторов 19, двухвходовой элемент И 20 и трехвходовой элемент И 21; узел тактирования 22, включающий в себя элемент задержки 23, элемент ИЛИ 24, триггер 25, элемент И 26 и генератор импульсов 27 (fr); субблок 28 подсчета приращений скорости МП, содержащий последовательно соединенные регистры 29 и 30 (формирующие буфер предыстории приращений скорости МП), компаратор 31, два элемента И 32 и 33, 4-х разрядный счетчик 34 отрицательных приращений (снижения) скорости МП и третий элемент И 35; схема тактирования 36 субблока подсчета приращений, содержащая элемент задержки 37, триггер 38, элемент И 39 и регистр сдвига 40; субблок 41 коррекции степени сглаживания на отрицательной динамике (при снижении) скорости МП, содержащий триггер 42, первый элемент И 43, второй элемент И 44, 7-ми разрядный счетчик 45 и инвертор 46; информационные вход 47 (хn), выход 48 (уn) и тактирующий вход 49 (fт) устройства.

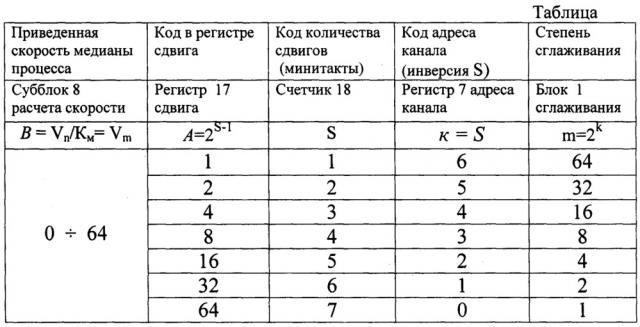

Алгоритм выбора величины степени (канала) сглаживания m обратно пропорциональной величине скорости медианы процесса построен на сравнении этих величин. Диапазон кодов степени сглаживания (1÷64) имеет семь фиксированных ступеней (каналов) m=1, 2, 4, 8, 16, 32 и 64 (см. фиг. 4), чтобы сделать код скорости медианы процесса соизмеримым с этим диапазоном, он делится на масштабный коэффициент Км:Vm=Vn/Км, где Vm - приведенная (виртуальная) скорость медианы процесса, причем ее максимальное значение не должно превышать предельного кода степени сглаживания в устройстве (m=64), т.е Vm макс.<64. Поскольку масштабный коэффициент Км зависит от емкости разрядной сетки аналого-цифрового преобразования (АЦП) входного сигнала, то для 12-ти разрядного АЦП: Км=4096/64=26, М=6; для 10-ти разрядного АЦП:Км=1024/64=24, М=4 и т.д.

Операция приведения кода скорости медианы процесса к требуемому диапазону (0÷64) путем деления ее на масштабный коэффициент производится монтажно - путем сдвига выходных шин субблока 8 расчета скорости МП на М разрядов вправо при вводе их на второй информационный вход компаратора 16 субблока 15 выбора степени сглаживания. Такая операция на блок-схеме (см. фиг. 1) обозначена кружочком.

Цикл работы устройства состоит из одного такта, тактирующий импульс (fт) со входа 49 устройства инициирует работу блока сглаживания 1, каждый канал которого реализует оператор экспоненциального сглаживания yn=1/2(xn+yn-1). Степень (канал) сглаживания m=2k выбирается мультиплексором 6 в соответствии с кодом адреса канала к=0÷6 в регистре 7. Ордината уn, предварительно сглаженного входного случайного процесса, с выхода 4-го канала блока 1 поступает в первый регистр 9 блока регистровой памяти субблока 8 расчета скорости процесса, одновременно производится перезапись (сдвиг) предшествующих ординат в соседние регистры 9 (т.е. формируется предыстория процесса), по формуле (2) рассчитывается скорость медианы процесса, а на выходе субблока 8 устанавливается ее абсолютное значение Vn. Тактирующий сигнал (fт) со входа 49 записывает «1» в первый (младший) разряд регистра сдвига 17, обнуляет счетчик 18 субблока 15 выбора степени (канала) сглаживания и установкой в «1» триггера 25 инициирует работу узла тактирования 22. Последний - вырабатывает от генератора 27 серию минитактов (fr), причем fr>>fт, первый и последующие из которых сдвигают «1» в регистре сдвига 17 влево на один разряд, формируя в нем потактно (S=l÷7), позиционный код А=2S-1, который в компараторе 16 сравнивается с кодом приведенной скорости процесса В=Vm, одновременно в счетчике 18 идет подсчет количества поступивших импульсов сдвига (S). Вышеперечисленные операции будут продолжаться до выполнения в компараторе 16 соотношения (А>В), высокий уровень («1») выходного сигнала которого, в этом случае, через трехвходовой элемент И 21 разрешит запись в регистр адреса 7 канала блока сглаживания 1 (через блок инверторов 19) инверсного кода счетчика 18 к=S, т.е. выберется канал сглаживания (m), соответствующий скорости медианы процесса. Одновременно, этим же сигналом минитакта с выхода элемента И 21 через элемент ИЛИ 24 обнулится триггер 25, завершив тем самым работу узла тактирования 22 и субблока 15 в этом такте. Инверсия кода количества сдвигов в счетчике 18 делает степень (номер канала) сглаживания m=2k обратно пропорциональной скорости медианы процесса (см. таблицу).

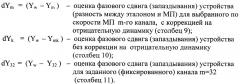

При отрицательной динамике (снижении, спаде) скорости МП, т.е. при переходе с любой скорости МП на меньшую, например, почти нулевую (стационарную) субблок 15 почти сразу устанавливает максимальную степень (канал) сглаживания m=64. Однако, в составе выходной дискреты этого канала, долгое время, доля прошлых дискрет с более высокими весами будет превалировать над долями текущих (свежих, с малыми весами) дискрет нового стационарного режима (см. фиг. 2, а.с. СССР №686034, кл. G06F 15/32, бюл. №34, 1979). Отсюда, существенный фазовый сдвиг (запаздывание) на выходе устройства в начале стационарного режима (см. Приложение 1 и 2, колонки 9 (dYm) и 10 (dYk), такты W=410÷473).

Субблок 28 определяет момент начала отрицательной динамики, т.е. переход на другую (меньшую) скорость МП, путем подсчета в 4-х разрядном счетчике 34 подряд восемь только отрицательных приращений (А<В) скорости МП: Δy'n=y'n[wT]-y'n[(w-1)]. Положительные приращения (А>В) обнуляют счетчик 34. Схема тактирования 36 с выхода регистра сдвига 40 формирует серию минитактов («а», «в» и «с») для инициации работы субблока 28. Высокий уровень («1») выхода 4-го разряда счетчика 34 разрешит минитактом «с» установить в «1» триггер 42 (dd=l) субблока 41 коррекции степени сглаживания на отрицательной динамике, который инверсным выходом 46 запретит запись (к) на новом стационарном режиме в регистр адреса 7, в последнем останется адрес (к) кода канала (степени) сглаживания предыдущего скоростного режима с минимальным (или существенно меньшим) фазовым сдвигом. Через 64 такта (ΔТ=64Т - интервал достаточный для смены текущих дискрет блока сглаживания 1 новой информацией) 7-й разряд счетчика 45 очередным тактовым сигналом со входа 49 обнулит триггер 42 (dd=0), последний инверсным выходом 46 разрешит работу субблока 15 на других скоростных режимах.

Для исключения неопределенности в работе блока сглаживания 1 при возможном превышении скорости МП (например, при скачке) максимального кода степени сглаживания Vm макс.>64 (m=64) выход 4-го разряда счетчика 18 (S=8) позволит через элемент И 20 очередному импульсу минитакта сбросить в «0» счетчик адреса 7 (к=0) - на выходе блока сглаживания установится минимальная степень (канал) сглаживания (m=1).

В приложении 1 и 2 приведены результаты моделирования работы устройства на ЭВМ:

где

Zn - случайный процесс, характеризующий помеху;

Yw - детерминированная основа (эталон) сглаживаемого случайного процесса (СП) Хп;

Ym - выходная дискрета сглаженного СП, медиана процесса (МП).

ПРИЛОЖЕНИЕ 1. Самонастраивающееся цифровое сглаживающее устройство

Результаты моделирования работы устройства при обработке (сглаживании) нестационарного случайного процесса (СП).

Параметры СП: Объем реализации n=500; Среднее квадратич. отклонение σ[Хn]=9.

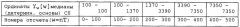

Параметры устройства: Временной интервал замера скорости H=NT=10T. Константа перехода на динамику (ТГ=1)при снижении скорости СП: Nd>10. Время (при ТГ=1) коррекции сглаженного СП после начала динамики Tkor=64T. Масштабный коэффициент приведения Км=8=23, М=3.

Н=10Т, М=3[Км=8], Tkor=64T, Nd=10T, Yw(Makc)=7350.

ПРИЛОЖЕНИЕ 2. Самонастраивающееся цифровое сглаживающее устройство

Результаты моделирования работы устройства при обработке (сглаживании) нестационарного случайного процесса (СП). Параметры СП: Объем реализации n=500; Среднее квадратич. отклонение σ[Хn]=9.

Параметры устройства: Временной интервал замера скорости H=NT=10T. Константа перехода на динамику (ТГ=1)при снижении скорости СП: Nd>10. Время (при ТГ=1) коррекции сглаженного СП после начала динамики Tkor=64T. Масштабный коэффициент приведения Км=8=23, М=3.

Н=10Т, М=3[Км=8], Tkor=64T, Nd=10T, Yw(Маkс)=7347.

Самонастраивающееся цифровое сглаживающее устройство, в состав которого входят: блок сглаживания, содержащий мультиплексор, регистр адреса и m=64 последовательно соединенных каналов, каждый из которых состоит из сумматора и регистра, выходы m=1, 2, 4, 8, 16, 32 и 64-го каналов заведены на информационные входы мультиплексора, адресный вход которого подключен к выходу регистра адреса, выход блока сглаживания является информационным выходом (yn), а вход первого канала - информационным входом (xn) устройства; субблок расчета скорости медианы процесса (МП), содержащий буфер регистровой памяти (предыстории входного дискретного процесса), блок инверторов, сумматор и схему формирования абсолютного значения скорости МП из блока инверторов и мультиплексора, выход которого является информационным выходом субблока; субблок подсчета приращений скорости процесса, содержащий два последовательно соединенных регистра хранения текущей y'n[(wT)] и предыдущей у'n[(w-1)T)] дискрет скорости МП, компаратор, два элемента И, 4-разрядный счетчик приращений и третий элемент И; схема тактирования субблока подсчета приращений, содержащая элемент задержки, триггер, элемент И и регистр сдвига, отличающееся тем, что в него введены: субблок выбора степени сглаживания по скорости медианы процесса, содержащий компаратор, регистр сдвига, 4-разрядный счетчик, блок инверторов, двухвходовый и трехвходовый элементы И; узел тактирования субблока выбора степени сглаживания, содержащий элемент задержки, трехвходовый элемент ИЛИ, триггер, генератор импульсов и элемент И; субблок коррекции степени сглаживания на отрицательной динамике (при снижении) скорости МП, содержащий триггер, первый элемент И, 7- разрядный счетчик, второй элемент И и инвертор, причем вход установки в «1» триггера субблока коррекции соединен с выходом третьего элемента И субблока подсчета приращений, а прямой выход триггера через инвертор заведен на третий вход трехвходового элемента И субблока выбора степени сглаживания, в котором на младший (первый) разряд регистра сдвига заведен высокий уровень логической «1», шина сдвига регистра, счетный вход счетчика, первый вход двухвходового элемента И и второй вход трехвходового элемента И подключены к выходу элемента И узла тактирования, шина установки в «0» счетчика и шина записи «1» в регистр сдвига соединены с тактирующим входом устройства, выход счетчика через блок инверторов заведен на вход регистра адреса блока сглаживания, а выход 4-го разряда счетчика - на второй вход двухвходового элемента И, выход которого соединен с шиной сброса в «0» регистра адреса блока сглаживания и со вторым входом элемента ИЛИ узла тактирования, шина записи в регистре адреса блока сглаживания подключена к первому входу элемента ИЛИ узла тактирования и к выходу трехвходового элемента И субблока выбора степени сглаживания, выход регистра сдвига которого подсоединен к первому (А) информационному входу компаратора с монтажным сдвигом на один разряд вправо (в сторону младших разрядов), второй (В) информационный вход компаратора, монтажно сдвинутый на (М) разрядов вправо (в сторону младших разрядов), подключен к выходу субблока расчета скорости МП, а управляющий выход соотношения (А>В) компаратора соединен с первым входом первого трехвходового элемента И субблока.