Микропроцессор

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники и может быть использовано при разработке и построении конвейерных микропроцессоров с внеочередным исполнением команд. Техническим результатом является повышение скорости вычислений микропроцессора. Технический результат достигается за счет микропроцессора, который содержит блок подкачки кода, блок предсказания перехода, устройство управления, блок памяти контрольных точек, стек адресов возврата, буфер переупорядочивания команд и устройство внеочередного исполнения инструкций, который содержит станцию резервирования, устройство чтения-записи операндов и устройство передач управления. 2 ил.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано при разработке и построении конвейерных микропроцессоров с внеочередным исполнением команд.

Известен микропроцессор, содержащий взаимосвязанные между собой и входящие в состав большой интегральной схемы узлы обработки информации, управления, синхронизации, локальной памяти, регистры, дешифраторы микрокоманд, входные и выходные шины и источник питания, отличающийся тем, что узел управления микропроцессора снабжен приспособлением поиска неисправностей, которое выполнено в виде стабилизатора и попарно установленных с противоположных сторон последнего параллельно смонтированных разновеликих конденсаторов, причем одна пара конденсаторов выполнена с заземлением, другая имеет диагонально соединенные между конденсаторами сопротивление и диод.

Недостатком этого микропроцессора являются относительно узкие функциональные возможности.

Наиболее близким к заявляемому является «Конвейерный процессор» [РФ №2032215 C1, G06F 15/15, 27.01.1992], содержащий первый и второй коммутаторы, выходы которых соединены с входами памяти, выход которой соединен с входом третьего коммутатора, формирователь управляющих сигналов, выход которого соединен с входом арифметико-логического блока, отличающийся тем, что в него введены первый и второй формирователи потоков команд, четвертый и пятый коммутаторы и блок обмена, причем выходы четвертого коммутатора соединены с входами арифметико-логического блока, выход которого соединен с входом пятого коммутатора, выходы которого соединены с входами первого и четвертого коммутаторов и первого и второго формирователей потоков команд, выходы которых соединены с входами первого, второго и пятого коммутаторов и формирователя управляющих сигналов, выходы которого соединены с входами второго, четвертого и пятого коммутаторов и блока обмена, выходы которого соединены с входами первого коммутатора и второго коммутатора, выход которого соединен с входом третьего коммутатора, выходы которого соединены с входами блока обмена, четвертого коммутатора и первого и второго формирователей потоков команд.

Недостатком этого процессора является его низкая скорость вычислений.

Техническим результатом является повышение скорости вычислений за счет осуществления возможности внеочередного исполнения команд.

Технический результат достигается тем, что в микропроцессор, содержащий арифметико-логический блок, дополнительно введены блок 1 подкачки кода, блок предсказания перехода 2, устройство управления 3, блок памяти контрольных точек 4, стек адресов возврата 5, буфер переупорядочивания команд 6 и устройство внеочередного исполнения 7 инструкций, первый выход которого соединен с объединенными вторыми входами блока памяти контрольных точек 4, стека адресов возврата 5 и входом блока 2 предсказания перехода, выход которого соединен с входом блока 1 подкачки кода, выход которого соединен с четвертым входом устройства управления 3, первый выход которого соединен с объединенными первыми входами буфера переупорядочивания команд 6 и устройства внеочередного исполнения 7 инструкций, второй, третий и четвертый выходы последнего соединены каждый отдельно с одноименными входами буфера переупорядочивания команд 6, выход которого соединен с третьим входом устройства управления 3, первый вход которого соединен с первым выходом стека адресов возврата 5, первый вход которого соединен с вторым выходом устройства управления 3, второй вход которого соединен с первым выходом блока памяти контрольных точек 4, первый вход которого соединен с третьим выходом устройства управления 3, первый вход блока памяти контрольных точек 4 соединен со вторым выходом стека адресов возврата 5, третий вход которого соединен со вторым выходом блока памяти контрольных точек 4, причем устройство внеочередного исполнения 7 инструкций содержит станцию резервирования 8, арифметико-логический блок, устройство чтения-записи 10 операндов и устройство передач управления 11, выход которого соединен с объединенными первым и четвертым выходами устройства внеочередного исполнения 7 инструкций, первый вход которого соединен с первым входом станции резервирования 8, первый выход которой соединен с входом арифметико-логического блока 9, выход которого соединен с объединенными вторыми выходами устройства внеочередного исполнения 7 инструкций и станции резервирования 8, третий вход которой соединен с третьим выходом устройства внеочередного исполнения 7 инструкций и выходом устройство чтения-записи 10 операндов, вход которого соединен со вторым выходом станции резервирования 8, третий выход которой соединен с входом устройства передач управления 11.

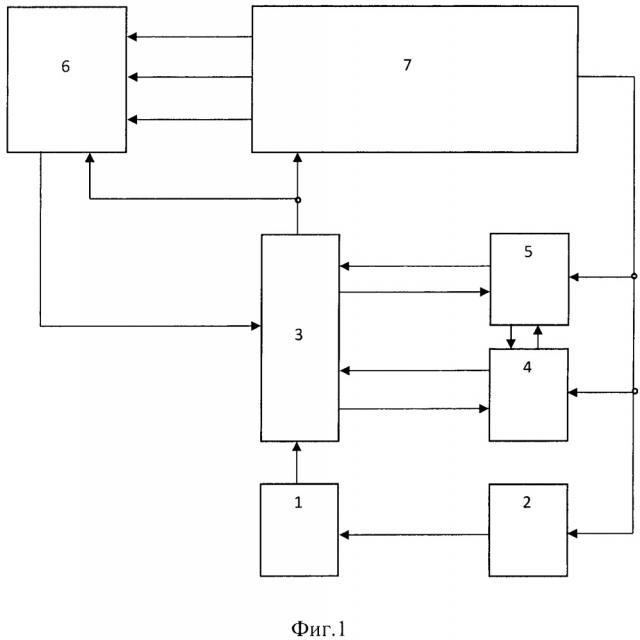

На фиг. 1 представлена схема микропроцессора.

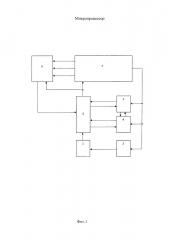

На фиг. 2 представлена схема блока внеочередного исполнения инструкций.

Микропроцессор (фиг. 1) содержит блок 1 подкачки кода, блок 2 предсказания перехода, устройство управления 3, блок 4 памяти контрольных точек, стек адресов возврата 5, буфер переупорядочивания команд 6 и устройство внеочередного исполнения 7 инструкций.

Устройство внеочередного исполнения 7 инструкций (фиг. 2) содержит станцию резервирования 8, арифметико-логический блок 9, устройство чтения-записи 10 операндов и устройство передач управления 11.

Микропроцессор (фиг. 1, 2) содержит блок 1 подкачки кода, блок предсказания перехода 2, устройство управления 3, блок памяти контрольных точек 4, стек адресов возврата 5, буфер переупорядочивания команд 6 и устройство внеочередного исполнения 7 инструкций, первый выход которого соединен с объединенными вторыми входами блока памяти контрольных точек 4, стека адресов возврата 5 и входом блока 2 предсказания перехода, выход которого соединен с входом блока 1 подкачки кода, выход которого соединен с четвертым входом устройства управления 3, первый выход которого соединен с объединенными первыми входами буфера переупорядочивания команд 6 и устройства внеочередного исполнения 7 инструкций, второй, третий и четвертый выходы последнего соединены каждый отдельно с одноименными входами буфера переупорядочивания команд 6, выход которого соединен с третьим входом устройства управления 3, первый вход которого соединен с первым выходом стека адресов возврата 5, первый вход которого соединен со вторым выходом устройства управления 3, второй вход которого соединен с первым выходом блока памяти контрольных точек 4, первый вход которого соединен с третьим выходом устройства управления 3, первый вход блока памяти контрольных точек 4 соединен со вторым выходом стека адресов возврата 5, третий вход которого соединен со вторым выходом блока памяти контрольных точек 4, причем устройство внеочередного исполнения 7 инструкций содержит станцию резервирования 8, устройство чтения-записи 10 операндов и устройство передач управления 11, выход которого соединен с объединенными первым и четвертым выходами устройства внеочередного исполнения 7 инструкций, первый вход которого соединен с первым входом станции резервирования 8, первый выход которой соединен с входом арифметико-логического блока 9, выход которого соединен с объединенными вторыми выходами устройства внеочередного исполнения 7 инструкций и станции резервирования 8, третий вход которой соединен с третьим выходом устройства внеочередного исполнения 7 инструкций и выходом устройство чтения-записи 10 операндов, вход которого соединен со вторым выходом станции резервирования 8, третий выход которой соединен с входом устройства передач управления 11.

Работа микропроцессора (фиг. 1) заключается в следующем.

В современных высокопроизводительных микропроцессорах используется несколько общепринятых техник для увеличения скорости вычислений. В частности, они включают

- конвейерное исполнение команд;

- предсказание направления передачи управления и условное исполнение предсказанной ветви.

Для ускорения выполнения команд выхода из процедур в высокопроизводительных микропроцессорах используется стек адресов возврата (RAS, Return Address Stack). С архитектурной точки зрения RAS представляет LIFO-память, в которую заносятся адреса, поставляемые командами вызова процедур и используемые (извлекаемые из LIFO) командами возврата из процедуры. При переполнении RAS'a самые старые локации переиспользуются. На верхнюю (последнюю значимую) локацию LIFO указывает регистр ras_top. При исполнении команды входа в процедуру он инкрементируется, при исполнении команды возврата из процедуры - декрементируется.

Указанные выше техники, однако, могут приводить к искажению информации в RAS'e. Так, например, наличие в условно исполняемой ветви впоследствии отмененной инструкции входа в процедуру приведет к занесению адреса в RAS, который не будет соответствовать архитектурному состоянию. Аналогично наличие в коде отмененной инструкции возврата из процедуры приведет к ложному использованию данных из локации и опять-таки коррупции состояния RAS'a.

Для борьбы с такого рода коррупцией предложено несколько методов. Как правило, предлагается хранить данные заносимые в RAS/используемые из RAS'a в отдельном буфере и модифицировать/восстанавливать состояние RAS только при изменении архитектурного состояния. Эти действия требуют дополнительного времени на изменение состояния при возникновении нештатных ситуаций, как например, в [US №6898699 A1, G06F 0/00, опубл. 26.06.2003].

В заявляемом микропроцессоре обеспечивается непрерывная поддержка корректного состояния RAS без использования дополнительных буферов.

Работа микропроцессора заключается в следующем.

Устройство подкачки инструкций 1 на основе информации из устройства предсказания переходов 2 подкачивает поток инструкций в устройство управления 3, где они декодируются и передаются в устройство внеочередного исполнения команд 7. Текущий статус операндов определяется на основе информации из буфера переупорядочивания команд 6. В станциях резервирования 8 команда дожидается готовности операндов и при их наличии передается в соответствующее исполнительное устройство: арифметико-логический блок 9, устройство чтения-записи 10 операндов и устройство передач управления 11. Команды при этом могут выдаваться на исполнение не в программном порядке. Результаты выполнения команд или информация об их завершении передаются в буфер переупорядочивания команд 6, где они завершаются, т.е. изменяют архитектурное состояние ядра и удаляются из конвейера, в программном порядке.

Устройство передач управления 11 определяет реальное направление ветвления и передает результат в устройство предсказания переходов 2 для коррекции предсказания, а также в блок памяти контрольных точек 4 для сохранения состояния при дешифрации переходов, для восстановления состояния необходимых регистров микропроцессора при неверном предсказании направления ветвления и в стек адресов возврата RAS.

В микропроцессоре инструкции передачи управления могут определять реальное направление передачи управления не по порядку, а отмена инструкций в неверно предсказанном потоке команд может осуществляться за один такт работы микропроцессора.

Таким образом, в микропроцессоре повышается скорость вычислений за счет осуществления возможности внеочередного исполнения команд.

Микропроцессор, содержащий арифметико-логический блок, отличающийся тем, что в него дополнительно введены блок подкачки кода, блок предсказания перехода, устройство управления, блок памяти контрольных точек, стек адресов возврата, буфер переупорядочивания команд и устройство внеочередного исполнения инструкций, первый выход которого соединен с объединенными вторыми входами блока памяти контрольных точек, стека адресов возврата и входом блока предсказания перехода, выход которого соединен с входом блока подкачки кода, выход которого соединен с четвертым входом устройства управления, первый выход которого соединен с объединенными первыми входами буфера переупорядочивания команд и устройства внеочередного исполнения инструкций, второй, третий и четвертый выходы последнего соединены каждый отдельно с одноименными входами буфера переупорядочивания команд, выход которого соединен с третьим входом устройства управления, первый вход которого соединен с первым выходом стека адресов возврата, первый вход которого соединен со вторым выходом устройства управления, второй вход которого соединен с первым выходом блока памяти контрольных точек, первый вход которого соединен с третьим выходом устройства управления, первый вход блока памяти контрольных точек соединен со вторым выходом стека адресов возврата, третий вход которого соединен со вторым выходом блока памяти контрольных точек, причем устройство внеочередного исполнения инструкций содержит станцию резервирования, арифметико-логический блок, устройство чтения-записи операндов и устройство передач управления, выход которого соединен с объединенными первым и четвертым выходами устройства внеочередного исполнения инструкций, первый вход которого соединен с первым входом станции резервирования, первый выход которой соединен с входом арифметико-логического блока, выход которого соединен с объединенными вторыми выходами устройства внеочередного исполнения инструкций и станции резервирования, третий вход которой соединен с третьим выходом устройства внеочередного исполнения инструкций и выходом устройство чтения-записи операндов, вход которого соединен со вторым выходом станции резервирования, третий выход которой соединен с входом устройства передач управления.