Устройство обнаружения нелинейных кодовых последовательностей

Иллюстрации

Показать всеИзобретение относится к области радиотехники и может быть использовано в системах связи для обнаружения сложных шумоподобных сигналов. Технический результат заключается в повышении точности обнаружения нелинейных последовательностей и автоматическом определении длины формирующих нелинейных последовательностей регистров. Устройство обнаружения нелинейных кодовых последовательностей состоит из генератора тактовых импульсов, подстраиваемого буферного регистра сдвига, логического элемента ИЛИ-НЕ с подстраиваемым количеством входов, коммутатора входов, блока управления коммутаторов входов, двух блоков коммутации, блока управления, сумматора по модулю 2, блока элементов И, выходного сдвигового регистра и решающего регистра сдвига. Вход коммутатора входов соединен с выходами подстраиваемого буферного регистра сдвига и блока управления коммутаторов входов, выход коммутатора входов соединен с входом логического элемента ИЛИ-НЕ с подстраиваемым количеством входов, а вход блока управления коммутаторов входов соединен с выходом логического элемента ИЛИ-НЕ с подстраиваемым количеством входов. 1 ил.

Реферат

Изобретение относится к области радиотехники и может быть использовано в системах связи для обнаружения сложных шумоподобных сигналов.

Известно своим схожим практическим использованием устройство обнаружения широкополосных сигналов [1], а также устройства обнаружения линейных последовательностей [2].

Недостатками данных устройств являются отсутствие возможности автоматической перестройки длины регистра вскрываемого генератора, а также неспособность вскрытия нелинейных последовательностей [2].

Наиболее близким по технической сущности является устройство для обнаружения нелинейных кодовых последовательностей [3].

Применение подобных устройств ограничивается отсутствием возможности обнаружения нелинейной последовательности, а также отсутствием возможности подстройки количества входов элемента ИЛИ-НЕ.

Задачей изобретения является создание устройства, которое позволяло бы обнаруживать нелинейные последовательности, вскрывать структуру их формирования, которое так же было бы способно автоматически определять длины формирующих нелинейные последовательности регистров.

Требуемый технический результат достигается тем, что устройство обнаружения нелинейных кодовых последовательностей содержит генератор тактовых импульсов, подстраиваемый буферный регистр сдвига, логический элемент ИЛИ-НЕ с подстраиваемым количеством входов, коммутатор входов, блок управления коммутаторов входов, два блока коммутации, блок управления, сумматор по модулю 2, блок элементов И, выходной сдвиговый регистр и решающий регистр сдвига, причем вход коммутатора входов соединен с выходами подстраиваемого буферного регистра сдвига и блока управления коммутаторов входов, выход коммутатора входов соединен с входом логического элемента ИЛИ-НЕ с подстраиваемым количеством входов, а вход блока управления коммутаторов входов соединен с выходом логического элемента ИЛИ-НЕ с подстраиваемым количеством входов.

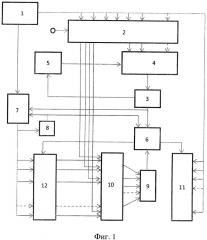

Сущность изобретения поясняется чертежом, где на фиг. 1 представлен возможный вариант построения данного передатчика, который в себе содержит:

1 - генератор тактовых импульсов;

2 - подстраиваемый буферный регистра сдвига;

3 - логический элемент ИЛИ-НЕ с подстраиваемым количеством входов;

4 - коммутатор входов;

5 - блок управления коммутаторов входов;

6 - блок коммутации;

7 - блок коммутации;

8 - блок управления;

9 - сумматор по модулю 2;

10 - блок элементов И;

11 - выходной сдвиговый регистр;

12 - решающий регистр сдвига.

Устройство обнаружения нелинейных кодовых последовательностей работает следующим образом.

В исходном состоянии блоки коммутации (6 и 7) отключают свои выходы от входов, входы коммутатора входов (4) соединены со своими выходами, ячейки подстраиваемого буферного регистра сдвига (2), решающего регистра сдвига (12) и выходного сдвигового регистра (11) находятся в обнуленном состоянии, за исключением старшего разряда решающего регистра (12), который находится в состоянии логической единицы. Принимаемая последовательность записывается в подстраиваемый буферный регистр сдвига (2), затем с подстраиваемого буферного регистра сдвига (2) на логический элемент ИЛИ-НЕ с подстраиваемым количеством входов (3) поступают логические значения серии n последних ячеек, где обнаруживаются серии из n нулей. С данного момента предполагаемая нелинейная кодовая последовательность на протяжении n значений будет иметь линейный закон формирования, что позволяет на данном участке вскрывать структуру данной последовательности за счет решения системы линейных дискретных уравнений. При появлении серии из n нулей с логического элемента ИЛИ-НЕ с подстраиваемым количеством входов (3) импульс подключает выход блока коммутации (6) к входу решающего регистра сдвига (12), также на блок управления коммутаторов входов (5) подается сигнал управления, который запускает его функционирование, а выход блока коммутации (7) подключается к входу блока управления (8) и решающего регистра сдвига (12). В результате этого тактовые импульсы от генератора тактовых импульсов (1) начинают поступать на решающий регистр сдвига (12) и блок управления (8), который после каждых n импульсов подает на блоки коммутации (6 и 7) импульсы управления. Блок управления коммутаторов входов (5) подает сигнал на коммутатор входов (4), вход которого соединен с выходами подстраиваемого буферного регистра сдвига (2) и блока управления коммутаторов входов (5), выход коммутатора входов (4) соединен с входом логического элемента ИЛИ-НЕ с подстраиваемым количеством входов (3), а вход блока управления коммутаторов входов (5) соединен с выходом логический элемент ИЛИ-НЕ с подстраиваемым количеством входов (3), в результате подачи описанного выше сигнала прерывается связь выхода младшей ячейки подстраиваемого буферного регистра сдвига (2) с одним из входов логического элемента ИЛИ-НЕ с подстраиваемым количеством входов (3). При этом на данный вход данного элемента подается значение логического нуля. Затем замыкается цепь обратной связи решающего регистра сдвига (12), которая содержит блок элементов И (10) и сумматор по модулю 2 (9) и блок коммутации (6). После этого в цепи этих блоков начинается решение системы дискретных линейных уравнений. Решение производится путем n кратного продвижения символов подстраиваемого буферного регистра сдвига (2) и решающего регистра сдвига (12) при замкнутой цепи обратной связи последнего. После n продвижений выходной сдвиговый регистр (11) будет полностью заполнен значениями ai. На основании принятых символов представляется возможность составить структуру генератора нелинейных кодовых последовательностей. При этом ячейки, содержащие логические единицы, говорят о наличии выводов на обратные связи генератора нелинейных последовательностей.

Нелинейные последовательности могут использоваться для формирования маскирующей несущей радиоканала передачи данных. Таким образом, введение новых элементов и изменение алгоритмов функционирования позволяет осуществить определение коэффициентов полинома нелинейных последовательностей.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Гай-Бин Ю., Уорд Р.Б. Методы дешифрации последовательности максимальной длины, ТИИЭР, т. 65, №7, 1977 г.

2. Тузов Г.И., Сивов В.А., Прытков В.И. и др. Помехозащищенность систем со сложными сигналами, М., - Радиосвязь, с. 264, 1985 г.

3. Su 767990, 1980 г.

Устройство обнаружения нелинейных кодовых последовательностей, состоящее из генератора тактовых импульсов, подстраиваемого буферного регистра сдвига, логического элемента ИЛИ-НЕ с подстраиваемым количеством входов, двух блоков коммутации, блока управления, сумматора по модулю 2, блока элементов И, выходного сдвигового регистра, решающего регистра сдвига, отличающееся тем, что в него дополнительно введены коммутатор входов и блок управления коммутаторов входов, причем вход коммутатора входов соединен с выходами подстраиваемого буферного регистра сдвига и блока управления коммутаторов входов, выход коммутатора входов соединен с входом логического элемента ИЛИ-НЕ с подстраиваемым количеством входов, а вход блока управления коммутаторов входов соединен с выходом логического элемента ИЛИ-НЕ с подстраиваемым количеством входов.