Управляющая схема драйвера затвора в матрице, применяемая для дисплейного устройства с плоской панелью, и дисплейное устройство с плоской панелью

Иллюстрации

Показать всеИзобретение относится к области воспроизведения изображений. Технический результат заключается в повышении эффективности управления схемой драйвера затвора в матрице. Технический результат достигается за счет схемы входного каскада, содержащей множество управляющих подблоков GOA, соединенных каскадно; схемы промежуточного каскада, содержащей два управляющих подблока GOA, соединенных каскадно, причем входная клемма первого каскада управляющих подблоков GOA в схеме промежуточного каскада электрически соединена с выходной клеммой последнего каскада множества управляющих подблоков GOA в схеме входного каскада; схемы выходного каскада, содержащей множество управляющих подблоков GOA, соединенных каскадно, причем входная клемма первого каскада множества управляющих подблоков GOA в схеме выходного каскада электрически соединена с выходной клеммой последнего каскада управляющих подблоков GOA в схеме промежуточного каскада. 3 н. и 16 з.п. ф-лы, 8 ил.

Реферат

Область техники

[0001] Изобретение относится к области технологии воспроизведения изображений, а в частности, к управляющей схеме драйвера затвора в матрице, применяемой для дисплейного устройства с плоской панелью, и к дисплейному устройству с плоской панелью.

Описание соответствующей области техники

[0002] Драйвер затвора в матрице (GOA - gate driver on array, далее - драйвер затвора) имеет преимущества, заключающиеся в пониженной стоимости производства и узкой конструкции, драйвер затвора постепенно начинает применяться в области жидкокристаллических дисплеев (ЖКД). В то же время технология сенсорного управления, позволяющая организовать естественный интерфейс между электронной системой и пользователем, также широко используется в различных областях техники, особенно в сенсорной технологии встраивания в ячейку (in-cell), обладающей такими преимуществами, как малая толщина и высокая чувствительность сенсоров.

[0003] При объединении управляющей схемы драйвера затвора и технологии сенсорного управления для решения прикладных задач на известном уровне техники в общем случае, когда панель работает в нормальном режиме, в первую очередь выполняется сканирование, управляемое схемой драйвера затвора, а затем выполняется сканирование выходного сенсорного сигнала после того, как будет выполнено сканирование всех затворных шин, процесс сканирования, управляемый схемой драйвера затвора, не имеет прерываний, и поэтому частота сканирования, управляемого схемой драйвера затвора, и частота сканирования выходного сенсорного сигнала согласованы между собой, т.е. один период сканирования, управляемого с помощью схемы драйвера затвора, соответствует одному периоду сканирования выходного сенсорного сигнала, поэтому частота сенсорного сканирования ограничена.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0004] Основная техническая проблема, решаемая настоящим изобретением, состоит в том, чтобы предложить управляющую схему драйвера затвора в матрице, применяемую в дисплейном устройстве с плоской панелью, и дисплейное устройство с плоской панелью, чтобы в результате добиться прерывания сканирования посредством управляющей схемы драйвера затвора и за счет этого увеличить частоту сенсорного сканирования.

[0005] Техническое решение указанной технической проблемы, предложенное в настоящем изобретении, заключается в том, чтобы разработать управляющую схему драйвера затвора, применяемую для дисплейного устройства с плоской панелью. Управляющая схема драйвера затвора содержит:

схему входного каскада, содержащую множество управляющих подблоков драйвера затвора, соединенных каскадно;

схему промежуточного каскада, содержащую два управляющих подблока драйвера затвора, соединенных каскадно, причем входная клемма первого каскада управляющих подблоков драйвера затвора в схеме промежуточного каскада электрически соединена с выходной клеммой последнего каскада множества управляющих подблоков драйвера затвора в схеме входного каскада;

схему выходного каскада, содержащую множество управляющих подблоков драйвера затвора, соединенных каскадно, причем входная клемма первого каскада множества управляющих подблоков драйвера затвора в схеме выходного каскада электрически соединена с выходной клеммой последнего каскада управляющих подблоков драйвера затвора в схеме промежуточного каскада;

причем управляющие подблоки драйвера затвора в схеме входного каскада, схеме промежуточного каскада и схеме выходного каскада выполнены (т.е. структурированы и скомпонованы) с возможностью приема первого тактового сигнала и второго тактового сигнала для последовательного формирования соответствующих управляющих сигналов затвора, в первом тактовом сигнале и во втором тактовом сигнале задан период прерывания для формирования прерывания между последовательно генерируемыми управляющими сигналами затвора, а дисплейное устройство с плоской панелью выполнено с возможностью обнаружения касания в период прерывания; период прерывания больше длительности одного импульсного сигнала и меньше длительности одного видеокадра.

[0006] В одном варианте исполнения каждый каскад управляющих подблоков драйвера затвора в схеме входного каскада, схеме промежуточного каскада и схеме выходного каскада электрически соединен с соответствующей затворной шиной и предназначен для подачи одного из соответствующих последовательно генерируемых управляющих сигналов затвора на соответствующую затворную шину.

[0007] В одном варианте исполнения первый тактовый сигнал и второй тактовый сигнал каждый имеют первый период, период прерывания, период восстановления и второй период;

в первый период источник первого тактового сигнала и источник второго тактового сигнала соответственно выдают импульсные сигналы противоположной полярности, управляющие подблоки драйвера затвора в схеме входного каскада управляющей схемы драйвера затвора последовательно подают часть последовательно генерируемых управляющих сигналов затвора, чтобы соответствующим образом управлять частью затворных шин дисплейного устройства с плоской панелью;

в период прерывания первый тактовый сигнал поддерживается в соответствии с первой логической схемой, а второй тактовый сигнал поддерживается в соответствии со второй логической схемой, полярность первой логической схемы и полярность второй логической схемы противоположные; и в период прерывания схема промежуточного каскада и схема выходного каскада управляющей схемы драйвера затвора прекращают выдавать управляющий сигнал затвора;

в период восстановления первый тактовый сигнал поддерживается в соответствии со второй логической схемой, источник второго тактового сигнала выдает один второй логический сигнал и один первый логический сигнал, а схема промежуточного каскада управляющей схемы драйвера затвора восстанавливает подачу следующих двух управляющих сигналов затвора;

во второй период источник первого тактового сигнала и источник второго тактового сигнала соответственно выдают импульсные сигналы противоположной полярности, схема выходного каскада управляющей схемы драйвера затвора выдает остальные последовательно генерируемые управляющие сигналы затвора.

[0008] В одном варианте исполнения первая логическая схема имеет низкий логический уровень, а вторая логическая схема имеет высокий логический уровень.

[0009] В одном варианте исполнения период прерывания настраивают в соответствии с фактической потребностью.

[0010] В одном варианте исполнения схема входного каскада, схема промежуточного каскада и схема выходного каскада каждая содержит нечетный управляющий каскадный подблок драйвера затвора и четный управляющий каскадный подблок драйвера затвора.

[0011] В одном варианте исполнения нечетный управляющий каскадный подблок драйвера затвора и четный управляющий каскадный подблок драйвера затвора в схеме входного каскада каждый содержит:

первый инвертор, имеющий входную клемму, первую клемму тактового управления, вторую клемму тактового управления и выходную клемму, при этом входная клемма первого инвертора электрически соединена с выходной клеммой предыдущего управляющего каскадного подблока драйвера затвора;

второй инвертор, при этом входная клемма второго инвертора электрически соединена с выходной клеммой первого инвертора;

первый вентиль ИЛИ-НЕ и второй вентиль ИЛИ-НЕ, при этом первая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго инвертора, вторая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ, выходная клемма первого вентиля ИЛИ-НЕ электрически соединена с первой входной клеммой второго вентиля ИЛИ-НЕ, а вторая входная клемма второго вентиля ИЛИ-НЕ электрически соединена с входной клеммой второго инвертора;

вентиль И-НЕ, при этом первая входная клемма вентиля И-НЕ электрически соединена с источником первого тактового сигнала или источником второго тактового сигнала, а вторая входная клемма вентиля И-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ;

третий инвертор, при этом входная клемма третьего инвертора электрически соединена с выходной клеммой вентиля И-НЕ;

четвертый инвертор, при этом входная клемма четвертого инвертора электрически соединена с выходной клеммой третьего инвертора, а выходную клемму четвертого инвертора используют в качестве выходной клеммы данного управляющего каскадного подблока драйвера затвора для вывода одного из соответствующих последовательно генерируемых управляющих сигналов затвора;

причем в нечетном управляющем каскадном подблоке драйвера затвора схемы входного каскада первая клемма тактового управления первого инвертора электрически соединена с источником первого тактового сигнала, вторая клемма тактового управления первого инвертора электрически соединена с источником второго тактового сигнала, и первая входная клемма вентиля И-НЕ электрически соединена с источником первого тактового сигнала;

причем в четном управляющем каскадном подблоке драйвера затвора схемы входного каскада первая клемма тактового управления первого инвертора электрически соединена с источником второго тактового сигнала, вторая клемма тактового управления первого инвертора электрически соединена с источником первого тактового сигнала, и первая входная клемма вентиля И-НЕ электрически соединена с источником второго тактового сигнала.

[0012] В одном варианте исполнения нечетный управляющий каскадный подблок драйвера затвора в схеме промежуточного каскада содержит:

первый инвертор, имеющий входную клемму, первую клемму тактового управления, вторую клемму тактового управления и выходную клемму, при этом входная клемма первого инвертора электрически соединена с выходной клеммой последнего управляющего каскадного подблока драйвера затвора в схеме входного каскада;

второй инвертор, при этом входная клемма второго инвертора электрически соединена с выходной клеммой первого инвертора;

первый вентиль ИЛИ-НЕ и второй вентиль ИЛИ-НЕ, при этом первая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго инвертора, вторая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ, выходная клемма первого вентиля ИЛИ-НЕ электрически соединена с первой входной клеммой второго вентиля ИЛИ-НЕ, а вторая входная клемма второго вентиля ИЛИ-НЕ электрически соединена с входной клеммой второго инвертора;

тристабильный вентиль И-НЕ, имеющий первую входную клемму, вторую входную клемму, третью входную клемму и выходную клемму, при этом первая входная клемма тристабильного вентиля И-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ;

третий инвертор, при этом входная клемма третьего инвертора электрически соединена с выходной клеммой тристабильного вентиля И-НЕ;

четвертый инвертор, при этом входная клемма четвертого инвертора электрически соединена с выходной клеммой третьего инвертора, а выходную клемму четвертого инвертора используют в качестве выходной клеммы данного управляющего каскадного подблока драйвера затвора для вывода одного из соответствующих последовательно генерируемых управляющих сигналов затвора;

причем в нечетном управляющем каскадном подблоке драйвера затвора схемы промежуточного каскада первая клемма тактового управления первого инвертора и вторая входная клемма тристабильного вентиля И-НЕ электрически соединены с источником первого тактового сигнала, вторая клемма тактового управления первого инвертора и третья входная клемма тристабильного вентиля И-НЕ электрически соединены с источником второго тактового сигнала;

четный управляющий каскадный подблок драйвера затвора в схеме промежуточного каскада содержит:

первый инвертор, имеющий входную клемму, первую клемму тактового управления, вторую клемму тактового управления и выходную клемму, при этом входная клемма первого инвертора электрически соединена с выходной клеммой предыдущего управляющего каскадного подблока драйвера затвора;

второй инвертор, при этом входная клемма второго инвертора электрически соединена с выходной клеммой первого инвертора;

первый вентиль ИЛИ-НЕ и второй вентиль ИЛИ-НЕ, при этом первая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго инвертора, вторая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ, выходная клемма первого вентиля ИЛИ-НЕ электрически соединена с первой входной клеммой второго вентиля ИЛИ-НЕ, а вторая входная клемма второго вентиля ИЛИ-НЕ электрически соединена с входной клеммой второго инвертора;

третий инвертор, при этом входная клемма третьего инвертора электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ;

четвертый инвертор, имеющий первую входную клемму, вторую входную клемму и выходную клемму, при этом первая входная клемма четвертого инвертора электрически соединена с выходной клеммой третьего инвертора;

пятый инвертор, при этом входная клемма пятого инвертора электрически соединена с выходной клеммой четвертого инвертора, а выходную клемму пятого инвертора используют в качестве выходной клеммы данного управляющего каскадного подблока драйвера затвора для вывода одного из соответствующих последовательно генерируемых управляющих сигналов затвора;

причем в четном управляющем каскадном подблоке драйвера затвора схемы промежуточного каскада первая клемма тактового управления первого инвертора и вторая входная клемма четвертого инвертора электрически соединены с источником второго тактового сигнала, вторая клемма тактового управления первого инвертора электрически соединена с источником первого тактового сигнала;

[0013] В одном варианте исполнения нечетный управляющий каскадный подблок драйвера затвора и четный управляющий каскадный подблок драйвера затвора в схеме выходного каскада каждый содержит:

первый инвертор, имеющий входную клемму, первую клемму тактового управления, вторую клемму тактового управления и выходную клемму, при этом входная клемма первого инвертора электрически соединена с выходной клеммой последнего управляющего каскадного подблока драйвера затвора в схеме входного каскада;

второй инвертор, при этом входная клемма второго инвертора электрически соединена с выходной клеммой первого инвертора;

первый вентиль ИЛИ-НЕ и второй вентиль ИЛИ-НЕ, при этом первая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго инвертора, вторая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ, выходная клемма первого вентиля ИЛИ-НЕ электрически соединена с первой входной клеммой второго вентиля ИЛИ-НЕ, а вторая входная клемма второго вентиля ИЛИ-НЕ электрически соединена с входной клеммой второго инвертора;

вентиль И-НЕ, при этом первая входная клемма вентиля И-НЕ электрически соединена с источником первого тактового сигнала или источником второго тактового сигнала, а вторая входная клемма вентиля И-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ;

третий инвертор, при этом входная клемма третьего инвертора электрически соединена с выходной клеммой вентиля И-НЕ;

четвертый инвертор, при этом входная клемма четвертого инвертора электрически соединена с выходной клеммой третьего инвертора, а выходную клемму четвертого инвертора используют в качестве выходной клеммы данного управляющего каскадного подблока драйвера затвора для вывода одного из соответствующих последовательно генерируемых управляющих сигналов затвора;

причем в нечетном управляющем каскадном подблоке драйвера затвора схемы выходного каскада первая клемма тактового управления первого инвертора электрически соединена с источником первого тактового сигнала, вторая клемма тактового управления первого инвертора электрически соединена с источником второго тактового сигнала, и первая входная клемма вентиля И-НЕ электрически соединена с источником первого тактового сигнала;

причем в четном управляющем каскадном подблоке драйвера затвора схемы выходного каскада первая клемма тактового управления первого инвертора электрически соединена с источником второго тактового сигнала, вторая клемма тактового управления первого инвертора электрически соединена с источником первого тактового сигнала, и первая входная клемма вентиля И-НЕ электрически соединена с источником второго тактового сигнала.

[0014] В настоящем изобретении предложено другое техническое решение указанной технической проблемы, заключающееся в том, чтобы разработать управляющую схему драйвера затвора, применяемую для дисплейного устройства с плоской панелью. Управляющая схема драйвера затвора содержит:

схему входного каскада, содержащую множество управляющих подблоков драйвера затвора, соединенных каскадно;

схему промежуточного каскада, содержащую два управляющих подблока драйвера затвора, соединенных каскадно, причем входная клемма первого каскада управляющих подблоков драйвера затвора в схеме промежуточного каскада электрически соединена с выходной клеммой последнего каскада множества управляющих подблоков драйвера затвора в схеме входного каскада;

схему выходного каскада, содержащую множество управляющих подблоков драйвера затвора, соединенных каскадно, причем входная клемма первого каскада множества управляющих подблоков драйвера затвора в схеме выходного каскада электрически соединена с выходной клеммой последнего каскада управляющих подблоков драйвера затвора в схеме промежуточного каскада;

причем управляющие подблоки драйвера затвора в схеме входного каскада, схеме промежуточного каскада и схеме выходного каскада выполнены с возможностью приема первого тактового сигнала и второго тактового сигнала для последовательного формирования соответствующих управляющих сигналов затвора, при этом в первом тактовом сигнале и во втором тактовом сигнале задан период прерывания для формирования прерывания между последовательно генерируемыми управляющими сигналами затвора, а дисплейное устройство с плоской панелью предусматривает возможность выполнения операции обнаружения касания в период прерывания.

[0015] В одном варианте исполнения каждый каскад управляющих подблоков драйвера затвора в схеме входного каскада, схеме промежуточного каскада и схеме выходного каскада электрически соединен с соответствующей затворной шиной и предназначен для подачи одного из соответствующих последовательно генерируемых управляющих сигналов затвора на соответствующую затворную шину.

[0016] В одном варианте исполнения первый тактовый сигнал и второй тактовый сигнал каждый имеют первый период, период прерывания, период восстановления и второй период;

в первый период источник первого тактового сигнала и источник второго тактового сигнала соответственно выдают импульсные сигналы противоположной полярности, управляющие подблоки драйвера затвора в схеме входного каскада управляющей схемы драйвера затвора последовательно подают часть последовательно генерируемых управляющих сигналов затвора, чтобы соответствующим образом управлять частью затворных шин дисплейного устройства с плоской панелью;

в период прерывания первый тактовый сигнал поддерживается в соответствии с первой логической схемой, а второй тактовый сигнал поддерживается в соответствии со второй логической схемой, полярность первой логической схемы и полярность второй логической схемы противоположные; и в период прерывания схема промежуточного каскада и схема выходного каскада управляющей схемы драйвера затвора прекращают выдавать управляющий сигнал затвора;

в период восстановления первый тактовый сигнал поддерживается в соответствии со второй логической схемой, источник второго тактового сигнала выдает один второй логический сигнал и один первый логический сигнал, а схема промежуточного каскада управляющей схемы драйвера затвора восстанавливает подачу следующих двух управляющих сигналов затвора;

во второй период источник первого тактового сигнала и источник второго тактового сигнала соответственно выдают импульсные сигналы противоположной полярности, схема выходного каскада управляющей схемы драйвера затвора подает остальные последовательно генерируемые управляющие сигналы затвора.

[0017] В одном варианте исполнения первая логическая схема имеет низкий логический уровень, а вторая логическая схема имеет высокий логический уровень.

[0018] В одном варианте исполнения период прерывания настраивают в соответствии с фактической потребностью.

[0019] В одном варианте исполнения схема входного каскада, схема промежуточного каскада и схема выходного каскада каждая содержит нечетный управляющий каскадный подблок драйвера затвора и четный управляющий каскадный подблок драйвера затвора.

[0020] В одном варианте исполнения нечетный управляющий каскадный подблок драйвера затвора и четный управляющий каскадный подблок драйвера затвора в схеме входного каскада каждый содержит:

первый инвертор, имеющий входную клемму, первую клемму тактового управления, вторую клемму тактового управления и выходную клемму, при этом входная клемма первого инвертора электрически соединена с выходной клеммой предыдущего управляющего каскадного подблока драйвера затвора;

второй инвертор, при этом входная клемма второго инвертора электрически соединена с выходной клеммой первого инвертора;

первый вентиль ИЛИ-НЕ и второй вентиль ИЛИ-НЕ, при этом первая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго инвертора, вторая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ, выходная клемма первого вентиля ИЛИ-НЕ электрически соединена с первой входной клеммой второго вентиля ИЛИ-НЕ, а вторая входная клемма второго вентиля ИЛИ-НЕ электрически соединена с входной клеммой второго инвертора;

вентиль И-НЕ, при этом первая входная клемма вентиля И-НЕ электрически соединена с источником первого тактового сигнала или источником второго тактового сигнала, а вторая входная клемма вентиля И-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ;

третий инвертор, при этом входная клемма третьего инвертора электрически соединена с выходной клеммой вентиля И-НЕ;

четвертый инвертор, при этом входная клемма четвертого инвертора электрически соединена с выходной клеммой третьего инвертора, а выходную клемму четвертого инвертора используют в качестве выходной клеммы данного управляющего каскадного подблока драйвера затвора для вывода одного из соответствующих последовательно генерируемых управляющих сигналов затвора;

причем в нечетном управляющем каскадном подблоке драйвера затвора схемы входного каскада первая клемма тактового управления первого инвертора электрически соединена с источником первого тактового сигнала, вторая клемма тактового управления первого инвертора электрически соединена с источником второго тактового сигнала, и первая входная клемма вентиля И-НЕ электрически соединена с источником первого тактового сигнала;

причем в четном управляющем каскадном подблоке драйвера затвора схемы входного каскада первая клемма тактового управления первого инвертора электрически соединена с источником второго тактового сигнала, вторая клемма тактового управления первого инвертора электрически соединена с источником первого тактового сигнала, и первая входная клемма вентиля И-НЕ электрически соединена с источником второго тактового сигнала.

[0021] В одном варианте исполнения нечетный управляющий каскадный подблок драйвера затвора в схеме промежуточного каскада содержит:

первый инвертор, имеющий входную клемму, первую клемму тактового управления, вторую клемму тактового управления и выходную клемму, при этом входная клемма первого инвертора электрически соединена с выходной клеммой последнего управляющего каскадного подблока драйвера затвора в схеме входного каскада;

второй инвертор, при этом входная клемма второго инвертора электрически соединена с выходной клеммой первого инвертора;

первый вентиль ИЛИ-НЕ и второй вентиль ИЛИ-НЕ, при этом первая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго инвертора, вторая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ, выходная клемма первого вентиля ИЛИ-НЕ электрически соединена с первой входной клеммой второго вентиля ИЛИ-НЕ, а вторая входная клемма второго вентиля ИЛИ-НЕ электрически соединена с входной клеммой второго инвертора;

тристабильный вентиль И-НЕ, имеющий первую входную клемму, вторую входную клемму, третью входную клемму и выходную клемму, при этом первая входная клемма тристабильного вентиля И-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ;

третий инвертор, при этом входная клемма третьего инвертора электрически соединена с выходной клеммой тристабильного вентиля И-НЕ;

четвертый инвертор, при этом входная клемма четвертого инвертора электрически соединена с выходной клеммой третьего инвертора, а выходную клемму четвертого инвертора используют в качестве выходной клеммы данного управляющего каскадного подблока драйвера затвора для вывода одного из соответствующих последовательно генерируемых управляющих сигналов затвора;

причем в нечетном управляющем каскадном подблоке драйвера затвора схемы промежуточного каскада первая клемма тактового управления первого инвертора и вторая входная клемма тристабильного вентиля И-НЕ электрически соединены с источником первого тактового сигнала, вторая клемма тактового управления первого инвертора и третья входная клемма тристабильного вентиля И-НЕ электрически соединены с источником второго тактового сигнала;

четный управляющий каскадный подблок драйвера затвора в схеме промежуточного каскада содержит:

первый инвертор, имеющий входную клемму, первую клемму тактового управления, вторую клемму тактового управления и выходную клемму, при этом входная клемма первого инвертора электрически соединена с выходной клеммой предыдущего управляющего каскадного подблока драйвера затвора;

второй инвертор, при этом входная клемма второго инвертора электрически соединена с выходной клеммой первого инвертора;

первый вентиль ИЛИ-НЕ и второй вентиль ИЛИ-НЕ, при этом первая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго инвертора, вторая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ, выходная клемма первого вентиля ИЛИ-НЕ электрически соединена с первой входной клеммой второго вентиля ИЛИ-НЕ, а вторая входная клемма второго вентиля ИЛИ-НЕ электрически соединена с входной клеммой второго инвертора;

третий инвертор, при этом входная клемма третьего инвертора электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ;

четвертый инвертор, имеющий первую входную клемму, вторую входную клемму и выходную клемму, при этом первая входная клемма четвертого инвертора электрически соединена с выходной клеммой третьего инвертора;

пятый инвертор, при этом входная клемма пятого инвертора электрически соединена с выходной клеммой четвертого инвертора, а выходную клемму пятого инвертора используют в качестве выходной клеммы данного управляющего каскадного подблока драйвера затвора для вывода одного из соответствующих последовательно генерируемых управляющих сигналов затвора;

причем в четном управляющем каскадном подблоке драйвера затвора схемы промежуточного каскада первая клемма тактового управления первого инвертора и вторая входная клемма четвертого инвертора электрически соединены с источником второго тактового сигнала, вторая клемма тактового управления первого инвертора электрически соединена с источником первого тактового сигнала;

[0022] В одном варианте исполнения нечетный управляющий каскадный подблок драйвера затвора и четный управляющий каскадный подблок драйвера затвора в схеме выходного каскада каждый содержит:

первый инвертор, имеющий входную клемму, первую клемму тактового управления, вторую клемму тактового управления и выходную клемму, при этом входная клемма первого инвертора электрически соединена с выходной клеммой последнего управляющего каскадного подблока драйвера затвора в схеме входного каскада;

второй инвертор, при этом входная клемма второго инвертора электрически соединена с выходной клеммой первого инвертора;

первый вентиль ИЛИ-НЕ и второй вентиль ИЛИ-НЕ, при этом первая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго инвертора, вторая входная клемма первого вентиля ИЛИ-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ, выходная клемма первого вентиля ИЛИ-НЕ электрически соединена с первой входной клеммой второго вентиля ИЛИ-НЕ, а вторая входная клемма второго вентиля ИЛИ-НЕ электрически соединена с входной клеммой второго инвертора;

вентиль И-НЕ, при этом первая входная клемма вентиля И-НЕ электрически соединена с источником первого тактового сигнала или источником второго тактового сигнала, а вторая входная клемма вентиля И-НЕ электрически соединена с выходной клеммой второго вентиля ИЛИ-НЕ;

третий инвертор, при этом входная клемма третьего инвертора электрически соединена с выходной клеммой вентиля И-НЕ;

четвертый инвертор, при этом входная клемма четвертого инвертора электрически соединена с выходной клеммой третьего инвертора, а выходную клемму четвертого инвертора используют в качестве выходной клеммы данного управляющего каскадного подблока драйвера затвора для вывода одного из соответствующих последовательно генерируемых управляющих сигналов затвора;

причем в нечетном управляющем каскадном подблоке драйвера затвора схемы выходного каскада первая клемма тактового управления первого инвертора электрически соединена с источником первого тактового сигнала, вторая клемма тактового управления первого инвертора электрически соединена с источником второго тактового сигнала, и первая входная клемма вентиля И-НЕ электрически соединена с источником первого тактового сигнала;

причем в четном управляющем каскадном подблоке драйвера затвора схемы выходного каскада первая клемма тактового управления первого инвертора электрически соединена с источником второго тактового сигнала, вторая клемма тактового управления первого инвертора электрически соединена с источником первого тактового сигнала, и первая входная клемма вентиля И-НЕ электрически соединена с источником второго тактового сигнала.

[0023] В настоящем изобретении предложено еще одно техническое решение указанной технической проблемы, заключающееся в том, чтобы разработать дисплейное устройство с плоской панелью. Дисплейное устройство с плоской панелью содержит управляющую схему драйвера затвора в матрице, описанную в любом из вышеприведенных вариантов исполнения.

[0024] Посредством настоящего изобретения можно достигнуть полезного эффекта, заключающегося в том, что в отличие от предшествующего уровня техники управляющая схема драйвера затвора в матрице, применяемая для дисплейного устройства с плоской панелью, содержит последовательно соединенные схему входного каскада, схему промежуточного каскада и схему выходного каскада и использует первый тактовый сигнал и второй тактовый сигнал, чтобы подавать сигналы в схему входного каскада, схему промежуточного каскада и схему выходного каскада с той целью, чтобы эти схемы последовательно генерировали соответствующие управляющие сигналы затвора. Изобретение устанавливает период прерывания в первом тактовом сигнале и во втором тактовом сигнале, причем когда сканирование с помощью первого тактового сигнала и второго тактового сигнала доходит до периода прерывания, управляющая схема драйвера затвора формирует прерывание между последовательно генерируемыми управляющими сигналами затвора, а по окончании периода прерывания управляющая схема драйвера затвора восстанавливает генерацию соответствующих управляющих сигналов затвора. Кроме того, в период прерывания дисплейное устройство с плоской панелью выполняет операцию обнаружения касания, за счет этого операция обнаружения касания может выполняться в процессе сканирования затворных шин драйвером, при этом не требуется ждать, пока будут просканированы все затворные шины, частота операции обнаружения касания увеличивается, и появляется возможность отслеживать несколько точек касания.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

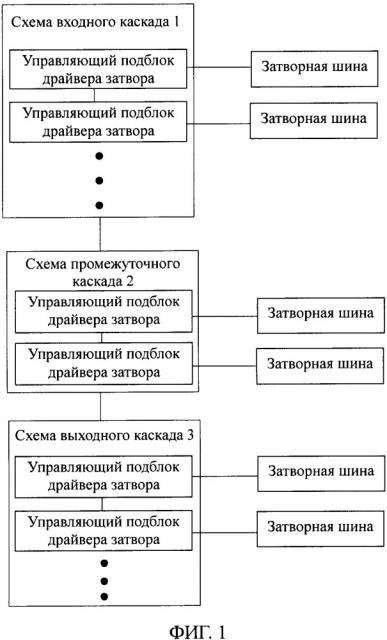

[0025] На Фиг. 1 показан структурный схематичный чертеж управляющей схемы драйвера затвора, применяемой для дисплейного устройства с плоской панелью, в одном из вариантов исполнения изобретения.

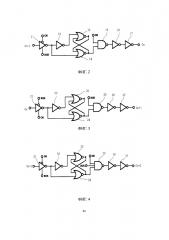

[0026] На Фиг. 2 показана принципиальная электрическая схема нечетного управляющего каскадного подблока драйвера затвора в схеме входного каскада в одном из вариантов исполнения настоящего изобретения.

[0027] На Фиг. 3 показана принципиальная электрическая схема четного управляющего каскадного подблока драйвера затвора в схеме входного каскада в одном из вариантов исполнения настоящего изобретения.

[0028] На Фиг. 4 показана принципиальная электрическая схема нечетного управляющего каскадного подблока драйвера затвора в схеме промежуточного каскада в одном из вариантов исполнения настоящего изобретения.

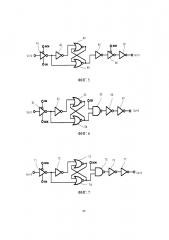

[0029] На Фиг. 5 показана принципиальная электрическая схема четного управляющего каскадного подблока драйвера затвора в схеме промежуточного каскада в одном из вариантов исполнения настоящего изобретения.

[0030] На Фиг. 6 показана принципиальная электрическая схема нечетного управляющего каскадного подблока драйвера затвора в схеме выходного каскада в одном из вариантов исполнения настоящего изобретения.

[0031] На Фиг. 7 показана принципиальная электрическая схема четного управляющего каскадного подблока драйвера затвора в схеме выходного каскада в одном из вариантов исполнения настоящего изобретения.

[0032] На Фиг. 8 показано схематическое представление временной диаграммы выходных сигналов управляющей схемы драйвера затвора для одного из вариантов исполнения изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ИСПОЛНЕНИЯ

[0033] В одном из вариантов исполнения изобретения предложена управляющая схема драйвера затвора, применяемая для дисплейного устройства с плоской панелью. Управляющую схему драйвера затвора встраивают в подложку матрицы и используют для подачи управляющих сигналов на затворные шины. Как показано на Фиг. 1, управляющая схема драйвера затвора содержит последовательно подключенные схему входного каскада 1, схему промежуточного каскада 2 и схему выходного каскада 3. Схема входного каскада 1 содержит многочисленные (т.е. более одного) управляющие подблоки драйвера затвора, соединенные каскадно. Схема промежуточного каскада 2 содержит два управляющих подблока драйвера затвора, соединенных каскадно, причем входная клемма первого управляющего каскадного подблока драйвера затвора в схеме промежуточного каскада 2 электрически соединена с выходной клеммой последнего управляющего каскадного подблока драйвера затвора в схеме входного каскада 1. Схема выходного каскада 3 содержит многочисленные управляющие подблоки драйвера затвора, соединенные каскадно, причем входная клемма первого управляющего каскадного подблока драйвера затвора в схеме выходного каскада 3 электрически соединена с выходной клеммой последнего управляющего каскадного подблока драйвера затвора в схеме промежуточного каскада 2. В этом варианте исполнения «соединенные каскадно» означает соединенные последовательно, т.е. выходная