Пороговый логический элемент

Иллюстрации

Показать всеРеферат

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союэ Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 13.1.1969 (№ 1303775/18-24) с присоединением заявки №

Приоритет

Опубликовано 01.17.1970. Бюллетень № 12

Дата опубликования описания 15Х11.1970

Кл. 21ат, 36/18

МПК Н 03k 21/06

УДК 681.325.65(088.8) Комитет по делам изобретений II открытий при Совете Министров

СССР

ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Изобретение относится к логическим элементам автоматики и вычислительной техники.

Известный пороговый логический элемент, состоящий из входных токовых переключателей, источника опорного и фиксирующих напряжений и выходного переключателя, содержит большое количество транзисторов, что увеличивает стоимость и снижает надежность его работы.

Целью изобретения является упрощение логического элемента. Это достигается тем, что в нем во входных переключателях и в источнике опорного и фиксирующих напряжений включены многоэмиттерные транзисторы, причем база многоэмиттерного транзистора входных переключателей соединена с первым эмиттером транзистора источника опорного и фиксирующих напряжений, два других эмиттера которого соединены со входами выходного переключателя, к одному из .которых подключен также коллектор многоэмиттерного транзистора входных переключателей, а каждый эмиттер последнего соединения с эмиттером одного из входных транзисторов.

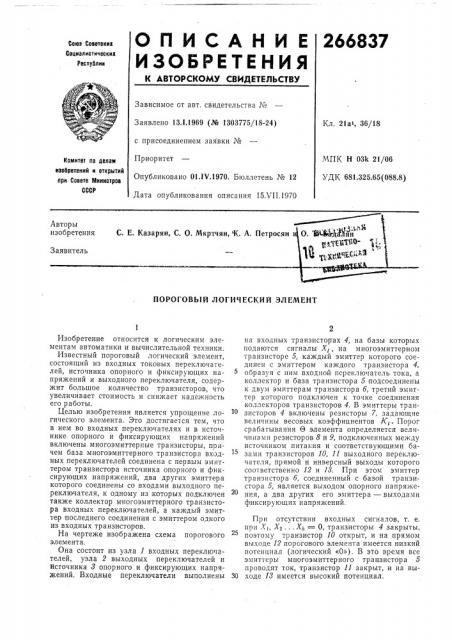

На чертеже изображена схема порогового элемента.

Она состоит из узла 1 входных переключателей, узла 2 выходных переключателей и источника 8 опорного и фиксирующих напряжений. Входные переключатели выполнены на входных транзисторах 4, на базы которых подаются сигналы Х;, на многоэмиттерном транзисторе 5, каждый эмиттер которого соединен с эмиттером каждого транзистора 4, образуя с ним входной переключатель тока, а коллектор и база транзистора 5 подсоединены к двум эмиттерам транзистора о, третий эмиттер которого подключен к точке соединения коллекторов транзисторов 4. В эмиттеры транзисторов 4 включены резисторы 7, задающие величины весовых коэффициентов К,. Порог срабатывания 0 элемента определяется величинами резисторов 8 и 9, подключенных между источником питания и соответствующими базами транзисторов 10, 11 выходного переключателя, прямой и инверсный выходы которого соответственно 12 и 18. При этом эмиттер транзистора 6, соединенный с базой транзистора 5, является выходом опорного напряжения, а два других его эмиттера — выходами фиксирующих напряжений.

При отсутствии входных сигналов, т. е. при Хь Хэ... Х5 — — О, транзисторы 4 закрыты, 25 ГОЭ1.0 у транзистор 10 открыт, и на пря. Окт1 выходе 12 порогового элемента имеется низкий потенциал (логический «О»). В это время все эмиттеры многоэмиттерного транзистора 5 проводят ток, транзистор 11 закрыт, и на вы30 ходе И имеется высокий потенциал.

266837 г1 х (1 !

Составитель В. Е, Йалюженич

Редактор О. Н. Кузнецова Техред Т. П. Курилко Корректор Л. Б, Бадылама

Заказ 181213 Тираж 480 Подписное

11НИИПИ Комитета по делам изооретений и открьпий при Совете Министров ГССР

Москва Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2."1опустим, что Кь Кг... Кз = +1 и

О = +2. Это значит, что при наличии сигнала на любых двух илн более входах из пяти пороговый элемент должен срабатывать и на его прямом выходе должен быть высокий потенциал (логическая «1»), а при наличии сигнала только на одном входе элемент не должен срабатывать. Из этих условий определяются величины резисторов 7, 8 и 9. Пусть

Х =Х = 1; Х,=Х,=Ха=О, тогда соответствующие транзисторы 4 открыты, и через резистор 8 протекает ток, соответствующий двум единицам. Поскольку О= +2, то падения напряжения на резисторе 8 достаточно для того, чтобы закрыть транзистор 10 и на выходе 12 элемента получить высокий уровень потенциала. При закрывании транзистора 10 транзистор 11 открывается и на выходе И будет низкий уровень потенциала. В этих условиях при поступлении сигналов на три и более функциональных входа элемента его состояние не изменяется, ток через резистор 8 возрастает, но до некоторого значения, после чего соответствующий эмиттерный переход многоэмиттерного транзистора 6 открывается и фиксирует низкий уровень напряжения на оазе транзистора 10.

При других комбинациях весовых коэффициентов и порога срабатывания схема рабога5 ет аналогичным образом.

Предмет изобретения

Пороговый логический элемент на переключателях тока, содержащий входные и выход10 ной переключатели и источник опорного и фиксирующих напряжений, отличающиася тем, что, с целью упрощения, в нем во входных переключателях и в источнике опорного и фиксирующих напряжений включены много15 эмиттерные транзисторы, причем база многоэмиттерного транзистора входных переключателей соединена с первым эмиттером транзистора источника опорного и фиксирующих напряжений, два других эмиттера которого сое20 динены со входами выходного переключателя, к одному из которых подключен также коллектор многоэмиттерного транзистора входных переключателей, а каждый эмиттер последнего соединен с эмиттером одного из входных

25 транзисторов.