Патент ссср 266944

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 266944

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ бсюа Советски»

Социалистически»

Респтблик

Зависимое от авт, свидетельства №

Кл, 21е, 36/10

Заявлено 18.1.1969 (№ 1307774/18-24) с присоединением заявки №

Приоритет

Опубликовано 01.1V.1970. Бюллетень № 12

Дата опубликования описания 8ХП.1970

МПК Ci 01г 31/28

УДК 621.327.53(088.8) Комитет по делам иаобретений и открытий при Совете Министров

СССР,:,; чвстс@й иетеит,-.о--. " б„бл„;,ета,:, .а "ДЬА-Автор изобретения

В. А, Пелипейко

Заявитель Институт электроники и вычислительной техники АН Латвийской ССР

СПОСОБ КОНТРОЛЯ ИНТЕГРАЛЪНЪ|Х СХЕМ «И — ИЛИ вЂ” НЕ»

ТИПА ТТЛ

Изобретение относится к контрольно-измерительной технике, в частности к технике измерения параметров цифровых интегральных схем, При синтезе логических устройств из интегральных схем возникает ряд вопросов, связанных с необходимостью согласования выходных и,входных параметпов интегральных схем для тото, чтобы обеспечить их нормальное функционирование в общей схеме синтезируемого устройства. Одним из таких параметров в интегральных схемах типа ТТЛ является уровень потенциала, который должен быть на коллекторном входе «ИЛИ», чтобы на выходе интегральной схемы обеспечивалось устойчивое состояние логического «О».

Цель предлагаемого изобретения состоит в разработке метода проверки интегральных схем типа ТТЛ, позволяющего определить совместимость работы интегральных схем данного типа по коллекторному входу «ИЛИ».

Эта цель достигается тем, что на входы «И» и эмиттерный вход «ИЛИ» контролируемой схемы подают нулевой потенциал, а на коллекторный вход «ИЛИ» — возрастающий потенциал, значение которого фиксируют по достижении заданного порогового уровня током выходного транзистора коммутации высокого потенциала.

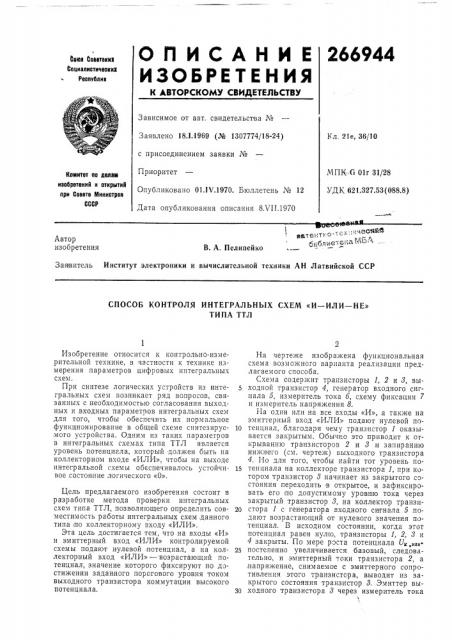

На чертеже изобрахкена функциональная схема возможного варианта реализации предлагаемого способа.

Схема содержит транзисторы 1, 2 и 8, выходной транзистор 4, генератор входного сигнала 5, измеритель тока б, схему фиксации 7 и измеритель напряжения 8.

На один или на все входы «И», а также на эмиттерный вход «ИЛИ» подают нулевой по10 тенциал, благодаря чему транзистор 1 оказывается закрытым. Обычно это приводит к открыванию транзисторов 2 и 8 и запиранию нижнего (см. чертеж) выходного транзистора

4. Но для того, чтобы найти тот уровень no1s тенциала на коллекторе тр-нзистора 1, при котором транзистор 8 начинает из закрытого состояния переходить в открытое, и зафиксировать его по допустимому уровню тока через закрытый транзистор 8, на коллектор транзи2р стора 1 с генератора входного сигнала 5 подают возрастающий от нулевого значения потенциал. В исходном состоянии, когда этот потенциал равен нулю, транзисторы 1, 2, 8 и

4 з акр ыты. По мере р эста потенциала U< .,,.

25 постепенно увеличивается базовый, следовательно, и эмиттерный токи транзистора 2, а ,напряжение, снимаемое с эмиттерного сопротивления этого транзистсра, выводит из закрытого состояния транзистор 8. Эмиттер вычо ходного транзистора 8 через измеритель тока

266944

Соста итель В. А. Комаров

Редактор О. Кузнецова Техред Т. П. Курилко Корректор М. П. Ромашова

Заказ 1740)12 Тираж 480 Подписное

ЦИИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

6 замкнут на «землю». Выходной сигнал измерителя тока вводят в схему фиксации 7, с помощью которой фиксируют достигнутый ypoBeHb напряжения Uz,èëè ° В тот UIOMeHT, когда ток через транзистор 8 достигнет контрольного уровня. Зафиксированное значение

U измеряют с помощью измерителя напряжения 8.

Чтобы уменьшить влияние нижнего выходного транзистора 4,на величину контролируемого тока, его базу закорачивают на «землю».

Предлагаемый способ позволяет найти статистический уровень или для каждой отдельной интегральной схемы ТТЛ тот максимально допустимый уровень логического «0» для коллекторного входа «ИЛИ», при котором логический «0» на выходе еще сохраняет свою устойчивость, что позволяет при подключении к этому входу «ИЛИ» схем-расширителей определять совместимость их работы.

Предмет изобретения

Способ контроля интегральных схем «И—

ИЛИ вЂ” НЕ» типа ТТЛ, отличающийся тем, что, с целью увеличения полноты контроля, на

10 входы «И» и эмиттерный вход «ИЛИ» контролируемой схемы .подаюг нулевой потенциал, и на коллекторный вход «ИЛИ» — возрастающий потенциал, значение которого фиксируют при достижении заданного порогового уровня

15 током выходного транзистора коммутации высокого потенциала.