Устройство для синхронизации импульсов

Иллюстрации

Показать всеРеферат

е сэквзичмтт пат а Фнт с i н. чбсн л бМзтифтектв МЙА

F Q n

ИЗОБРЕТЕНИЯ

267687

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства ¹

Заявлено 16.1Х.1968 (№ 1270132/18-24) с присоединением заявки ¹o

Приоритет

Опубликовано 02.IV.1970. Бюллетень ¹ 13

Дата опубликования описания 5Х111.1970

Кл. 21а, 36(18

МПК Н ОЗЬ 3/04

УДК 681.142.67(088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

Ю. В, Ерилов

Заявитель

УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ

Предлагаемое устройство для синхронизации импульсов предназначено для привязки асинхронных импульсов к импульсам тактовой частоты и может найти применение в устройствах преобразования, обработки и передачи 5 информации, синхронизированных тактовой частотой (например, в дискретных системах управления, телеметрии и т. д.).

Известны устройства для синхронизации импульсов, содержащие триггер, схему совпа- 10 дения и каскад задержки.

Предложенное устройство отличается or известных тем, что в него введены два инвертора и две вентильные схемы, причем выход триггера подключен к первому входу 15 первой вентильной схемы, выход которой через инвертор соединен с первым входом второй вентильной схемы, второй вход которой подключен к источнику синхронизирующих импульсов, а ее выход через инвертор соеди- 20 нен со вторым входом первой вентильной схемы и с первым входом схемы совпадения.

Это позволяет повысить точность привязки асинхронных импульсов к импульсам частоты синхронизации. 25

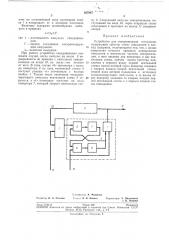

На чертеже приведена блок-схема описываемого устройства.

Устройство содержит триггерную ячейку 1, схему задержки 2 и комбинационную логическую схему 8, в состав которой входят схема 30 совпадения 4, две вентильные схемы 5, б и два инвертора 7, 8.

В исходном состоянии ячейка 1 находится в состоянии «О». «О» потенциал с выхода ячейки 1 поступает на один из входов вентпльной схемы 5. Независимо от потенциала на другом входе вентильной схемы 5 íà выходе соединенного с ней инвертора 7 поддерживается

«1» потенциал, который подается на один из входов вентильпой схемы б. При отсутствии синхронизирующего импульса на входе 10, с выхода инвертора 8 снимается «1» потенциал, поступающий на входы схемы совпадения

4 и вентильной схемы 5. На выходе схемы совпадения 4, а значит и на выходе 11 устройства — «О» потенциал.

Поступивший на вход 9 асинхронный входной импульс опрокинет ячейку 1. «1» потенциал с выхода ячейки через открытую вентпльную схему 5 поступает на вход инвертора 7. «О» потенциал, снимаемый с выхода инвертора 7, закрывает вентильную схему б, при этом независимо от потенциала на ее другом входе на выходе инвертора 8 действует

«1» потенциал. Поступивший вслед за этим на вход 10 импульс синхронизации через открытую схему совпадения 4 проходит на выход 11 устройства и на вход схемы задержки

2. Задержанный импульс, в виде импульса сброса с выхода 12 схемы задержки 2, посту. л

267687 т(з(7, Предмет изобретения

Составитель А. Федорова

Техр=д Л. Я. Левина

Редактор Л. А. Утехина

Корректоры: E. Ласточкина и В. Петрова

Заказ 2136!12 Тира)к 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская паб., д. 4!5

Типография, пр. Сапунова, 2 пает на установочный вход триггерной ячейки l и возвращает ее в исходное состояние.

Величину задержки целесообразно выбирать в пределах где т — длительность импульса синхронизации;

T — период следования синхронизирующих импульсов;

1а — величина задержки.

При работе устройства синхронизации возможен случай, когда импульс на входе 9 перекрывается во времени с импульсом синхронизации па входе 10, но HecK() .ко отстает от него. В этом случае «0» потенциал с выхода инвертора 8 на вход вентильной схемы 5 поступит раньше «1» потенциала с выхода ячейки 1. Только после окончания синхронизирующего импульса вентильная схема 5 откроется и «1» потенциал поступит на вход инвертора 7, который закроет вентильную схему б. Следующий импульс синхронизации, поступивший на вход 10, через открытую схему совпадения 4 проходит на выход 11 синхронизатора.

Устройство для синхронизации импульсов, содержащее триггер, схему совпадения и кас10 кад задержки, отличающееся тем, что, с целью повышения точности привязки асинхронных импульсов к импульсам частоты синхронизации, в него введены два инвертора и две вентильные схемы, причем выход триггера под15 ключен к первому входу первой вентильной схемы, выход которой через инвертор соединен с первым входом второй вентильной схемы, второй вход которой подключен к источнику синхронизирующих импульсов, а ее выход че20 рез инвертор соединен со вторым входом первой вентильной схемы и с первым входом схемы совпадения,