Разностное счетное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

2680I7

Союз Соеетских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 14.II.1969 (¹ 1313123/18-24) Кл. 42m>, 7/00 с присоединением заявки №

Приоритет Опубликовано 02.IV.1970, Бюллетень ¹ 13

Дата or убликования описания 31Л 11.1970

МПК H 03k 23/04

УДК 681.3.055 (088.8) Комитет по делам изобретений и открытий при Соеете Мииистрое

СССР

Авторы изобретения

В, Ф. Королев и А. П. Утехин

Заявитель

РА3НОСТНОЕ СЧЕТНОЕ УСТРОЙСТВО

Предлагаемое ycrpoIIcrao может оыть использовано в радиотехнических установках, B частности в ядерно-физической аппаратуре различного назначения, в том числе и полевь1х портативных приборах, где ставится задача регистрации разности в числе импульсов, проходящих в течение двух или нескольких последовательных отрезков времени (например, автоматическое вычитание фоновой радиации, выполнение анализатора для рентгенорадиометрического анализа и т. д.). Аналогичные задачи возникают часто и ripII предварительной обработке накопленной информации.

Известны разностные счетные устройства:a четырех симметричных триггерах с перекрестной связью, разделенных ключевыми каскадами, которые управляют режимами суммирования и вычитания, а введением обратной связи.

Вывод данных о числе накопленных импульсов обеспечивается с помощью привода на люминесцентный знаковый индикатор.

Так как в большинстве случаев объем IIaмяти счетных схем составляет не менее 10 импульсов, основными недостатками известнь1х устройств является сложность (по числу используемых элементов) и значительная потребляемая мощность, что практически искл1очает применение их в портативной аппаратуре.

Данное устройство для упрощения ewe;II» разностного счета двух или нескольких последовательностей импульсов, поступающих на один и тот же вход схемы памяти, упрогцения вывода информации и сокращения потребляемой мощности содержит переключатель разрядов, входы которого соединены с программным переклю ателем и выходом индицированного декадного счетчика, а выходы—

10 со схемой пропускания, ключом связи между входом устройства и декадными счетчиками схемы памяти, а также с клIочами связи между декадными счетчиками. Схема знака разности подключена к выходу схемы памяти и

15 ключам связи между декадными счетчиками схемы памяти, а также к схеме пропускания управляющих импульсов и к программному переключателю, связанному с ключами блока преобразования.

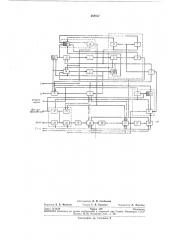

20 Блок-схема устройства изображена на чертеже.

Устройство состоит нз двух ф нкциональных частей — блока преобразования и регистрирующей схемы памяти. Блок преобразования

25 включает в себя буферный декадный счетчик

1, индицирова ный декадный счетчик 2, управляющий симметричный триггер 8 с раздельным запуском, переключатель разрядов 4, представляющий собой пересчетную схему, 30 программный переключатель 5. Ключи b — 9 и

268017 симметричный триггер 10 с раздельным запуском образуют ключевую схему связи. Симметричный триггер 11 с несколькими входа и и ключ 12 составляют пропускатель управляlñщих импульсов, аналогичный пропускатслям

18 — 16. Пропускатель 16, ключ 17 и симметричный триггер 18 с раздельным запуском образуют схему знака разности. Регистрирующая счетная схема состоит из и последовательно включенных декадных счетчиков 19—

21. Ключи 2 — 24 и импульсный согласующий усилитель 25 составляют каскад связи ме2кду первым десятичным счетчиком и входом усгройства. Лналогичные каскады связи 26 — 28 соединяют соответствующие десятичные счстчики.

На вход А устройства подают две последовательности импульсов Л, = т... ba u

N2 — — ml .-.. bla, при регистрации которых должна быть получена их разность Л,— Л .„ где a>b... т,а lbl... m> — значения разрядов данных последовательностей импульсов. Для простоты рассмотрим процесс (порядок операций) получения разности двух последовательностей импульсов N; = a< 10 и Ж2 = а < 10 при их регистрации счетной схемой памяти, состоящей из одного декадного счетчика. Могут быть два варианта очерсдности поступления на вход схемы памяти числа импульсов

N1) N2 и Л 1(Л 2, Вариант У1)У2.

После регистрации числа импульсов Л,=а состояние декадного счетчика схемы памяти преобразуется сначала в результате добавления единицы в (а+1), а затем путем вычитания из десяти в состояние 10 — (а+1). (исло импульсов Л4=а суммируется с преобразованным состоянием 10 — (а+1). По окончании регистрации Л2 декадный счетчик схемы па llÿòè оказывается в состоянии 10 — (а + 1) + ol, которое путем добавления единицы и последующего вычитания из десяти преобразуется и состояние, соответствующее разнссти двух последовательностей импульсов.

В случае многозначных последовательностей импульсов число декадных счетчиков счетной схемы выбирают из условия N (10, где

n — число декадных счетчиков. После регистрации N, операции а+ 1 и 10 — (а+ 1) происходят в каждом разряде числа без переноса единицы в соседний старший разряд.

Вариант „V (N .

Операции после регистрации У2 те же, что и при варианте Nl)N. После регистрации

Л2 как при одноразрядном, так и при многоразрядном числах проводится лишь операция добавления единицы в младший разряд с последующим переносом импульса наполнения разрядов в соседний старший разряд.

Операция «а» проводится в момент прихода импульсов, при этом все декадные счет-яки включены последовательно.

Операция а+ 1.

К моменту начала преобразования пропускатель, образованный из триггера 11 и клю5

1О

65 ча 12, и аналогичные ему пропускатели 18 —15 закрыты, а пропускатель 16 схемы знака разности открыт. Программный переключатслb

5 устанавливает ключ 6 закрытым, а ключ 7 и 8 — открытыми. Переключатель разрядов 4 находится в поло>кении, при котором подк110чен декадный счетчик 2(схемы памяти. добавление единицы во все разряды происходит по скончании регистрации последовательности импульсов (срабатывание таймера). В этот момент послсдовате IbHblp связи ме2еду дскад1!Ими счетчиками с .смы памяти разорваны вследствие запирания внешним сигналом «стоп» ключа 2<3 входного каскада связи и аналогичных ему B каскадах связи 26—

28.

Одновременно с приходом сигнала «стоп» внешний импульс «пуск преобразования» подготавливает триггер 18 к приему импульса частотой f2 и через ключ 17 открывает пропускатсль 15. С приходом импульса частотой

f2 триггер 18 через пропускатсль 16 добавляет единицу ьо все разряды счетной схемы через согласующий усилитель 25 входного каскада связи и аналогичных ему усилителей каскадов связи 26 и 27.

Операция 10 — (а+1).

Одновременно с приходом импульса частотой f2 2управляющий триггер 8 подготавливается к приему импульса цикла преобразования состояния разряда схемы памяти, пропускатель 14 открывается, и импульсы частогой ), дополняют до десяти индицировапный декадный счетчик 2, выходной импульс которого закрывает пропускатель 14 и перебрасывает управляющий триггер. Импульсом последнего триггер 11 перебрасывается в поло>кение, TIpH котором ключ 12 открывается.

Пропускатель 13, в котором происходят аналогичные преобразования, также открывается.

Таким образом, импульсы частотой f< поступают одновременно на декадные счетчики 1 и 21. После прихода в декадный счетчик 21 старшего разряда схемы памяти числа импульсов 10 — (а+ 1) оп запо".íÿåòñÿ ас десяти и выдает импульс, который открывает пропускатель 14 и через ключ 8 перебрасывает триггер 11, закрывающий ключ 12, что обеспечивает поступление импульсов частотой в декадные счетчики 1 и 2.

При заполнении буферного декадного счетчика 1 до десяти его выходной импульс перебрасывает триггер 11 в положение, при котором открывается ключ 12, закрывает пропускатель 18 и подготавливает к приему выходного импульса индицированного декадного счетчика 2 триггер 10. С приходом импульса со счетчика 1 счетчик 2 регистрирует (а+1) импульсов. В этот момент счетчик 21 схемы памяти готов к приему импульсов дополнения с частотой f . После заполнения счетчика 2 до десяти счетчик 21 регистрирует 10 — (а+1) импульсов. Импульсом счетчика 2 перебрасывается триггер 10, который в свою очередь перебрасывает триггер 11, закрывая ключ .12.

268017

Одновременно закрывается пропускатель 14, а переключатель 4 подключает декадный счетчик схемы памяти разряда и — 1.

Время Т преобразования схемы памяти вы30п бирают из условия Т), где и — чис lo

Л декадных счетчиков. С приходом следующего импульса частотой / (преобразуется соЛ зо стояние декадного счетчика следующего разряда счетной схемы и т. д. После преобразования младшего разряда выходным импульсом переключателя разрядов пропускатель 15 закрывается. Счетная схема готова к регистрации последовательности импульсов N-. Переключатель разрядов находится в положении, при котором подключен старший разряд.

Операция «+1» в младший разряд.

После заполнения счетной схемы при регистрации последовательности импульсов N» выходной импульс декадного счетчика 21 старшего разряда через ключевой каскад 28 закрывает пропускатель Iб и ключ 17, а ключ

22 открывается. По окончании регистрации импульсов N (срабатывание таймера) на данное устройство подаются импульс «пуск преобразования» и сигнал «стоп». Импульс

«пуск преобразования» опережает сигнал

«стоп» на время, достаточное для переноса единицы во всех разрядах схемы памяти. Импульс «пуск преобразования» через ключ 22 добавляет к состоянию счетной схемы единицу. Состояние декадных счетчиков схемы памяти не изменяется, так как ключ 17 закрыт, и пропускатель 15 становится неуправляемым.

Режим вывода информации из схемы памяти определяется положением программного переключателя 5, при котором ключи 7 и 8 закрыты, ключи б и 9 открыты и пропускатель

Iб закрыт. Состояние остальных узлов устройства аналогично режиму преобразования 4о после регистрации последовательности импульсов Ni. Опрос декадных счетчиков начинается со старшего разряда схемы памяти (срабатывание таймера) после получения разности или зарегистрированной последователь- 4> ности импульсов. В этом случае программный переключатель 5 блокирует схему преобразования.

С подачей разового импульса опроса пропускатель 15 открывает пропускатель 14 и подготавливает к приему импульса цикла управляющий триггер 3. Импульсы частотой f> через пропускатель наполняют индицированный декадный счетчик 2, и он сбрасывается в нуль.

Выходной импульс с него закрывает пропускатель 14 и перебрасывает триггер 3. Выходной импульс управляющего триггера перебрасывает триггер 11, открывает ключ 12 и пропускатель 13. Таким образом, на входы опрашиваемого разряда и буферного декадного счетчика

1 поступают импульсы частотой f . Пусть опрашиваемый декадный счетчик 21 находится в состоянии «m». С регистрацией им числа импульсов 10 — m его выходной импульс открывает пропускатель 14. В этот момент счетчик

1 регистрирует 10 — т импульсов, а счетчики

2 и 21 находятся в состоянии «нуль». Д;гя дополнения счетчика 1 до десяти на его вход, а, следовательно, и на счетчики 2 и 21 должно поступить m импульсов. По заполнении счетчика 1 его выходной импульс перебрасывает триггер 11, закрывает ключ 12 и пропускатели 13 — 15 и одновременно подключает следующий разряд за счет автоматического перехода в новое состояние переключателя разрядов 4. С приходом следующего импульса опроса начинается аналогичный процесс вывода информации.

Вывод информации проходит без разрушения памяти счетной схемы. Возможна индикация номера опрашиваемого разряда с помощью переключателя 4.

Предмет изобретения

Разностное счетное устройство, содержащее схему памяти из и последовательно включенных через ключи декадных счетчиков и блок преобразования, выполненный из буферного и индицированного декадных счетчиков, триггеров, ключей, схем пропускания, схемы знака разности и программного переключателя, отличаюгггееся тем, что, с целью обеспечения возможности работы по одному счетному входу, упрощения как разностного устройства, так и схемы вывода информации, уменьшения потребляемой мощности, оно содержит переключатель разрядов, соединенный входами с программным переключателем и с выходом индицированного декадного счетчика, а выходами — со схемой пропускания, ключом связи между входом устройства и декадными счетчиками схемы памяти, а также с ключами связи между декадными счетчиками; схема знака разности подключена к выходу схемы памяти и ключам связи между декадными счетчиками схемы памяти, а также к схеме пропускания управляющих импульсов и к программному переключателю, связанному с ключами блока преобразования.

268017.г2 — "1 г

Корректор Л. Фирсова

Редактор Б. Б. Федотов

Типография, пр. Сапунова, 2

Ыыулос

ar,,ооса гфст преедраюода атее

Составитель Л. В. Скобелева

Текрсд Т. П. Курилко

Заказ 2134/16 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва 7К,-35, Раушская наб., д. 4/5