Латентно -^^^ \ ^^ пхничсс-.л j бн:>&лчотсп-х

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 30.!.1969 (№ 1307082/18-24) с присоединением заявки №

Приоритет

Опубликовано 26.Ч.1970. Бюллетень ¹ 18

Дата опубликования описания 10.IX.1970

Кл. 42m, 11/00

МПК G 06f 11/00

УДК 681.326.77(088.8) Комитет по делам изобретвииЯ и открытиЯ

IlpM Совете Мииистров

СССР

Авторы изобретения

Г. А. Захарян, Л. М. Чахояи и А. О. Чоликяи

Заявитель

Ъ11 г. 1 Я 0 "Хii 1

ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С БЛОКИРОВКОЙ НЕИСПРАВНЫХ АДРЕСОВ

Настоящее изобретение относится к области .вычислительной техники и может быть использовано в оперативных запоминающих устройствах ЦВМ повышенной надежности.

Известны оперативные запоминающие устройства (ОЗУ), в которых с целью повышения надежности выполняется обход;неисправных адресов, т. е. адресов, в разрезах которых.имеются один или более неисправных запоминающих элементов (ЗЭ). ОЗУ работает при этом следующим образом. На регистр адреса посту. пает код адреса, по которому выбирается информация. При выдаче исправной информации ОЗУ функционирует как обычно. При наличии же неисправности происходит о6ращение к дополнительному полю по коду адреса, записанному в неисправном адресе. Такихт образом, при наличии неисправности в какомлибо адресе для получения правильной информации необходимо дважды обращаться к ОЗУ.

Целью настоящего изобретения является увеличение быстродействия ОЗУ за счет сокращения времени, необходимого на формиро.вание и дешифрацию, нового адреса при ооращении по неисправному адресу. Это достигается путем блокировки выходного элемента дешифратора, соответствующего неисправному адресу, .и одновременного разрешения срабатывания элемента .выборки из дополнительного поля запоминания информации, соответств ющего исправному адресу.

Предложенное устройство отличается от известных тем, что выход блока обнаружения не5 исправного адреса соединен со входами олока дешифратора адреса и элемента выборки из дополнительного поля запоминания информации.

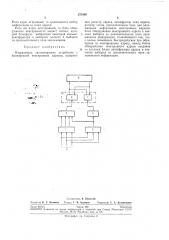

На чертеже приведена блок-схема ОЗУ с

10 блокировкой неисправных адресов.

ОЗУ с блокировкой неисправных адресов содержит регистр адреса 1, дешифратор 2 кода адреса, блок 8 обнаружения неисправного адреса, элемент 4 выборки из дополнительно15 го поля запоминания информации, накопитель

5, который содержит основное 6 и дополнительное 7 поля запоминания информации и регистр числа 8. Блок 3, связанный с дешифратором 2 кода адреса, блокирует выход

20 элемента дешпфратора, соответствующего неисправному адресу, и разрешает срабатывание элемента выборки из дополнительного поля запоминания информации, соответствующего исправному адресу. Прием и выдача ин25 формации в накопитель 5 производится через регистр числа 8.

Код адреса 9 поступает одновременно на регистр адреса 1 и блок 8 обнаружения неисправного адреса. По коду адреса выбирается

30 один из выходных элементов дешифратора 2.

271895

Предмет изобретения

Фв ° g ° ° Ф4Ф е о

Составитель В. Шумский

Редактор Б. С. Панкина Текред Т. П. Курилко Корректор С. А. Кузовенкова

Заказ 2421i5 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Я(-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Если адрес исправный, то производится выбор информации из этого адреса.

Если же адрес неисправный, то блок обна ружения неисправности выдает сигнал, который блокирует выбранный выходной элемент дешифратора и выбирает элемент 4 выборки из дополнительного поля запоминания.

Оперативное запоминающее устройство с блокировкой неисправных адресов, содержащее регистр адреса, дешифратор кода адреса, регистр числа, дополнительное поле для запоминания информации неисправных адресов, блок обнаружения неисправного адреса и эле5 мент выборки из дополнительного поля запоминания информации, отличающееся твм, что, с целью повышения быстродействия при обращении по неисправному адресу, выход блока обнаружения неисправного адреса соединен

lo со входами блока дешифратора адреса и элемента выборки из дополнительного поля запоминания информации.