Дискретная вычислительная среда

Иллюстрации

Показать всеРеферат

t Ll ) ОПИСАНИ Е 272365

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства ¹

Заявлено 13.1Х.1967 (¹ 1183456/18-24) Кл. 21а.т, 36/18 с присоединением заявки ¹

Приоритет

МПК Н 03k

УДК 681.325.65(088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Опубликовано ОЗ,VI.1970. Бюллетень ¹ 19

Дата опубликования описания ЗО.Х.1970

Авторы изобретения

Ю. А. Попов и П. Е. Бочков

Заявитель

Московский инженерно-физический институт

ДИСКРЕТНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА

Предложение относится к области автоматики и вычислительной техники и предназначено для построения логических и вычислительных устройств.

Известны дискретные вычислительные среды (однородные структуры), перенастройка которых в процессе работы возможна лишь в случае, когда на элементах структуры реализованы элементы памяти для хранения промежуточных результатов.

Предложенная дискретная вычислительная среда отличается тем, что управляемые связи между функционально-логическими элементами среды содержат элементы кратковременной памяти.

3То позволяет уменьшить число элементов, используемых для реализации заданной функции, при перенастройке среды.

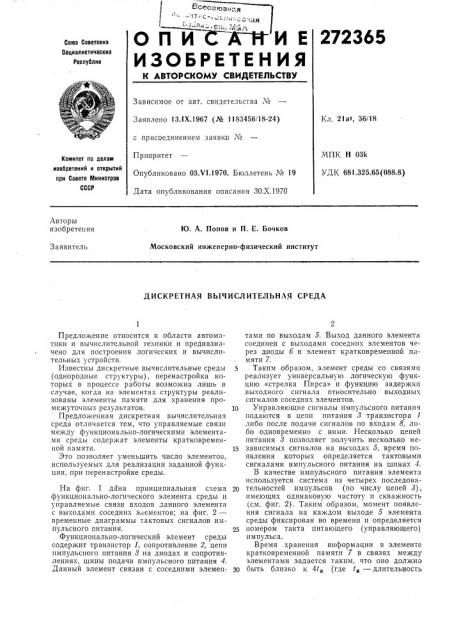

На фиг. 1 дана принципиальная схема функционально-логического элемента среды и управляемые связи входов данного элемента с выходами соседних э. ементов; на фиг. 2— временные диаграммы тактовых сигналов импульсного питания.

Функционально-логический элемент среды содержит транзистор 1, сопротивление 2, цепи импульсного питания 8 на диодах и сопротивлениях, шины подачи импульсного питания 4.

Данный элемент связан с соседними элементами по выходам 5. Выход данного элемента соединен с выходами соседник элементов через диоды б и элемент кратковременной памяти 7.

Таким образом, элемент среды со связями реализует универсальную логическую функцию «стрелка Пирса» и функцию задержки выходного сигнала относительно выходных сигналов соседних элементов.

1р Управляющие сигналы импульсного питанич подаются в цепи питания 8 транзистора 1 либо после подачи сигналов по входам 8, либо одновременно с ними. Несколько цепей питания 8 позволяет получить несколько не15 зависимых сигналов на выходах 5, время появления которых определяется тактовыми сигналами импульсного питания на шинах 1.

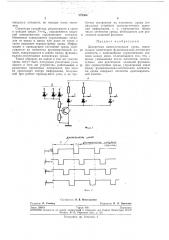

В качестве импульсного питания элемента используется система из четырех последова2р тельностей импульсов (по числу цепей 8), имеющих одинаковую частоту и скважность (см. фиг. 2). Таким образом, момент появления сигнала на каждом выходе 5 элемента среды фиксирован во времени и определяется номером такта питающего (управляющего) импульса.

Время хранения информации в элементе кратковременной памяти 7 в связях между элементами задается таким, что оно должно быть близко к 4t, (где („— длительность

272365

Предмет изобретения я иг. 1

g óèiïåïüíàñòü i1и.ла

МП .11ьСа

<Риг 2

Составитель В. В. Игнатущенко

Корректор H. Л. Бронская

Редактор Л. Утехина

Заказ 308914 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий |рп Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 4;5

Типография, пр. Сапунова, 2 импульса питания), но меньше этого значения.

Структура устройства, реализуемого в среде в каждом цикле T=4t„, определяется заданной совокупностью управляющих сигналов.

Изменение совокупности управляющих сигналов от цикла к циклу или даже от такта к такту вызывает перенастройку среды. Информация о предыдущем состоянии среды записывается на элементах кратковременной памяти, содержащихся в связях между функционально-логическими элементами среды.

Таким образом, на одном и том же участке среды могут быть построены различные узлы одного и того же устройства, работающие в различных временных интервалах; при этом не происходит потери информации, полученной при работе предыдущего узла, и не требуется построения на элементах среды специальных устройств промежуточного хранения информации, т. е. уменьшается общее число элементов среды, необходимое для реализации заданной функции.

Дискретная вычислительная среда, содер10 жащая однотипные функционально-логические элементы с одинаковыми управляемыми связями между ними, отлича ощаяся тем, что, с целью уменьшения числа элементов, используемых для реализации заданной функции, 1S при перенастройке среды, управляемые связи между функционально-логическими элементами среды содержат элементы кратковременной памяти.