Сумматор параллельного действия

Иллюстрации

Показать всеРеферат

272672

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 28.Vill.1969 (№ 1265519/18-24) с присоединением заявки №

Приоритет

Опубликовано ОЗ.V1,1970. Бюллетень X 19

Дата опубликования описания 16.IX.1970

Кл. 42m"., 7/50

МПК G 06f 7/50

УДК 681.325.54 (088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

Заявитель

А. Е. Бобров

Ленинградский институт инженеров железнодорожного транспорта имени акад. В. Н. Образцова и

СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ

Сумматор может быть использован в вычислительных устройствах и машинах на ферриттранзисторных ячейках различных типов.

Известны сумматоры параллельного действия на феррит-транзисторных ячейках, дей- 5 ствие которых основано на компенсационном или разновременном способе гашения информации (запрета) .

Недостаток известных схем заключается в том, что и компенсационный и разновремсн- 10 ный ре>кимы запрета (гашения) существенно отличаются от типового режима работы ферриттранзисторной ячейки «запись — считывание». Это приводит к усложнению схем и снижает надежность работы сумматоров. 15

Предлагаемый сумматор отличается от известных тем, что в нем шины первого и второго слагаемых подключены, соответственно, ко входам записи первой ячейки и второй и третьей ячеек и соединены со входами. первой 20 схемы «ИЛИ», выход которой связан со входом записи четвертой ячейки и со входом считывания седьмой ячейки. Выход первой ячейки соединен со входом считывания третьей и со входом второй схемы «ИЛИ», на второй 25 вход которой подключен выход второй ячейки. Выход второй схемы «ИЛИ» соединен со входом записи седьмой ячейки, выходы третьей и четвертой ячеек подключены ко входам третьей схемы «ИЛИ», выход которой соеди- 30 нен со входом считывания восьмой ячейки.

Шина переноса из младшего разряда соединена со входом считывания четвертой и входом записи пятой ячейки, выходы пятой и шестой ячеек подключены ко входам четвертой схемы

«ИЛИ», выход которой соединен со входом записи девятой и входом считывания десятой ячейки. Выход седьмой ячейки соединен со входом считывания шестой, а выход девятой соединен со входом записи десятой.

Это дает возможность повысить надежность и упростить схему сумматора.

В сумматоре используется временной парафазный код.

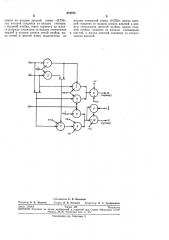

Схема устройства приведена на чертеже.

Сумматор на феррит-транзисторных ячейках 1 — 10 имеет три входа (два входа слагаемых 11 и 12 и вход 13 переноса из младшего разряда) и два выхода (перенос в старший разряд 14 и выход суммы 15).

Ячейки 1, 2, 5 и 9 предназначены для задержки информации на один такт, ячейки 3, 4, 7 и 10 — для конъюнкций, а ячейки 6 и 8— для восстановления взапмоинверсного значения рабочих тактов.

Входы слагаемых 11 и 12 подключены па запись в ячейку 1 и ячейки 2 и 3, соответственно, после чего они объединяются и их дизьюнкция подается на запись в ячейку 4 и считывание с ячейки 7. Вход 13 переноса из млад272672

ЗНАЧЕНИЕ ИНФОРМАЦИИ

На выходе сумматора

На выходах ячеек

На входах ячеек

12

10 л ъ

4 о

Sl »

Й о

СЧ ъ

»75

& о

И м

СЧ

Ьъ (» о

g) Ъ

f»

М

f» о

И И ъ

f»

М

Ф

Е» о

С Ъ

1»»

f»

М

f" о

РЪ ъ

& о

»л ъ

6" о

Шего разряда подан на считывание с ячейки

4 и на запись в ячейку 5. Выход ячейки 1 подключен на считывание с ячейки З, после чего он объединяется с выходом ячейки 2 и подключается на запись в ячейку 7. Выходы ячеек

3 и 4 объединены и поданы на считывание с ячейки 8. Выходы ячеек 5 и б также объединены и поданы на запись в ячейку 9 и считывание с ячейки 10. Выход ячейки 7 подан на считывание с ячейки б. Выход ячейки 9 подан на запись в ячейку 10. Выход ячейки 8 является выходом переноса в старший разряд, а выход ячейки 10 — выходом суммы.

Кроме того, для нормальной работы сумматора к схеме подключены постоянно идущие сигналы тактов, На чертеже тактовые сигналы обозначены буквой п и номером, например п1, п4 и т. д. Если на ячейку подключены два тактовых входа, на чертеже номера этих так2 тов обозначены в виде дроби, например и —.

Такт п1 подан на считывание с ячеек б и 7, на запись в ячейку 8 и считывание с ячейки 5.

Такт п2 подан на запись в ячейку б, на считывание с ячеек 1, 2 и 9. Такт пЗ подан на

Предмет изобретения

Сумматор параллельного действия, содержащий феррит-транзисторные ячейки, отличающийся тем, что, с целью повышения .надежности и упрощения схемы сумматора, шины первого и второго слагаемых подключены

""oîòâåòñòâåHíî ко входам записи первой ячейКи и второй и третьей ячеек и соединены со

4 считывание с ячейки 10 и с ячейки 5. Такт п4 подан на считывание с ячеек З, 4 и 8, на считывание с ячеек 1, 2 и 9.

Слагаемые подаются во временном пара5 фазном коде по тактам п1 и пЗ, а временной парафазный код переноса из младшего разряда — по тактам п2 и п4. Код суммы получается по тактам nI и пЗ с задержкой на один период по сравнению со временем прихода кода

10 слагаемых.

Для работы сумматора требуется не менее четырех тактов.

Подробное описание работы сумматора дается в виде таблицы, в которой:

15 наличие импульса (в обмотке, на входе и выходе ячейки и т. д.) обозначается единицей, отсутствие — нулем; временные параметры импульса (сигнала) даются в виде гР где t — номер такта, р — но20 мер периода, в котором рассматривается (вырабатывается) сигнал, причем считается, что коды слагаемых подаются по тактам 1 и 3;

Как видно из таблицы, на выходах суммы

15 и переноса 14 информация получается во

25 временном парафазном коде. входами первой схемы «ИЛИ», выход которой связан со входом записи четвертой ячейки и со входом считывания седьмой ячейки, выход первой ячейки соединен со входом считывания

30 третьей ячейки и со входом второй схемы

«ИЛИ», на второй вход которой подключен выход второй ячейки, выход второй схемы

«ИЛИ» соединен со входом записи седьмой ячейки, выходы третьей и четвертой ячеек под272672

Щ енос) 15 ма) Составитель Е. И. Иванеева

Техред Л. В. Куклина Корректор Н. С. Сударенкова

Редактор Б. Б. Федотов

Заказ 2243)2 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2.очены ко входам третьей схемы «ИЛИ», ход которой соединен со входом считывач восьмой ячейки, шина переноса из младго разряда соединена со входом считывания вертой и входом записи пятой ячейки, вы ы пятой и шестой ячеек подключены ко входам четвертой схемы «ИЛИ», выход которой соединен со входом записи девятой и входом считывания десятой ячейки, выход седьмой ячейки соединен со входом считывания шестой, а выход девятой соединен со входом записи десятой.