Патент ссср 275123

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ 275I23

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

1хл. 21а>, 36 18

Заявлено 08.Х11.1968 (№ 1289537/18-24) с присоединением заявки №

Приоритет

Опубликовано 03.И1.1970. Бюллетень ¹ 22

Дата опубликования описания 6.Х.1970.ЧГ1К Н 031< 19/40

УДЫ 621.374.3(088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

С. А. Бирюков

Заявитель

ИНВЕРТОР

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных машинах, построенных на интегральных схемах.

Известны инверторы, применяемые в вычислительных машинах, содержащие входной многоэмиттерный транзистор, промежуточный транзистор и выходной каскад, выполненный на двух последовательно соединенных транзисторах, причем для надежного запиранпя одного из них в его эмиттерную цепь включен диод. Для паде>кной работы такого ипвертора в диапазоне температур от — 60 до +120 С необходимо напряжение питания 5 в.

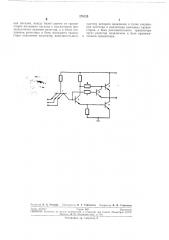

Предложенный инвертор отличается тем, что в нем с целью понижения величиш.! напряжения питания в!ежду базой одного из транзисторов выходного каскада и коллектором промежуточного транзистора включен резистор, а к точке соединения резистора и базы выходного транзистора подключен коллектор дополнительного, эмиттср которого подключен к точке соединения эмиттера и коллектора выходных транзисторов, а база дополнительного транзистора через резистор подкгиочеиа к базе проме куто шого транзистора.

1-1а чертеже приведена схема инвертора.

Инвертор содержит входной многоэмиттерный транзистор 1, промежуточный транзистор

2 и выходной каскад, состоящий из транзисторов 8 и 4. С целью надежного запирания транзистора 8 прп подаче высокого потепциа IB на вход инвертора между его базой и коллектором транзистора 2 введен резистор о, к базе транзистора 8 подключен дополнительный транзистор 6, эмиттер которого присоединен к эмиттеру транзистора 8, а б",çà через резистор

7 — к базе промежуточного транзистора 2.

При подаче низкого потенциала па вход ин10 вертора транзисторы 2, 4 и 6 заперты, и на выходе инвертора вь!сонин потенциал. При подаче высокого погеициала на вход транзисторы 2, 4 и 6 включены п насыщены, благодаря чему транзистор 8 заперт.

Использование для надежного запирания транзистора 8 дополнительного транзистора 6 вместо диода, включенного в цепь эмиттера, позволясг применить в диапазоне температур — 60 —: +120 С напряжение ш!таш!я 4 в, что

20 при сохранении потребляемой мощности повышает быстродействие, снижает суммарное сопротивление схемы и повышает ее надежность.

Предмет изоо тстсния

25 !

Инвертор, содержащий промежуточный дополнительный транзисторы и вь!ходной каскад, выполненный»а дву; последовательно соединеги!ых транзисторах, отлLEчают!1ийс.! тем, 30 по, с целью понижения величины напряже275123

Редактор Л. А. Утехина Составитель В. Г. Гордонова Корректор Л. И. Гаврилова

Заказ 2770,17 1 прая 480 Подписное

ЦНИИПИ 11озшгста Jlo дслаги изобретениий и открытий при Совете Министров СССР

Москва, )K-35, Раушская наб., д. 415

Типография, пр. Сапунова, 2 нпя пигапия, между базой одного пз транзисторов выходного каскада и коллектором промежуточного включен резистор, а к точке соединения резистора и базы выходного транзистора подключен коллектор дополнительного, змиттер которого подключен к точке соединения эмиттера и коллектора выходных транзисторов, а база дополнительного транзистора через резистор подключена к базе промежуточного транзистора.