Динамический логический элемент

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 27Я25

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Кл. 21ат, 36/18

Заявлено 24.II.1969 (№ 1320005/18-24) с присоединением заявки №

Приоритет

Опубликовано ОЗ.VII.1970. Бюллетень ¹ 22

Дата опубликования описания 15.Х.1970

Комитет по делам изобретений и открытий при Совете Министров

СССР

МПК Н 03k 19/00

УДК 681 325.65(088 8) с! щдх@т @1 ХИбжсиЯ аадноТЕ11

Авторы изобретения

Б, E. Фрадкин, В. П. Киселев и А. М. Степанцов

Заявитель

ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Динамический логический элемент может быть применен в электронных вычислительных машинах и устройствах цифровой автоматики.

В известных динамических логических элементах задержка сигнала осуществляется лиоо линией задержки (при однофазной системе импульсного питания), либо за счет заряда или разряда накопительной емкости (при многофазной системе импульсного питания). Наличие реактивностей затрудняет изготовление элементов методами современной микроэлектроники и увеличивает потребление мощности по цепи импульсного питания.

С целью задержки входного сигнала без применения реактивных элементов (расширения технологических возможностей), снижения потребляемой элементом мощности по цепи импульсного питания и увеличения коэффициентов объединения по входам «И» и «ИЛИ» (расширения логических возможностей) в предложенном элементе в качестве схемы задержки сигнала применен ждущий мультивибратор и использовано постоянное напряжение для питания входной логической сборки, имеющей на выходе эмиттерный повторитель.

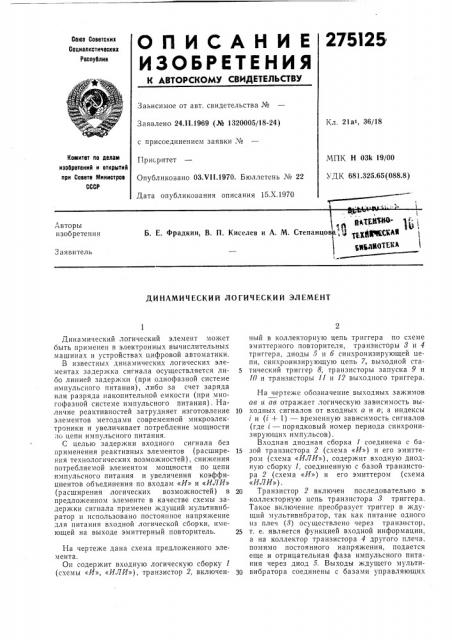

На чертеже дана схема предложенного элемента.

Он содержит входную логическую соорку 1 (схемы «И», «ИЛИ»), транзистор 2, включенный в коллекторную цепь триггера по схеме эмиттерного повторителя, транзисторы 8 и 4 триггера, диоды б и б синхронизирующей цепи, синхронизирующую цепь 7, выходной ста5 тический триггер 8, транзисторы запуска 9 и

10 и транзисторы 11 и 12 выходного триггера.

На чертеже обозначение выходных зажимов ав и ав отражает логическую зависимость вы10 ходных сигналов от входных а и в; а индексы

i и (+ 1) — временную зависимость сигналов (где i — порядковый номер периода синхронизирующих импульсов).

Входная диодная сборка 1 соединена с ба15 зой транзистора 2 (схема «И») и его эмиттером (схема «ИЛИ»), содержит входную диодную сборку 1, соединенную с базой транзистора 2 (схема «И») и его эмиттером (схема

«ИЛИ») .

20 Транзистор 2 включен последовательно в коллекторную цепь транзистора 3 триггера.

Такое включение преобразует триггер в ждущий мультивибратор, так как питание одного из плеч (8) осуществлено через транзистор, 25 т. е. является функцией входной информации, а на коллектор транзистора 4 другого плеча, помимо постоянного напряжения, подается еще и отрицательная фаза импульсного питания через диод 5. Выходы ждущего мульти30 вибратора соединены с базами управляющих

275125

Предмет изобретения аб;., „ ипи

Составитель А. И. Матвеев Редакгор Л. А. Утехина Коррсктор Л. В. Юшина

Заказ 2771(!2 Тираж 480 Подписное

Ц!-1ИИПИ Комитета по делам изобретений н открытий при Совсте Министров СССР

Москва, Я(-85, Раушскаи наб., д. 415

Типографии, пр. Сапунова, 2 транзисторов 9, 10 выходного статического тр и ггер а 8.

При низком потенциале на любом из входов (а;, в,) диодной сборки 1 транзистор 2 закрыт, и на базу транзистора 4 подается нулевое напряжение. Поэтому во время поло>кительной фазы сигнала по цепи 7 открываются транзисторы 8 и 9 (по базе).

Низкий потенциал на коллектора транзистора 9 устанавливает выходной триггер 8 в положение «0» (трапзистор 11 закрыт, транзистор 12 открыт). Таким образом, в устройствах, построенных на данных элементах, изменение входных сигналов воздействует лишь во время положительной фазы сигнала по цепи 7.

Возникновение на входах а, и в; высокого потенциала и передача его через транзистор 2 на транзистор 8 не изменяет состояния последнего, так как к этому моменту транзистор

8 уже был открьгг. Так достигается задержка в передаче логического сигнала на первую половину периода,,сщнала по цепи 7. За время следующей, - за :эгпм отрицательной фазы сигнала IIo цепи 7 ждущий мультивибратор изменяет свое состояние, т. е. открывается транзистор 4> TBIc 1431< транзистор 2 B 3To время попрежнему открыт, а на базу транзистора 8 подается отрицательный потенциал через диод 5.

Входная информация при этом оказывается переданной на ждущий мультивибратор и задержанной сщс на половину периода сигнала по цепи 7, так как состояние выходного триггера еще не изменилось. С наступлением очередной полo)Kитсльной фазы открывается транзистор 10, и выходной триггер 8 устанавливается в состояние «!».

Увеличение допустимой паразитной емкости

10 на входах схем «И» илп «ИЛИ», а следовательно, и повышение коэффициентов объединения IIo соотьетствующим входам достигается при этом в основном за, счет увеличения врсмени заряда этой емкосги.

15 I,HHàìè÷åñêèé логический элемент, содер20 жащий входнуIo логическую сборку, элемент задержки с диодной синхронизирующей цепью и выходной триггер, отличагощийсл тем, что, с целью расширения логических и технологических возможностей динамического элемента, 25 элемент задержки выполнен в виде статического триггера с включенным в одно из плеч дополнительным транзистором того же типа проводимости, база и эмиттер которого соединены с входной логической сборкой.