Делитель частоты

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 275l35

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Кл. 21ат, 36/22

Заявлено 11.XI.1968 (№ 1281464/18-24) с присоединением заявки ¹

Приоритет

Опубликовано ОЗ.VII.1970. Бюллетень № 22

Дата опубликования описания 15.Х.1970

МПК Н 03k 23/24

УДК 621.374.4(088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

А А Червяков

Заявитель

7

У

ДЕЛИТЕЛЬ ЧАСТОТЫ

Изобретение относится к измерительной и вычислительной технике в области контроля и генерации пакетов импульсов с высокой частотой заполнения.

Известно, что для формирования пакетов импульсов с точно устанавливаемым числом импульсов в пакете используются счетчиковые делители с устанавливаемым коэффициентом деления. Использованию подобных счетчиков на высоких частотах заполнения и больших количествах импульсов внутри пакета мешает задержка, которая накапливается при последовательном прохождении импульсами триггеров счетчика. Задержка тем больше, чем больше емкость счетчика, определяемая максимальным числом импульсов внутри пакета.

Эта задержка является нестабильной величиной, поэтому не может быть скомпенсирована.

Такие счетчики имеют несинхронный выход, а использование несинхронного выхода для обрыва илн коммутации конца пакета приводит к непостоянству или неточной установке числа импульсов в пакете.

Известны также счетчиковые делители с параллельным запуском и синхронным выходом.

Б одном из вариантов такого делителя параллельный запуск всех триггеров через схемы

«И» обеспечивает снижение задержки выходного импульса до суммарной величины задержек Hà всех с емах «И», что при большом количестве последних неприемлемо.

Другой вариант счетчикового делителя с параллельным запуском содержит rn тригге5 ров и m схем совпадения «И», причем каждая последующая схема «И» имеет на один управляющий вход болыпе, чем предыдущая. Такой делитель обладает синхронным выходом и задержкой, равной задержке на одной схеме

10 «И». Недостатком данного счетчика является неоднотипность схем «И», их сложность, невозможность практической реализации схем

«И» с большим количеством входов, жесткие требования к нагрузочной способности тригге15 ров (например, первый триггер должен управлять пг входами, второй — тгг — 1 входами и т, д.), а значит и невозможность реализации на данном принципе счетчика с большой емкостью (ббльшим числом триггеров).

20 Кроме того, общим недостатком счетчиковых делителей являются жесткие требования к входному генератору импульсов, который в обоих случаях нагружен на несколько параллельно соединенных триггеров.

25 Предложенный делитель частоты с устанавливаемым коэффициентом деления, в котором использован *известный способ установки коэффициента деления путем записи в счетчик дополнительного числа установочным импуль30 сом от генератора установки, отличается от

275135

Воин извсстных тем, чTо в нем выходы т-й и (и— — 1)-й триггерных ячеек со счетными входами подсоединены к и-й двухвходовой схеме «И», выход которой соединен с одним из входов

im — 1)-й схемы «И», на второй вход которой 5 подсоединен выход с (и — 2) -й триггерной ячейки и т. д.; выходной импульс делителя, которым является и-й импульс входной последовательности, снимается непосредственно с

1-й схемы «И», подготовленной к его приходу 10 (12 — 1) -ым входным импульсом. Задержка выходного импульса равна задержке на одном

-элементе «И», Это позволяет свести задержку выходного импульса до величины задержки одной схемы 15

«И»; упростить все схемы «И»; снизить требования по нагрузке к триггерам и задающему геператору и обеспечить работу счетчикового делителя при любом количестве использованных в нем триггеров. 20

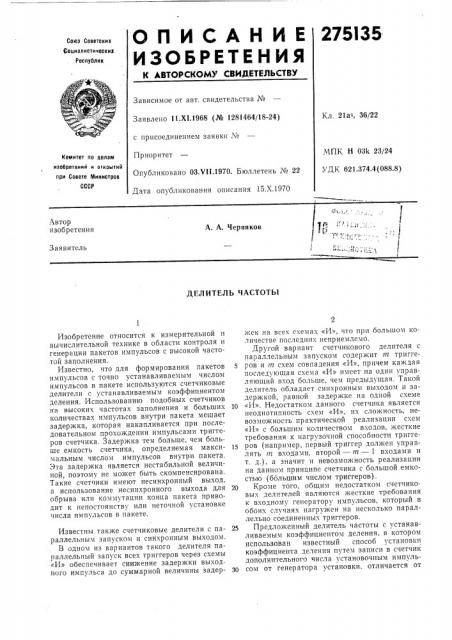

На фиг. 1 показана схема делителя частоты, состоящая из триггеров 1,— 1, двухвходовых схем совпадения «И» 2> — 2, генератора начальной установки 8 и переключателей начальной установки 4; на фиг. 2 показаны 25 эпюры двоичного четырехразрядного делителя.

Эпюры для любого числа последовательно соединенных триггеров могут быть построены аналогично.

Схемы «И» выделяют сигнал (потенциал) 30 совпадения при наличии «единичного» потенциала на обоих входах. Предположим, необходимо поделить входную последовательность импульсов на 10 при использовании четырехразрядного делителя с емкостью, равной 16, Для этого необходимо с помощью генератора установки 8 записать в делитель число б (пунктирная линия на эпюрах). Четвертая схема «И» выдает сигнал совпадения после

6-го входного импульса (на эпюрах 12-й), третья схема «И» — после 8-ro (14-го), вторая — после 9-го (15-го). Таким образом, к приходу 10-го (1б-го) импульса первая схема

«И» будет подготовлена по одному из входов входной !О-й импульс, пройдя через первую схему «И», поступает на выход и на генератор установки 8. При этом длина делителя (число триггеров) не имеет значения, так как схема

«И» подготавливается в направлении от конца делителя к началу.

Предмет изобретения

Делитель частоты с синхронным выходом, содержащий двоичный счетчик íà m триггерах и и межкаскадных двухвходовых схем

«И», отличающийся тем, что, с целью его упрощения и повышения надежности, в нем выходы т-го и (т — 1)-го триггеров соединены со входами т-й схемы «И», выход которой соединен с одним из входов (т — 1)-й схемы «И», ко второму входу которой подключен выход (m — 2)-го триггера и т. д.; выход первой схемы «И», ко входам которой подключены выход второй схемы «И» и источник входных импульсов, служит выходом делителя.

2 3 Ч 5 6 7 8 9 10 71 12 13 1Ч 75 16

„7

Фиг 2

Составитель В. Е. Валюженич Редактор Л. А. Утехина Корректор О. Б. Тюрина

Заказ 2771,18 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 7К-35, Раушская наб., д. 415

Типография, пр. Сапунова, 2