Устройство для деления чисел с естественным расположением запятой

Иллюстрации

Показать всеРеферат

276520

Q АНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Кл, 42шз, 7/52

Заявлено 27.III.1969 (¹ 1327541/18-24) с присоединением заявки

Приоритет

ЧПК G OGf 7/52

УДК 681.325.58 (088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Опубликовано 14Х11.1970. Бюллетень № 23

Дата опубликования описания З.XI.1970

Авторы изобретения Г. И. Корниенко, А. С. Одинокий, В. Г. Назаренко и А. С. Сапожников

Институт кибернетики АН Украинской ССР

Заявитель

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ С ЕСТЕСТВЕННЫМ

РАСПОЛО,EHHEM ЗАПЯТОЙ

Изобретение относится к области вычислительной техники и может быть использовано при построении вычислительных машин.

Известны устройства для деления чисел с естественным расположением запятой, содержащие блок операционных регистров, кажды1 разряд которых содер>кит дополнительный эле мент памяти для хранения запятой, сумматор, блок сдвигов и блок управления.

Предложенное устройство отличается от известного тем, что содержит блок анализа совпадения запятых и блок сравнеш|я разрядов, первые входы которых соединены с выходами блока операционных регистров, вторые входы соединены с выходами блока управления, а выходы — с входами блока управления.

Это позволяет повысить быстродействие устройства.

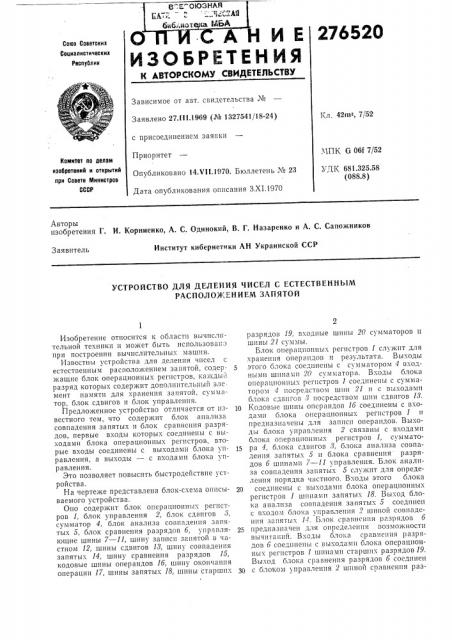

На чертеже представлена блок-c eìà описываемого устройства.

Опо содер>кит блок операционных регистров 1, блок управления 2, блок сдвигов 8, сумматор 4, блок анализа совпадения запятых 5, блок сравнения разрядов 6, управляющие шины 7 — 11, шину записи запятой в частном 12, шины сдвигов 18, шину совпадения запяты.; 14, шину сравнения разрядов 15, кодовые шины операндов 16, шину окончания операции 17, шины запятых 18, шины старших разрядов 19, входные шины 20 сумматоров и шины 21 суммы.

Блок операционных регпстпов 1 cJIA?KILT pля хранешгя операндов и результата. Выходы

5 это" î блока соединены с сумматором 4 входными шинами 20 сумматора. Входы блока операционных регистров 1 соединены с сумматором 4 посредством шин 21 и с выходами блока сдвигов 8 по-редством шин сдвигов 18.

1Q Кодовые шины операндов 16 соединены с входами блока операционных регистров 1 и предназначены для записи операндов. Выходы блока управления 2 связаны с входами блока операционных регистров 1, суммато15 ра 4, блока сдвигов 8, блока анализа совпадения запятых 5 и блока сравнения разрядов 6 шинами 7 — 11 управления. Блок анализа совпадения запятых 5 служит для определения порядка частного. Входы этого блока

20 соединены с выходами блока операционных регистров 1 шннамп запятых 18. Выход блока анализа совпадения запятых 5 соединен с входом блока управления 2 пшной совпадения 32HsIT51. . 1- . Б чок cp3BIic iliIH цазпядов 6

25 предназначен для определения возможности

a ai i H T é ii i i É. Входы o:i o i a с р а в и с и и я р а з р ядов 6 соединены с выходами блока операционных регистров 1 шпнамп старших разрядов 19.

Выход блока сравнения разрядов 6 соединен

30 с блоком управления 2 шиной сравнения раз276520

60 рядов 15. Выход блока управления 2 соединен с входом блока операционных регистров 1 шиной записи запятой в частном 12. Выход блока операционных регистров 1 связан с входом блока управления 2 шиной окончания операции 17.

Устройство работает следующим образом.

Оно реализует способ деления чисел с естественным расположением запятой, сущность которого состоит в следующем: запятая в частном представляется по совпадению запятых в делимом и делителе. Перед началом операции деления операнды приводятся к виду, когда запятые их находятся в одноименных разрядах. Затем производится сдвиг делителя до тех пор, пока старший разряд его не станет больше старшего разряда делимого, после чего сдвигается делимое. При каждом сдвиге его в частном получается очередной верный разряд. Запятая в частном записывается по совпадению запятых в делимом и делителе, которое наступает в результате сдвигов.

Блок управления 2 вырабатывает команду разрешения записи операндов, поступающую по шинам 7 в блок операционных регистров 1. Запись производится посредством кодовых шин операндов 1б. В каждом разряде памяти или оперативных регистров для запятой отводится один бит.

Блок управления 2 посредством шин 9 дает команду начала сдвигов делителя; Сигнал сдвигов поступает с выхода блоков сдвигов 8 на вход блока операционных регистров 1 по шине сдвигов 18. Одновременно блок управления 2 вырабатывает сигнал, разрешающий сравнение старших разрядов, который поступает по шине управления 11 на вход блока сравнения разрядов б. Старшие разряды попадают на блок сравнения разрядов б по шинам старших разрядов 19. Когда старший разряд делителя станет больше старшего разряда делимого, блок сравнения разрядов б по шине сравнения разрядов 15 посылает сигнал прекращения сдвигов на вход блока управления 2, Команда прекращения сдвигов делителя поступает из блока управления 2 в блок сдвигов 8 по шине 9.

Далее блок управления 2 вырабатывает команду сдвига делимого на один разряд. Сигнал сдвига делимого поступает из блока сдвигов 8 по шинам сдвигов 18 на вход блока операционных регистров 1. В этот момент возбуждена шина 10, по которой поступает сигнал на вход блока анализа совпадения запятых 5, разрешающий работу этого блока. Запятые попадают в блок анализа совпадения запятых 5 по шинам запятых 18. Если запятые делимого и делителя находятся в одноименных разрядах, то блок анализа совпадения запятых 5 посылает сигнал в блок уп5

45 равления 2 посредством шины совпадения запятых 14. По этому сигналу блок управления 2 вырабатывает команду записи запятой в частном, поступающую на вход блока операционных регистров 1 по шине записи запятой в частном 12. Верные разряды и запятая в частном записываются в младший разряд регистра, а затем сдвигаются вместе с делимым.

Если запятая в частном проставлена, то по сигналу блока управления 2 (отсутствие возбуждения шины 10) блок анализа совпадения запятых 5 выключается и не участвует в дальнейшей работе устройства.

Если после сдвига делимого на один раз. ряд его старший разряд станет больше старшего разряда делителя, что определяется блоком сравнения разрядов б, то по шине сравнения разрядов 15 в блок управления 2 поступает соответствующий сигнал. По этому сигналу блок управления 2 вырабатывает команду разрешения вычитаний делителя из делимого, которая поступает на вход сумматора 4 по шинам 8. Операнды поступают в сумматор 4 по входным шинам 20, а разность поступает в блок операционных регистров 1 по шинам 21. По команде блока управления 2, поступающей по шинам 7 на вход блока операционных регистров 1, происходит образование верного старшего разряда частного. Если после вычитания старший разряд делимого станет меньше старшего разряда делителя, что определяется блоком сравнения разрядов б, то блок управления 2 вырабатывает команду сдвига делимого и частного на один разряд.

Если после сдвига делимого старший разряд его меньше старшего разряда делителя, то происходит сдвиг делимого и частного на один разряд, а верным разрядом в этом случае будет нуль.

Описанный процесс происходит до тех пор, пока значащая цифра или запятая частного не окажется в старшем разряде регистра.

Сигнал об этом поступает в блок управления 2 по шине окончания операции 17.

Предмет изобретения

Устройство для деления чисел с естественным расположением запятой, содержащее блок операционных регистров, каждый разряд которых содержит дополнительный элемент памяти для хранения запятой, сумматор, блок сдвигов и блок управления, отличающееся тем, что, с целью:повышения быстродействия, оно содержит блок анализа совпадения запятых и блок сравнения разрядов, первые входы упомянутых блоков соединены с выходами блока операционных регистров, вторые входы соединены с выходами блока управления, а выходы — со входами блока управления.

276520

Составитель И. Долгушева

Редактор Е. В. Семанова Техред 3. Н. Тараненко Корректор О. С. Зайцева

Заказ 2902/8 Тираж 480 Подписное

IIHHHIIII Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, K-35, Раушская иаб., д. 4/5

Типография, пр. Сапунова, 2