Регистр цифрового автоматического прибора с поразрядным взвешиванием

Иллюстрации

Показать всеРеферат

2770l9

ОП И САН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 04.III.1969 (№ 1324179/18-24) с присоединением заявки №

Приоритет

Опубликовано 22.VII.1970. Бюллетень № 24

Дата опубликования описания З.XI.1970

Кл. 21а1, 36/22

МПК Н 031 13Ю0

УДК 621.374.32(088.8) Комитет па делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

Л. Н. Соколов

Им

Институт автоматики и телемеханики (технической киберн УЙ

Заявитель

РЕГИСТР ЦИФРОВОГО АВТОМАТИЧЕСКОГО ПРИБОРА

С ПОРАЗРЯДНЫМ ВЗВЕШИВАНИЕМ

Изобретение относится к области электроизмерительной техники, автоматики и телемеханики и может быть использовано в качестве устройства, совмещающего в себе функции регистра памяти и распределителя импульсов в цифровых автоматических приборах и кодирующих преобразователях, работающих по методу поразрядного взвешивания.

В известных цифровых автоматических приборах и кодирующих преобразователях распределение импульсов и промежуточное запоминание осуществляются двумя самостоятельными однофункциональными устройствами — распределителем импульсов и регистром. Распределители импульсов выполняются обычно на основе различных схем счетчиков или на основе комбинации счетчиков и дешифраторов.

При реализации последнего варианта заметно сокращается число разрядов счетчика, а следовательно, и число активных элементов (транзисторов), упрощается схема и повышается надежность распределительного устройства.

Дальнейшим шагом к упрощению распределительного устройства и частичной передаче

его функции распределения импульсов регистру является изобретение по авт. св. № 216130.

В этом изобретении распределитель импульсов имеет число разрядов (триггеров), равное числу декад регистра и осуществляет подекадное распределение импульсов, внутрпдекадное же распределение импульсов выполняется регистром, что значительно упрощает распределительное устройство. Кроме того, в этом изобретении сделана попытка превращения регистра в многофункциональное устрой10 ство, осуществляющее, кроме промежуточного запоминания, также частичное распределение импульсов. Но поскольку регистр выполняет лишь частичное распределение импульсов (внутри декады), то он не является полностью

1 независимым устройством и его функционирование невозможно без распределителя, хотя и упрощенного. Наличие же в приборе или в кодпрующем преобразователе двух устройств — распределителя импульсов и регист20 ра — приводит к значительным схемным усложнениям и детальной избыточности. Наличие же активных элементов (транзисторов) в распределителе импульсов снижает его надежность и помехоустойчивость, а следова25 тельно, и всего прибора в целом.

Целью изобретения является упрощение устройства (устранение распределителя) и повышение его надежности.

Эта цель достигается соответствующим

30 подключением схем совпадения (диодно-ем277019

15 костных ключей) и введением в регистр диодных схем «ИЛИ». Один пз двух погепцпальных входов схемы совпадения, относящейся к единичному входу кахкдого триггеpa, кроме первого, через разделительный диод подсоединен к диодпой схеме «ИЛИ», один из входов которой соединяется с единичным выходом данного триггера, а второй — с выходом диодной схемы «ИЛИ» последующего триггера. Другой потенциальный вход схемы совпадения, стоящей на единичном входе каждого триггера, соединен с нулевым выходом предыдущего триггера, а импульсный вход — с шиной тактовых импульсов.

Цепочка, сформированная последовательным соединением диодных схем «ИЛИ», может служить одновременно цепью сброса триггеров регистра в исходное состояние.

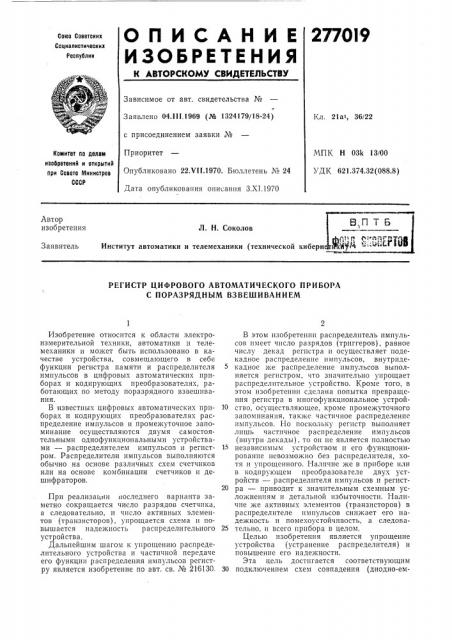

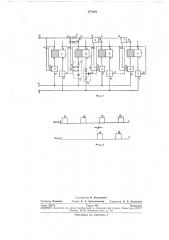

На фиг. 1 приведена блок-схема одной декады регистра; на фиг. 2 — временная диаграмма импульсов на шине тактовых импульсов и перекомпенсации.

Описываемый регистр может состоять из и-го числа триггеров (в данном случае n= 4, что составляет декаду регистра) и включает в себя триггеры 1«... l„со схемами совпадения 2 на их единичных входах «1» и схемами совпадения 8 на нулевых входах «О», разделительные диоды 4, диодпые схемы 5 и 7

«ИЛИ», шины 8 тактовых импульсов и шины 9 перекомпенсации.

Потенциальные входы 10 схем совпадения 8 триггеров 1«... 1, и импульсный вход 11 схемы 8 совпадения триггера 1«подсоединены к шине 9 перекомпенсации. Импульсный вход 11 схем совпадения 8 подключен к выходу «О» того триггера, который следует за триггером, имеющим данную схему совпадения на его входе «О». Такое включение схем 8 совпадения обеспечивает сброс предыдущего триггера после срабатывания последующего при наличии разрешающего потенциала на шине 9 перекомпенсации. Потенциальный вход 10 схемы 8 совпадения триггера l„соединен с выходом «О» своего триггера.

Схемы 2 совпадения, отосящиеся к входам

«1» триггеров, своими импульсными входами 12 подсоединены к шине 8 такговых импульсов. Потенциальный вход 18 схем 2 совпадения соединен с выходом «0» того триггера, который предшествует триггеру, имеющему данную схему совпадения на его входе

«1», а потенциальный вход 18 схемы 2 совпадения триггера 1, подсоединен к выходу «1» своего триггера. Другой потенциальный вход

14 схемы 2 совпадения триггеров 1>... 1 „ через разделительный диод 4 соединен с выходом 15 соответствующей диодной схемы 5, 6 и 7 «ИЛИ», один из входов которой соединен с выходом «1» триггера, имеющего на своем входе «1» данную схему 2 совпадения, а другой вход соединен с выходом 15 диодной схемы «ИЛИ», относящейся к последующему триггеру.

Исключение составляет потенциальный вход 14 схемы 2 совпадения триггера 1«, который через диод 4 соединен с выходом 15 диодной схемы 5 «ИЛИ» триггера 1>. Разделительный диод 4 препятствует появлению отрицательного потенциала с выхода «О» предшествующего триггера (связь через элементы схемы 2 совпадения) на выходе 15 диодной схемы «ИЛИ», относящейся к последующему триггеру.

Один из входов 16 диодных схем 5 — 7

«ИЛИ» соединен с выходом «1» соотвегствующего триггера 1,.13 и 1„, а другой вход17 каждой диодной схемы «ИЛИ» — с выходом 15 последующей диодпой схемь««ИЛИ».

В результате образуется цепь последовательно соединенных диодных схем «ИЛИ». Эта цепь обеспечивает подачу запрещенного отрицательного потенциала с выхода «1» каждого последующего триггера, после его опрокидывания, на потенциальный вход 14 схег«ы 2 совпадения этого триггера и схем 2 совпадения предыдущих триггеров, которые были сброшены в исходное состояние (дважды опрокинуты) . Кроме того, цепь диодных схем 5—

7 «ИЛИ» при подключении в клемме 18 нулевого потенциала может играть роль цепи сброса триггеров в исходное положение.

Предлагаемый регистр работает следующим образом.

В исходном положении все триггеры 1«... 1„ находятся в таком состоянии, что на их выходе «О» находится отрицательный потенциал.

Этот запрещающий потенциал с выхода «О» каждого предыдущего триггера подается на потенциальный вход 18 схемы 2 совпадения последующего триггера. На потенциальный же вход 18 схемы 2 совпадения триггера 1, заводится нулевой (разрешающий) потенциал с выхода «1» своего триггера. На другом потенциальном входе 14 схем 2 совпадения также находится разрешающий потенциал.

Предположим, что регистр должен запомнить величину, равную пяти условным единицам (у. е.), набранную по двоично-десятичному коду 4221.

Первый импульс на шине 8 тактовых импульсов (на фиг. 2 он условно обозчачен е,) поступает на вход 12 схемы 2 совпадения триггера 1«, дифференциру.ется и опрокидывает триггер. Поскольку включение триггера 1« соответствует запо« «инанию «4», то на шине 9 перекомпенсации пе появляется разрешающий потенциал и триггер 1«остается включенным. С выхода «1» триггера 1«на вход 18 его схемы 2 совпадения подается запрещающий потенциал, а с выхода «О» на потенциальный вход 18 схемы совпадения последующего триггера 1 — разрешающей потенциал. В результате вторым импульсом на шине 8 (е на фиг. 2) триггер lq будег опрокинут и с его выхода «1» через вход 16 диодной схемы 5 «ИЛИ» и разделительный диод 4 будет подан запрещающий потенциал на вход 14 его схемы 2 совпадения, а с выхода «0»вЂ”

277019 разрешающий потенциал на вход И схемы 2 совпадения триггера I>.

Включение триггера 1> соответствует запоминанию двух у. е., а суммарный результат после включения триггеров 1, и 1 составит

4+2=6 у. е., что превышает заданную величину в пять у. е. и указывает па необходимость возврата триггсра 12 в исходное положение. Для этого на шипу 9 перекомпепсации подается положительный импульс (е, на фиг. 2), который попадает на потенциальный вход 10 схем 8 совпадения и подготавливает триггер I> к повторному срабатыванию. Это происходит в момент включения триггера I» от импульса (е;, на фпг. 2), который сдшшут на время Л1 относительно е,, благодаря воздействию с его выхода «О» положительного перепада напряжения на импульсный вход 11 схемы 8 совпадения триггера 1 . После вкл!очения триггера 1 с его выхода «1» подается запрещающий потенциал на вход 14 его схемы 2 совпадения через вход 16 диодной схемы 6 «ИЛИ» и разделительный диод 4, и на вход 14 схемы 2 совпадения триггера 1 через вход 16 диодной схемы б «ИЛИ», выход 15 которой соединен со входом 17 предыдущей диодной схемы 5 «ИЛИ», и разделительный диод 4.

Срабатывание триггера lя, так же как и триггера 12, соответствует запоминапп;о двух у. е., следовательно, он должен быгь возвращен в исходное состояние. Это I.роизойдет в момент опрокидывания последующего триггера I„от воздействия положител= íîãî импульса (е1 на фиг. 2) с шины 8 тактовых импульсов.

Предварительно на шине 9 с опережением на время At появляется импульс е2, что подготавливает повторное срабатывание триггера 13. После опрокидывания триггера l „с его выхода «1», запрещающий потенциал поступает на вход 14 его схемы 2 совпадения через диодную схему «ИЛИ» 7 и диод 4, и на вход

14 схем совпадения 2 триггеров 1> и 1 соответственно через диодные схемы 7 и б

«ИЛИ» и разделительный диод 4 и диодные схемы «ИЛИ» 5 — 7 и диод 4.

Крометого, после срабатывания триггераl„ накладывается запрет е!я поступление пОлОж!Пгельпых импульсов на шину 8. Запрет накладывается с помощью вспомогательного триггера (не показан), который срабатывает под воздействием положительного перепада напряжения, сгп!маемого с в входа «0» триггера I„. Триггер 1, включение которого соотгетствует запоминанию одной у. е., не воз10 вращается в исходное состояние (на шине 9 пе появляется положительный импульс), IIOскольку включением триггеров I„и I> выполнено условие запоминания пяти у. е. по коду 4221.

15 При ЗЯПОминанип четырех у. е. TpIIr! ep 1 возвратился бы в исходное состояние под воздействием положительного импульса с шины 9 па пмпульсчый вход 11 его схемы 8 совпадения, на потенциальном входе 10 которого

20 присутствует разрешающий потенциал.

Триггеры регистра прпьодятся в исходное голожение путем подачи импульса сброса на клемму 18, который через цепочку дподных схем 5 — 7 «!.1ЛИ» воздействует на выход «1»

25 триггеров 1> 1; и I„. Триггер 1, сбрасывается обычным способом.

Предмет изобретения

Регистр цифрового автоматического прибо30 ра с поразрядным взвешиванием, выполненный на п триггерах со схемами совпадения на их входах и имеющий шины тактовых импульсов и перекомпенсации, оглича!Ощийся тем, что, с целью упрощения устройства и по35 вышения его надежности, он содержит (п — 1) дподпых схем «ИЛИ», причем од и! из двух потенциальных входов схемы совпадения, относящийся к единичному входу каждого триггера, кроме первого, через разделитель40 ный диод соединен с выходом диодной схемы

«ИЛИ», один вход которой соединен с единичным выходом данного триггера, другой— с выходом диодной схемы «ИЛИ», относящейся к последующему триггеру, другой потен45 цпальный вход схемы совпадения соединен с нулевым выходом предыдущего триггера, а ее импульсный вход — с шиной тактовых импульсов.

277019

Фиг.!

Шина

Фиг.2

Составитель В. Валюженич

Редактор Полещук

Техред А. А. Камышникова !(орректор Л, Б. Бадылама

Типография, пр. Сапунова, 2

Заказ 3087/6 Тираж 480 Подписное

ЦНИИПИ 1(омитета по делам изобретений и открытий при Совете Министров CCCP

Москва, Ж-З5, Раушская наб., д. 4/5