Логарифмический преобразователь напряжения в двоичный код

Иллюстрации

Показать всеРеферат

ПАТЕНТНО-ТЕХНИЧЕСКАЯ бибдиотана МБА

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сова Советских

Социалистических

Реслублик

277418

Зависимое от авт. свидетельства ¹

Заявлено 19.11.1969 (¹ 1315471/18-24) 1:,л, 42m>, 3/00 с присоединением заявки ¹

МПК Н 03k 13/175

Н 031 13/20

G 06j 3/00

УДК 681.325 (088.8) Приоритет комитет по делам изаоретений и открытий лри Совете Министров

СССР

Опубликовано 22.I/11.1970. Бюллетень ¹ 24

Дата опубликования описания З.XI.1970

Автор изобретения

И. М. Благовещенский

Заявитель

ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯ)КЕНИЯ

В ДВОИЧНЫЙ КОД

U„, (U,„(U,, Известны логарифмические преобразователи напряжения в двоичный код с промежуточным преобразованием напряжения во временной интервал.

Недостаток известных преобразователей заключается в товт, что максимальное время преобразования определяется числом разрядов кода результата преобразования и частотой,импульсов счета и не может быть уменьшено ниже определенного уровня, устанаьливаемого из технических соображений. Повышение частоты импульсов счета для ускорения преобразования влечет за собой уменьшение постоянной времени разряда конденсатор» схемы формирования экспоненциально спадающего напряжения, что, в свою очередь, приводит к резкому росту динамических погрешностей преобразования.

Предложенный преобразователь отличается тем, что для ускорения преобразования в -V ==

= 2" раз к выходу схемы формирования экспоненциально спадающего напряжения подключено N схем сравнения напряжений, выходы которых через одну схему сборки соединены со входом триггера управления. Выходы схем сравнения, кроме первой, через другую схему сборки соединены со входом ключа разряда конденсатора схемы формирования экспоненциально спадающего напряжения, а через остальные схемы сборки — со входа мп триггеров регистра старших разрядов кода.

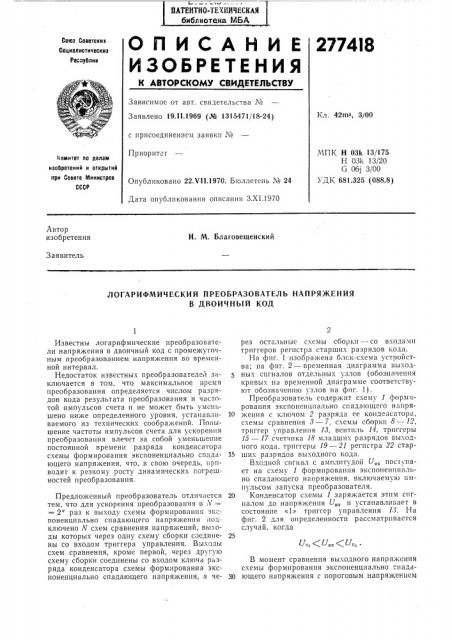

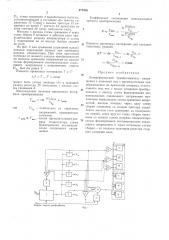

На фпг. 1 изображена блек-схема устройства; па фпг. 2 — временная диаграмма выходных сигналов отдельных узлов (обозначения кривых IIH временной диаграмме соответствуют обозначешпо узлов на фиг. 1).

Преобразователь содержит схему 1 формирования экспоиенцпально спадающего напря10 жения с ключом 2 разряда ее конде«сатора, схемы сравнения 8 — 7, схемы сборки 8 — 12, триггер управления 18, вентиль 14, триггеры

15 — 17 счетчика 18 младших разрядов выходного кода, триггеры 19 — 21 регпсгра 22 стар15 ших разрядов выходного кода.

Входной сигнал с амплитудой U посгтпает на схему 1 формирования экспоненцнально спадающего напряжения, включаемую импульсом запуска преобразователя.

20 Конденсатор схемы 1 заряжается этим сигналом до напряжения U,„è устанавливает в состояние «1» триггер управления И. На фиг. 2 для определенности рассматривается случай, когда

В момент сравнения выходного напряжения схемы формирования экспоненциально спада30 ющего напряжения с пороговым напряжением

277418 (ax)max у Тиара

Т,х (вх)пах

U п

Uux — 1п п п

ЛT =-In

= -.In = const. п(р, ЛТ = Т вЂ” Т = const где

I

I

I

I !

1

Импульс эаауана ареа азааателя айаг 1

U„, схема сравнения 4 вырабатывает импульс. устанавливающий в состояние «0» триггер управления 18. Строб с выхода триггера 18 открывает на время Т вентиль 14, пропуская па вход счетчика 24 пачку импульсов счета.

Импульс с выхода схемы сравнения 4 через схему сборки 8 приводит в действие клк>ч принудительного разряда конденсатора а схемы

1, напряжение на ее выходе быстро спадает до нуля.

На фиг. 2 для сравнения шгрпховой кривой показан переходный процесс при свободном разряде конденсатора. При этом временной интервал от. момента запуска преобразователя до момента сравнения напряжения на выходе схемы формирования экспонепциально спадающего напряжения с напряжением порога

U,, был бы равен Т.

Разность временных интервалов Т и Т может быть учтена записью «1» в младший разряд регистра 25 импульсом с выхода схемы сравнения 4.

Максимальное значение временного интервала преобразования ф

U„— наибольшее из пороговых напряжений, превышенных сигналом.

t р„р << Т „— время принудительного разряда конденсатора схемы формирования экспоненцпально спадающего напряжения.

1(оэффициент сокращения максимальногО времени преобразования

Разность временных интервалов для соседних пороговых уровней

Предмет изобретения

Логарифмический преобразователь напряжения в двоичный код с промежуточным преобразованием во временной интервал, отличающийся тем, что, с целью ускорения преобра25 зованпя, к выходу схемы формирования экспопепциально спадающего напряжения подключены параллельно схемы сравнения напряжений, выходы которых через одну схему

30 сборки соединены со входом триггера управления, выходы схем сравнения, за исключением первой, через другую схему сборки соединены со входом ключа разряда конденсатора схемы формирования экспоненциально спадающего напряжения и через остальные схемы сборки — со входами триггеров регистра старших разрядов кода.

2774:8

Вкодноо сигал

Venynос ското

Фог. 2

Редактор Б. Б. Федотов

Заказ 3044/12 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, 5К-35, Раушская наб., д 4!5

Типография, пр. Сапунова, 2 омпуло .толусюа

Составитель Крылова

Техред Л. Я. Левина Корректор T. А. Абрамова