Патент ссср 278729

Иллюстрации

Показать всеРеферат

278729

СхПИСАНИЕ

ИЗОБРЕТЕ Н И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республин

Зависимое от авт. свидетельства №вЂ”

Кл, 21а, 13/01

Заявлено 08.V11.1969 (№ 1345339!18-24) с II!pисоединением заявки №вЂ”

Приоритет —Опубликовано 21 Vill.1970. Бюллстспь № 26

Дата QIT>, o. III QBBIIHII списания 25.Х1.1970.

Комитет по цепам изобретений и открытий при Совете Министров

СССР > > П К Н 04/ 7/02

"ДК 681.326.35(088.8) 9 Ь.ММ9агЛ

Й .ТИТ59т;".у чд >ядр вв

Й)::Б.|йб 1 Д i

Лвтор изоб>ретсния

Л. Д. Кислюк

Заявитель

РЕГЕНЕРЛТОР ДВОИт1НЪ|Х СИМВОЛОВ

Изобретение относится к системам передачи данных.

Известны регенераторы двоичных символов, содержащие опорный генератор, делитель частоты, устройство управления коэффициентом деления, узел усреднения, фазовый дискриминатор и интегратоп со сбросом для выделения символов. В известных устройстВах на фазовый дискриминатор подаются импульсы фронтов, полученные в результате дифференцирования принимаемого сигнала.

При наличии искажений принимаемого сигнала типа дробле>пш на фазовый дискриминатор за время периода Т колебаний подстрапваемого генератора (T-длительность элементарной посылки) поступает несколько импульсов фронтов.

В известных устройствах фазовое рассогласование измеряется относительно 1-го за период Т импульса фронта, а потому при наличии дроблений точность синхронизации резко падает, благода ря чему увеличивается число неверно при IAThlx символов.

Для уменьшения числа неверно приняты.: символов прн наличии дроблений предлагается фазовьш дискриминатор выполнить в виде счетчика разности, вход которого соединен с двумя ячейками совпадения, псдкл>оченпымп к двум потенциальным вы_#_îäaм делителя частоты и выходу опорного генератора, а параллельные выходы счетчика разности подключены через ячейки опроса, связанные с импульсным в >ходом делителя, к преобразователю двоичного кода в чпслопмпульсный код, BBIход которого соединен со входами сложения и вычитания узла усред»ени» через две ячейки коммутации, соединенные с выходамп триггера знака. Прп этом выход единиц старшего разряда счетчика интегратора и выход

IC> нулей старшего разряда с» ò÷ø а разности подключены через сумматор Tio модул>о два н ячейку опроса к раздельному входу тршггера знака.

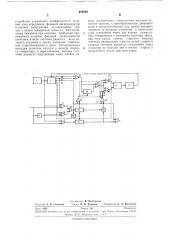

На чертеже приведена функциональпал д5 схема устройства.

Коррекционное устройство, состоящее пз опорного генератора 1, делителя частоты 2 (с коэффициентом деления !V), устройства управления коэффициентом деления >, узла усреднения 4 и фазового дискриминатора:>, работает известных> cliocoooll. Talc>Kc пз>к cTc .Il цифровой интегратор, выполненный на счст LiIIKB 6 (с коэффициентом деленил Л ), ячейках совпадения «И» 7 и 8. С помощью лчейкн

icoBI!azeIIIr» «И» 7 осуществляется стрoc»lpc>25 ванне п ринимаемого сигнала импульсамп с выхода спорного генератора.

Ячейка совпадения «И» 8 по1cop:el!I!c >» к выходу едишщ Tp!I!!cpa старшего разряда

3р счегчика 6. С импульсного выхо Ia 9 дслпгслл

17872I) частоты .на ячейку совпадения «И» 8 подается в момент /,,импульс опроса, которыи, кроме того, с некоторой задержкой в линии задержки 10 проходит на вход установки счетчика б в нулевое (состояние. При синфазности импульса опроса и границ принимаемых посылок и при отсутствии искажения посылок в момент / на выходе единиц всех триггеров счетчика б будуг находиться уровни

«О» (при приходе посылки О) или уровни «1» (при приходе посылки 1). Таким образом, выход счетчика б в момент опроса соответствует значению принимаемого символа.

Фазовый дискриминатор работает следующим образом.

Первая половина принимаемой посылки стробируется импульсами с выхода опорного генератора 1 в ячейке совпадения «И» 11, для чего на нее поступает сигнал уровня «1» с выхода 12 прямой фазы триггера старшего разряда демиреля частоты во время пе|рвой половины IllocIIJIKII, вторая половина принимаемой посылЙи стробируеПся (после инвертирования в инвесторе 13) в ячейке совпадения

«И» 14, на которую поступает сигнал уровня

«1» с выхода 15 обратной фазы триггера старшего разряда делителя частоты во .время второй lIIoëo âèíû посылки. Выхо,ды ячеек совпадения «И» 11 и 14 через ячейку «ИЛИ» 1б подключены к счетному входу счетчика 17 разности (с коэффициентом деления N), кото вый обнуляется .импульсом с линии задержки.

Как при приеме символа «О», так и символа

1» прп полной спнфазностп импульсов о)проса и границ принимаемыx посылок и QTIcóòñòâèè ,искажений посылок к моменту / „в счетчи

N ке 17 будет записано число Л=

Е сли импульс опроса отстает от границы посылки íà вовремя т, то в счетчике 17 к моN менту /„ будет находиться число Л= -- + а; у

T т где a =-«)=1 прп приеме посылки «1» и и;=-и, = — 1 Illpп приеме посылки «О», Прп опережении момента i „относительно границы посылки величина Л определяется этим же соотношением при учете того, что т О. Сигнал ошибки 6 при .рассогласованпп на время т ðàN псн отклонению величины Л от значения Л=--.;

N т.с. 6=aiTT . Процедура нахожчения величины сигнала рассогласования,,подаваемого на узел усреднения, распадается на две части— нахождение абсолютного значения рассогласо ва пя и нахождение знака рассогласования.

Для формирования абсолютного значения рассогласования в виде пачки из (6) импульсов служит счетчик 18 и ячейки совпадения «И»

19 — 21. В момент t, величина Л переписывается в параллельном коде из счетчика 17 через ячейки со впадения «И» 19 в счетчик 18 (с коэф рициентом деления N).

В течение первой половины принимаемой

lllocbIJIKи на выходе ячейки совпадения «И» 21, N фо рм ируется пачка из, импульсов опорного генератора, которая поступает на счетный вход счетчика 18 и на ячейку совпадения «И»

20. Другой вход ячейки совпадения «И» 20 связан с выходом, нуля триггера последнего разряда, счетчика 18. Если 6 О, то во время поступления с ячейки совпадения «И» 21 первых (6) импульсов ячейка совпаде)нация «И» 20 будет открыта сигналом счетчи ка 18, Ho IlocN ле набора в счетчике 18 числа — — ячейка совпадения «И» 20 окажется блокированной. Таким образом,;на выход ячейки совпадения

«И» 20 пройдут только первые (6) импульсов пачки с ячейки совпадения «И» 21. Если 6>0, то во время поступления с ячейки совпадения

N лО

«И» 20 первых —, — 6 импульсов эта ячейка

2 будет блокирована и откроется только после перехода счетчика 18 через нулевое состояние.

Таким образом, на выход ячейки совпадения

«И» 20 пройдут последние 6 импульсов пачки с ячейки со впадения «И» 21. Для формования знака рассогласования служат сумматор по модулю два 22, ячейка «И» 23 и триггер знака 24. Нахождение знака рассогласования основывается на том же факте, что знак вели30 чины 6 „. не зависит от значения принимаемой посылки, а однозначно определяется знаком временного рассогласования т, так как

1! ., И N

=а ., .— .. ". В таблице приведены четыре !

35 возможных варианта соотношения знаков 6 и а, соответствующие им значения выхода «О» триггера старшего разряда счетчика 17 (Ь„), выхода «1» триггера старшего разряда счетчика б (в) ) и получающегося в результате суммирования значения bi — b„+b, на выкодс сумматора по модулю два 22.

bО а!

Из таблицы следует, что be=1 при 6а )О и b. =-О при 6а, (О. Сигнал с выхода сумматора по модулю два 22 устанавливает триггер знака 24 через ячейку «И» 28, управляемую импульсом опроса. При b" .==1 триггер знака 21 открывает ячейку 25, а при b=- =-0 открывает ячейку 2б. Таким образом, при т)0 пачка из 6 импульсов с ячейки 25 проходит на вход сложения узла усреднения 4, а прп т - О— через ячейку 2б на вход вычитания.

П р сдм ет изобретен и я

ij5 Регенератор двоичных символов, содержащий опорный генератор, делитель частоты, 10 устройство управления коэффициентом деления, узел усреднения, фазовый дискриминатор и счетчик интегратора, orëичпюtuuйся тем, что, с целью повышения точности,восстановления символов при наличии дроблений принимаемых посылок, фазовый дискриминатор выполнен в виде счетчика разности, вход которого соединен с двумя ячейками совпадения, подключенными к двум потенциальным выходам делителя частоты и выходу опорного генератора, а параллельные выходы счетчика разности подключены через ячейки опроса, соединенные с импульсным выходом делителя частоты, к преобразователю двоичного кода в числоимllóëüñíûé код, выход которого соединен со входамп сложения и вычитания узла усреднения через две ячейки коммутации, соединенные с выходами триггера знака, при этом выход единиц старшего разряда счетчика интегратора и выход нулей старшего разряда счетчика разности подключены через сумматор по модулю два и ячейку опроса к раздельному входу триггера знака.

Составитель В. Валюженич

Редактор E. В. Семакова Текред Л. В. Куклина Корректор А. П, Васильева

Заказ 4980 Тираж 480 Подписное

ЦI!!111ПИ Комитета по делам изобретений и огкрытий прп Совете Министров СССР

Москва, iK,-35, Ралпская пао., д. 4, ;>

Загорская типография